4 DDR5 SDRAM命令描述和操作-38

4.38 Loopback

通过回环测试,DDR5可以将接收到的信号或数据反馈给外部接收器,用于多种目的。回环测试允许主机(内存控制器或测试仪器)监视刚刚发送到DRAM的数据,而无需将数据存储在DRAM中或使用读操作来检索发送到DRAM的数据。DDR5 DRAM中的回环测试要求在将数据发送到核心之前将其发送到回环路径,因此不需要读/写命令即可使回环测试正常工作。使用统计分析方法(如误码率(BER)分析)对接收器进行表征时也存在固有的限制。例如,在BER=1E-16时,(1) DRAM中没有足够的内存深度来存储所有的1E+16数据;(2) 执行多个写入/读取命令到/从内存所需的时间过长;(3) 由于执行这些操作所需的时间远远超过DRAM刷新速率间隔,主机或内存控制器还必须在测试期间管理刷新操作以确保数据保留;(4) 有限的模式深度意味着有限的符号间干扰(ISI)和有限的随机抖动(Rj),从而在接收器上产生有限的错误。使用回环测试功能是对接收器进行表征的必要手段,而无需受到其他传统验证方法的限制和复杂性。回环测试还可以在“正常”运行期间使用,例如在训练和加载操作系统时。

4.38.1 Loopback输出定义

Loopback需要两个输出引脚(一个单端Loopback strobe LBDQS和一个单端Loopback数据LBDQ)。Loopback引脚的引脚分配位置定义为LBDQS的A9和LBDQ的A1。

Loopback的默认RTT状态为RTT_OFF,由MR36:OP[2:0] = 000B指定。在这个状态下,LBDQS和LBDQ输出都被禁用。如果将多个DDR5 SDRAM设备的Loopback引脚连接在一起,并且“末端”设备需要终端电阻,则可以通过设置MR36:OP[2:0] = 101B选择RZQ/5(48欧姆)选项。

选择Loopback Select Phase A(MR53:OP[6:5] = 00B)和通过MR53:OP[4:0]选择除默认值Loopback Disabled(MR53:OP[4:0] = 00000B)之外的输出值,将使LBDQS和LBDQ引脚从RTT_OFF状态转换为DRAM驱动状态。

在将Loopback Output Select从高字节更改为低字节或反之前,主机应将Loopback Output Select设置为MR53:OP[4:0] = 00000B,以使Loopback模式被禁用。

对于x4和x8设备配置,LBDQS输出将随着DQS_t/DQS_c的差分输入交叉点以及延迟进行转换。如果选择了DML或DQL作为输出,则LBDQS将随着x16设备的DQSL_t/DQSL_c进行转换,如果选择了DMU或DQU作为输出,则LBDQS将随着x16设备的DQSU_t/DQSU_c进行转换。如果选择了RFU输出,或者在x4或x8设备上选择了DMU或DQU,而DQSU_t/DQSU_c无效,LBDQS将保持在DRAM驱动状态。

LBDQ输出将随着由MR53:OP[4:0]选择的DM或DQ引脚的接收器数据状态进行转换。如果选择了RFU输出,或者选择了设备配置的无效输出,则LBDQ输出将保持在DRAM驱动状态。

4.38.2 Loopback相位

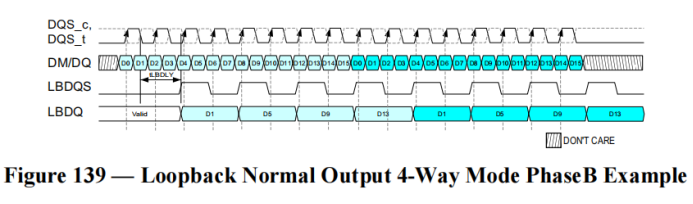

由于DDR5 SDRAM的高数据速率,Loopback可以使用2路或4路交错输出来实现。在2路实现中,DQS和选择的DM/DQ将每1个CK或2个UI进行采样和输出。类似地,在4路实现中,DQS和选择的DM/DQ将每2个CK或4个UI进行采样和输出。

为了能够通过2路或4路交错实现对所有位进行采样,MR53:OP[6:5]中编程的Loopback Select Phase允许选择要输出的DQS/DM/DQ相位。在2路模式下,Phase A和Phase B是有效选项。

在4路模式下,Phase A、Phase B、Phase C和Phase D是有效选项。

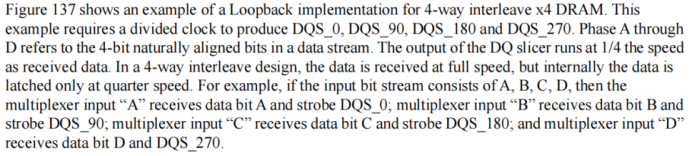

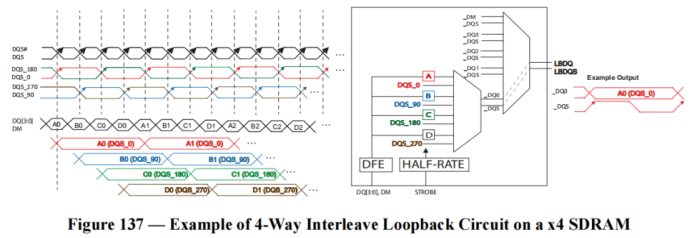

图137显示了4路交错x4 DRAM的Loopback实现示例。这个示例需要一个分频时钟来产生DQS_0、DQS_90、DQS_180和DQS_270。Phase A到D指的是数据流中4位自然对齐的位。DQ分选器的输出速度是接收到的数据的1/4。在4路交错设计中,数据以全速接收,但在内部只以四分之一的速度锁存数据。例如,如果输入位流由A、B、C、D组成,则多路复用器输入“A”接收数据位A和时钟DQS_0;多路复用器输入“B”接收数据位B和时钟DQS_90;多路复用器输入“C”接收数据位C和时钟DQS_180;多路复用器输入“D”接收数据位D和时钟DQS_270。

4.38.3 Loopback输出模式

Loopback输出模式基于MR53:OP[7]来选择是否以正常输出模式或写入突发输出模式输出LBDQS和LBDQ。在默认的正常输出模式下(MR53:OP[7] = 0B),所选的DM/DQ状态将在所选的Loopback相位的每次DQS_t/DQS_c切换时被捕获。在写入突发输出模式下(MR53:OP[7] = 1B),只有在写使能符合条件时,所选的DM/DQ状态才会在LBDQ上输出,这意味着数据仅在写入突发期间捕获,而不在前导码或尾码期间捕获。

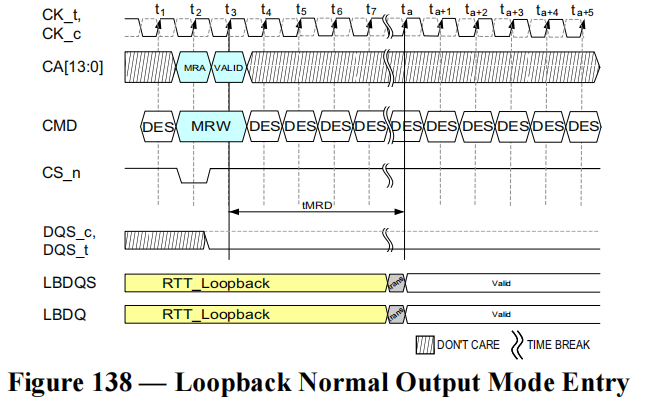

4.38.3.1 Loopback正常输出模式(默认)

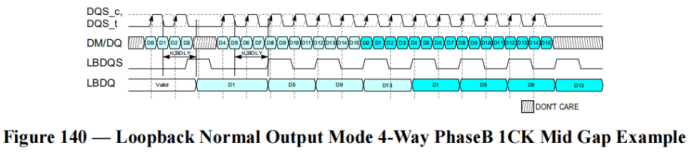

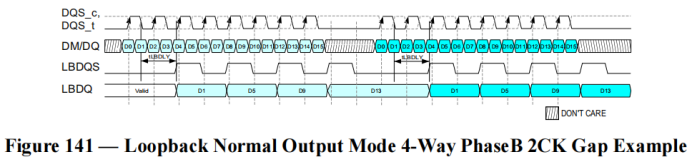

在正常输出模式下(MR53:OP[7] = 0B),所选的DM/DQ状态将在所选的Loopback相位的每次DQS_t/DQS_c切换时被捕获并输出到LBDQ。LBDQS输出将延迟tLBDLY与所选的DQS_t/DQS_c Loopback相位之间。相位C和相位D分别与相位A和相位B反相。由于在正常输出模式下不需要写命令,因此与Loopback功能相关的MR设置(如前导码、尾码、CWL)将被忽略。

正常输出模式的附加要求:

• 在使用内部写入时序模式设置MR2:OP[7]=1完成写入平衡训练后,不支持正常输出模式的Loopback。

• 在进入正常输出模式之前,必须差分驱动DQS(DQS_t低电平,DQS_c高电平)。

• 在Loopback操作期间,必须持续驱动DQS_t/DQS_c。不允许处于高阻态。

• 在正常输出模式期间,仅允许在命令引脚上使用DSEL和MRW命令。

• 退出Loopback正常输出模式需要进行复位(RESET)。

在DQS_t的第一个上升沿后,不假定进行DFE复位。进入正常输出模式后,DDR5 SDRAM阵列数据无法保证。

4.38.3.2 Loopback正常输出模式时序图

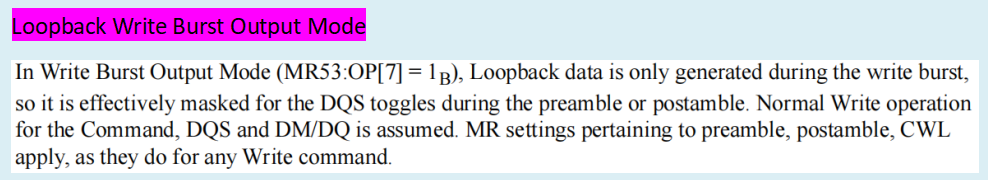

4.38.3.3 Loopback写突发输出模式

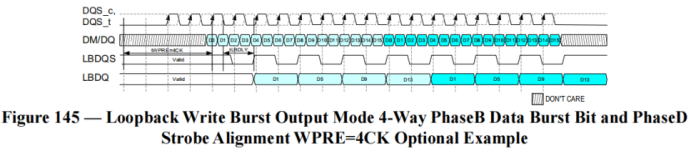

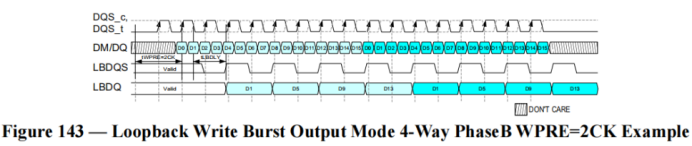

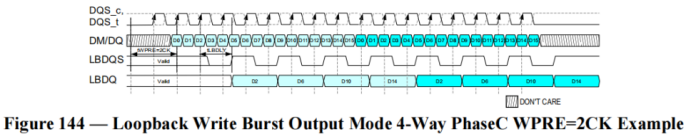

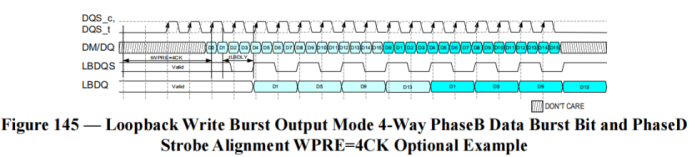

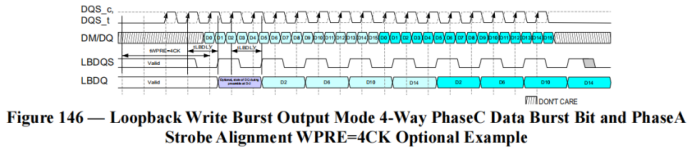

在写入突发输出模式下(MR53:OP[7] = 1B),Loopback数据仅在写入突发期间生成,因此在前导码或尾码期间,对于DQS的切换,它实际上被屏蔽了。假设使用正常的写入操作进行命令、DQS和DM/DQ。与任何写入命令一样,与前导码、尾码、CWL相关的MR设置也适用。

为了防止在正常数据路径中对DRAM的Loopback干扰,DRAM可以选择在特殊情况下输出第二个前导脉冲,即WPRE=4CK且选择相位C或D进行数据突发位相对齐,或选择相位A或B进行时钟相位对齐。在这种情况下,所有相位与正常行为相反。

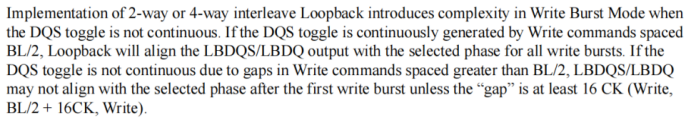

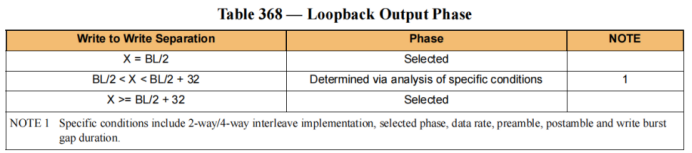

实现2路或4路交错Loopback时,在DQS切换不连续的写入突发模式下会引入复杂性。如果由间隔为BL/2的写入命令持续生成DQS切换,Loopback将使LBDQS/LBDQ输出与所选相位在所有写入突发期间对齐。如果由于大于BL/2的写入命令间隔而导致DQS切换不连续,除非“间隔”至少为16 CK(Write, BL/2 + 16CK, Write),否则LBDQS/LBDQ可能不会与所选相位对齐。

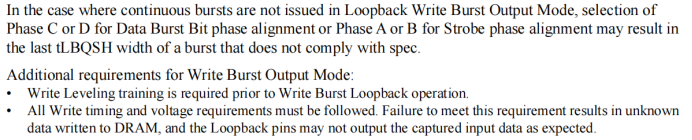

在Loopback写入突发输出模式下,如果不连续发出连续的突发,选择相位C或D进行数据突发位相对齐,或选择相位A或B进行时钟相位对齐可能导致突发的最后tLBQSH宽度不符合规范。

写入突发输出模式的附加要求:

• 在进行写入突发Loopback操作之前,必须进行写入平衡训练。

• 必须遵循所有写入时序和电压要求。不满足此要求将导致未知数据写入DRAM,并且Loopback引脚可能无法按预期输出捕获的输入数据。

4.38.3.4 Loopback写突发输出模式时序图

4.38.4 Loopback时序和电平

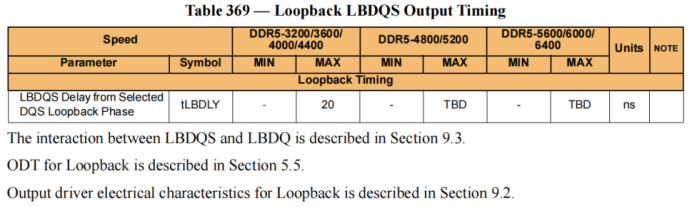

LBDQS和LBDQ之间的交互作用在第9.3节中进行了描述。

Loopback的ODT设置在第5.5节中进行了描述。

Loopback的输出驱动器电气特性在第9.2节中进行了描述。

本文详细解释了DDR5SDRAM的Loopback功能,包括其定义、输出模式(正常与写突发)、时序和电平,以及在测试中的应用,强调了回环测试在接收器表征中的重要性及其操作要求。

本文详细解释了DDR5SDRAM的Loopback功能,包括其定义、输出模式(正常与写突发)、时序和电平,以及在测试中的应用,强调了回环测试在接收器表征中的重要性及其操作要求。

562

562

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?