Vivado 软件使用流程

这里用一个分频的例子,完成Vivado工程的全部流程。按照本文流程走完,你对vivodo建立工程有一个基本的认识。

第一步:建立vivodo工程

该步骤很有很多教程就不详细描述了,主要是选择FPGA的型号。

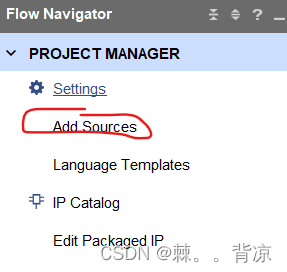

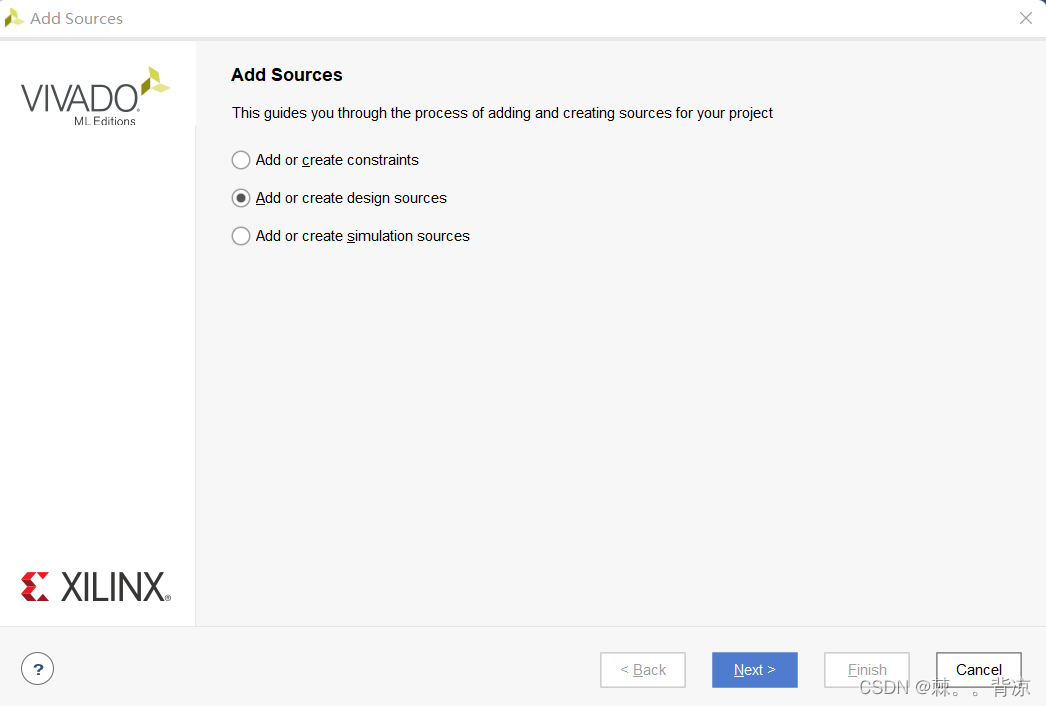

第二步:添加verilog文件

左键点击添加文件,vivodo中能够添加的文件有3种,依次是添加约束文件(时钟约束和引脚定义),源文件(verilog 代码)以及仿真文件

这里先添加verilog文件,取名为:divide_frequency,分频的代码如下:

module divide_frequency#(

DIVIDE=10

)(

input rst,

input sys_clk,

input sen,

output divide_clk

);

reg[31:0] cnt;

reg clk;

assign divide_clk=clk;

always@(posedge sys_clk or posedge rst)

begin

if(rst | ~sen)

begin

cnt<=32'd0;

clk<=1'd0;

end

else

begin

if(cnt>=DIVIDE-1'd1)

begin

cnt<=32'd0;

clk<=~clk;

end

else

cnt<=cnt+1'd1;

end

end

endmodule

使用同样的办法添加仿真文件,如下:

module sim_top(

);

reg rst;

reg sys_clk;

reg sen;

wire divide_clk;

initial

begin

rst=0;

sys_clk=0;

sen=0;

#20

rst=1;

#20

rst=0;

#50

sen=1;

end

always #1 sys_clk=~sys_clk;

divide_frequency #(

.DIVIDE(10)

)di(

.rst(rst),

.sys_clk(sys_clk),

.sen(sen),

.divide_clk(divide_clk)

);

endmodule

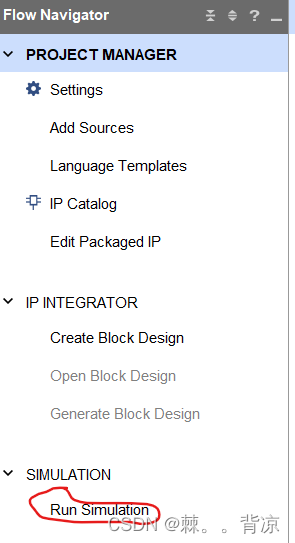

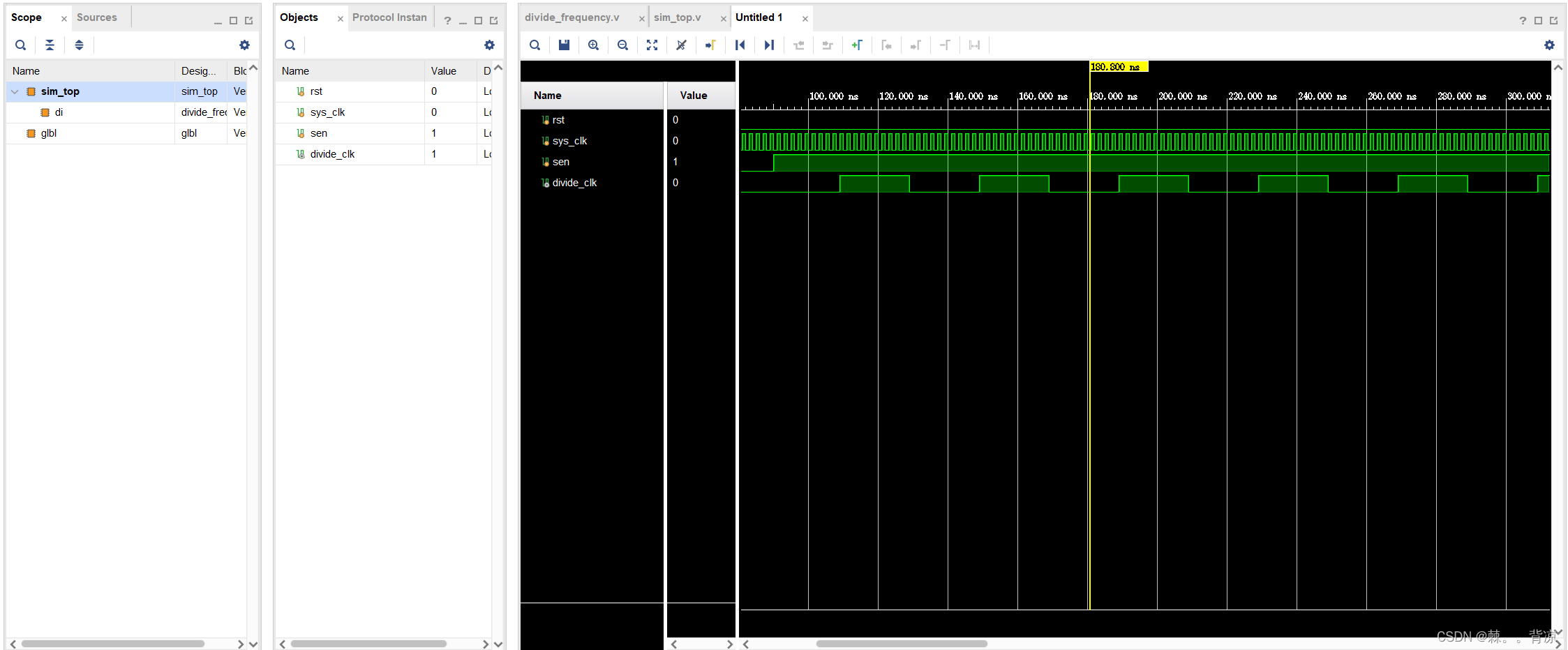

第三步:行为级仿真

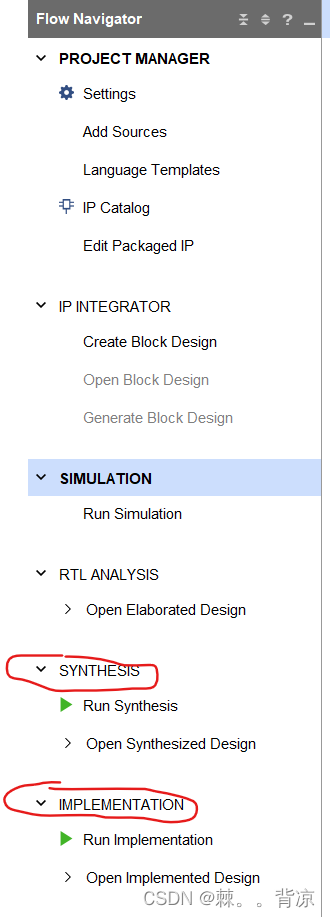

仿真代码和verilog代码写完了,就可以进行仿真了,左键点击流程导航里的Run Simulation

然后点击Run Behavioral Simulation,进行行为仿真。

第四步、综合与实现

在运行综合与实现之前可以RTL分析一下。

先运行综合,

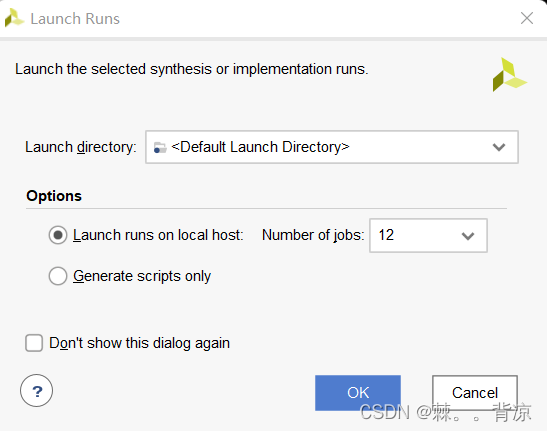

这里有一个Number of jobs 与自己电脑性能有关。

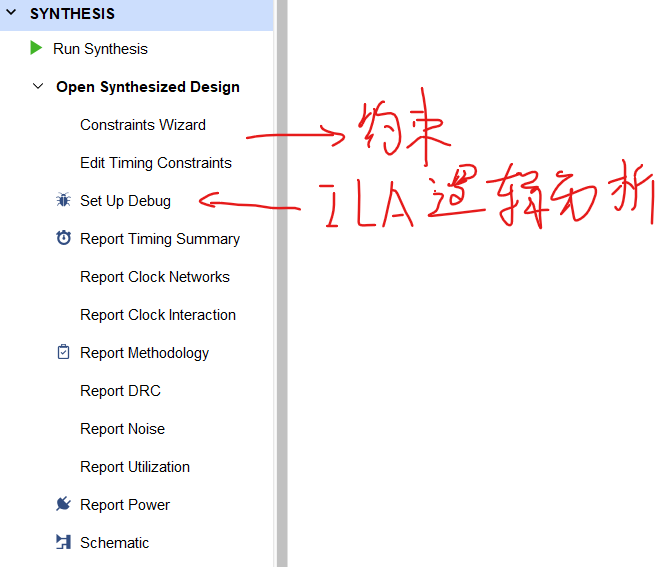

运行完成后如下,可以设置ILA逻辑分析和时钟约束,这里就不扩展开说了。

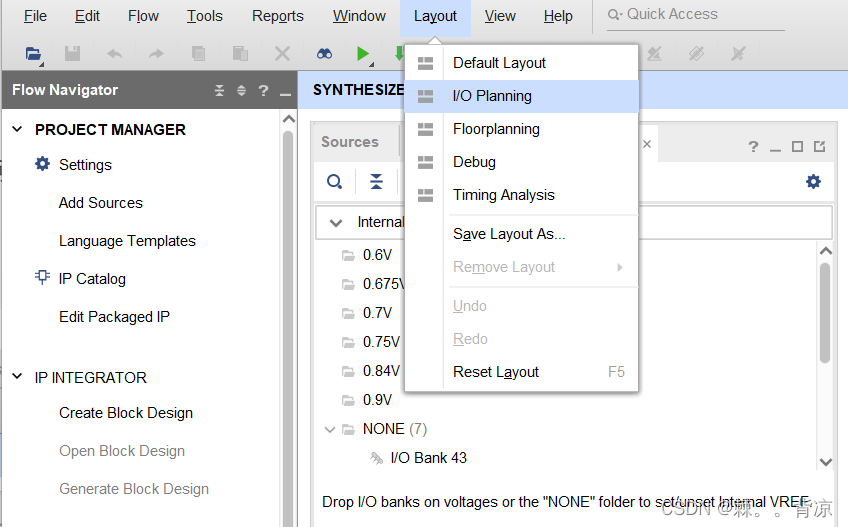

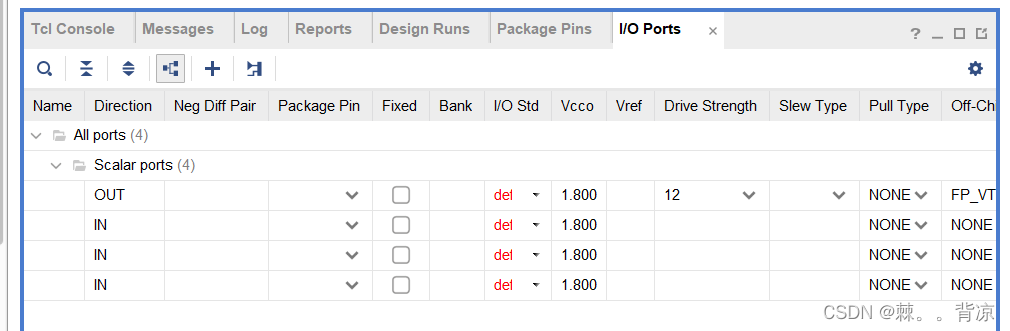

运行完综合后就可以进行引脚约束,可以使用xdc文件直接编写约束,也可以如下图在I/O Planning里手动进行约束。

当然,这里就不设置约束了。

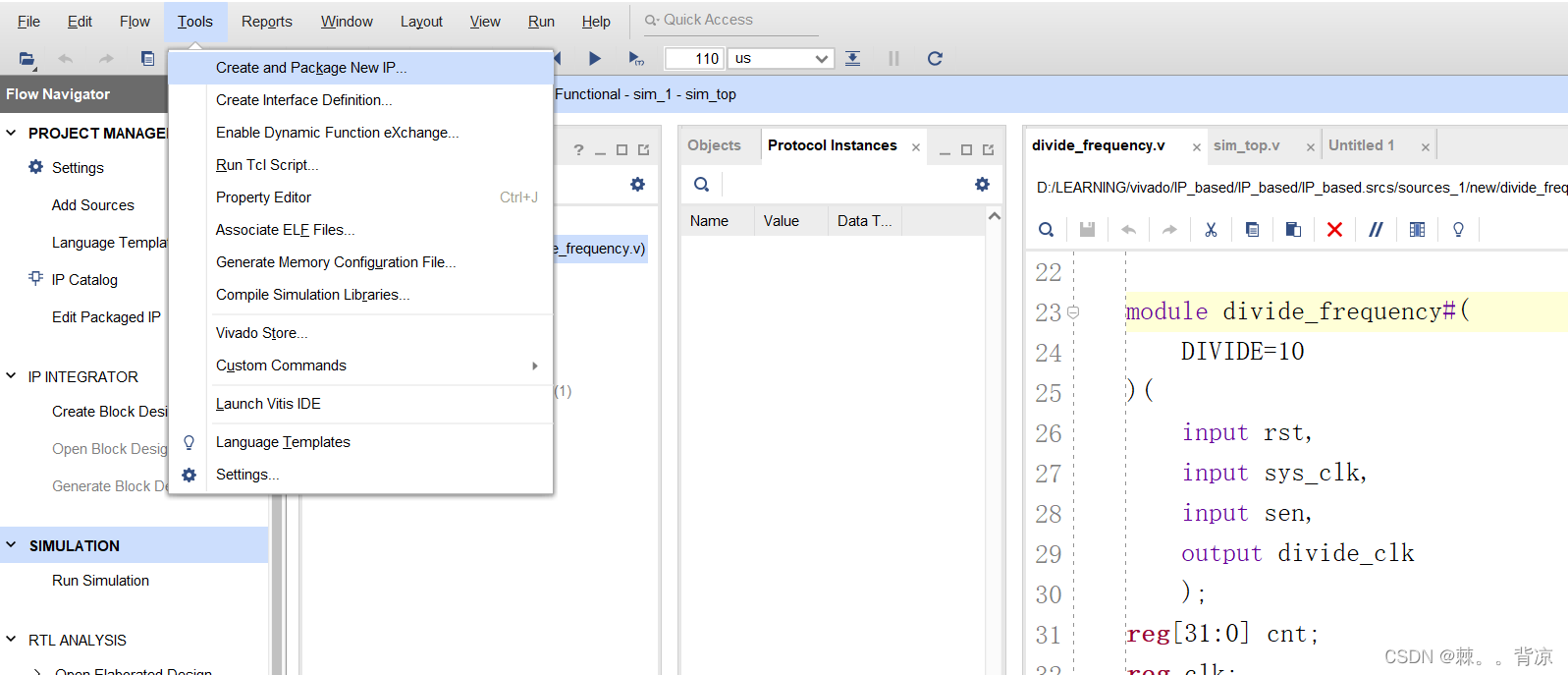

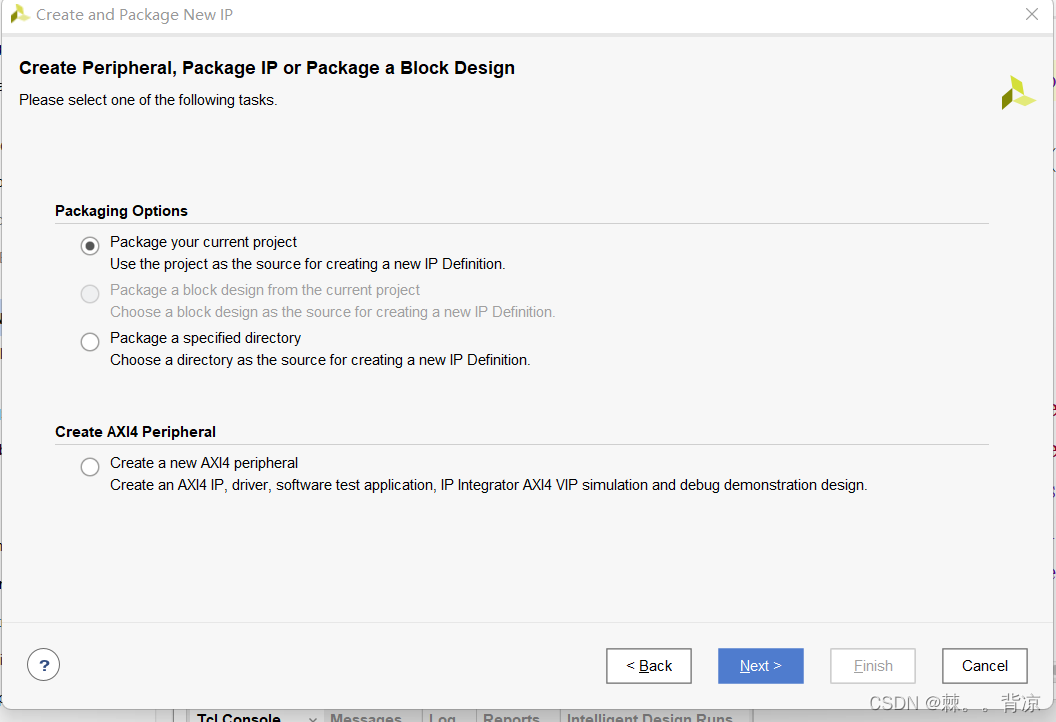

第五步,自定义IP

当你运行完成综合和实现后发现没啥大问题。可以将整个工程打包成一个IP核。

你也可以创建带有AXI4接口的IP核,也很方便。具体流程可以搜一下。

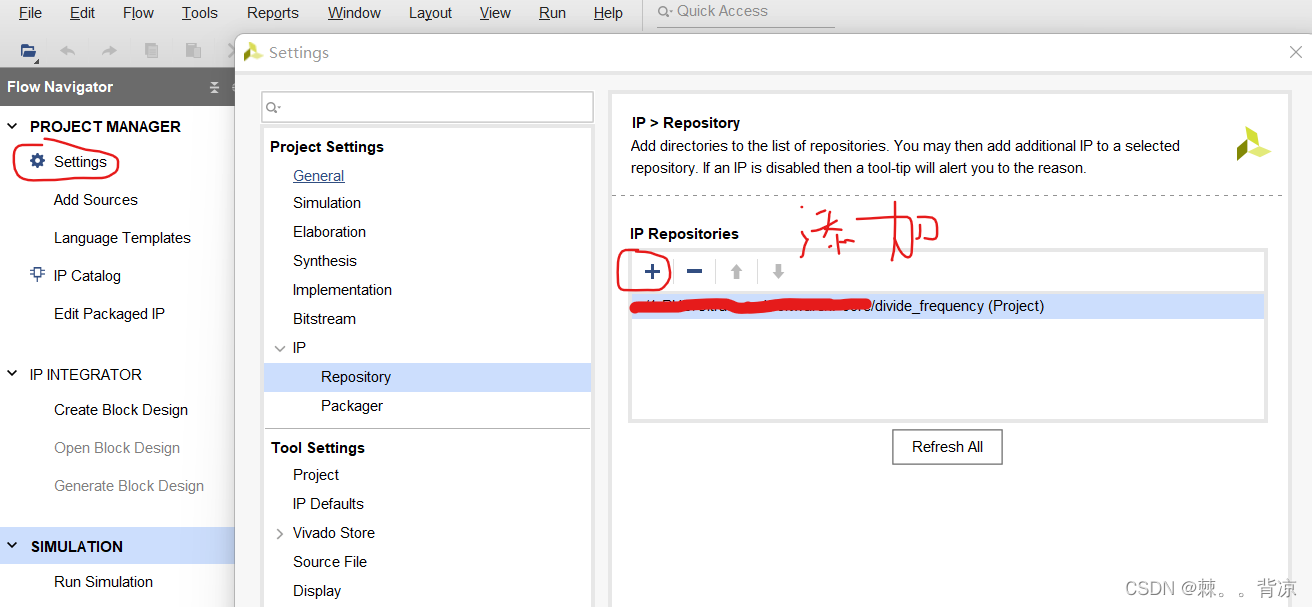

IP核创建完成后,添加IP核到工程里面。这样我们就可以在工程里直接使用IP。

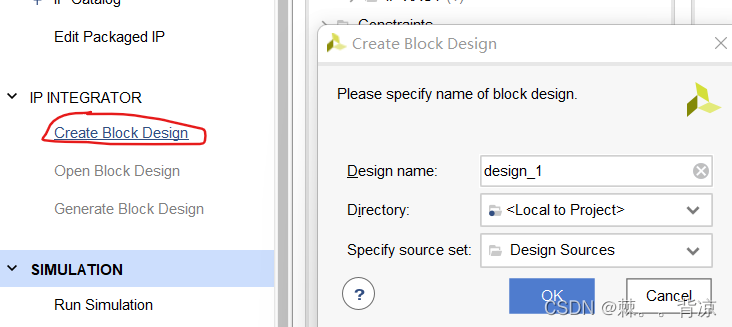

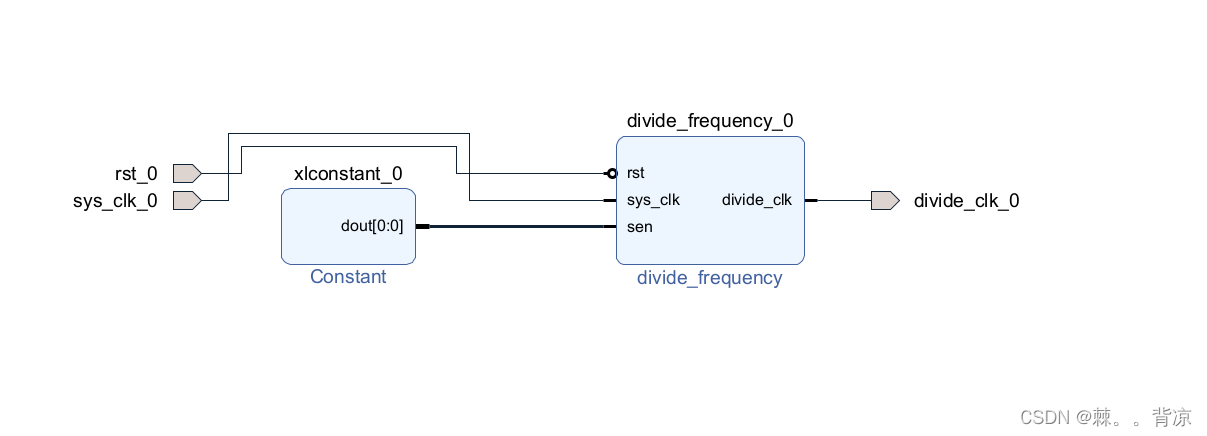

第六步,Block Design的创建

在vivodo中可以使用IP核块,进行图形话的操作,

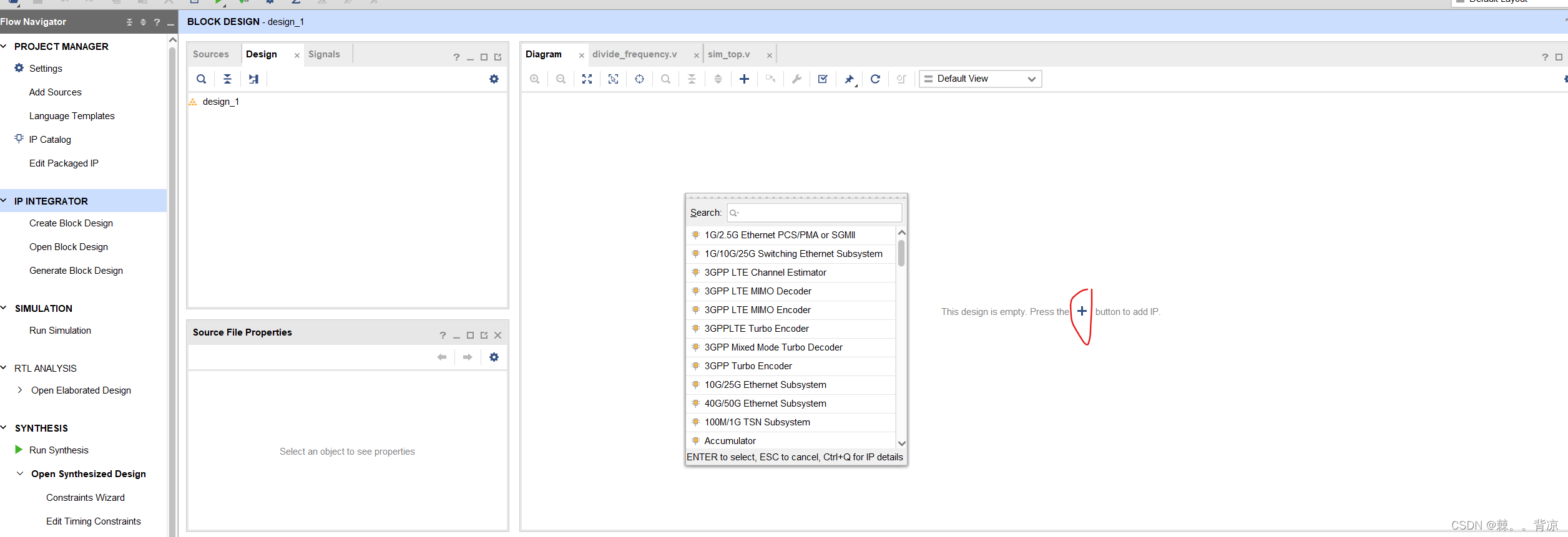

点击添加IP,然后搜索找到自定义的IP核,添加进来。

xilinx官方提供很多IP核,比如原语BUFFER的IP核 Utility Buffer,与或非逻辑IP核 Utility Vector Logic。还有生成MMCM和PLL时钟的clocking wizard,生成FIFO的IP核,等等。

这里不做复杂的设计。

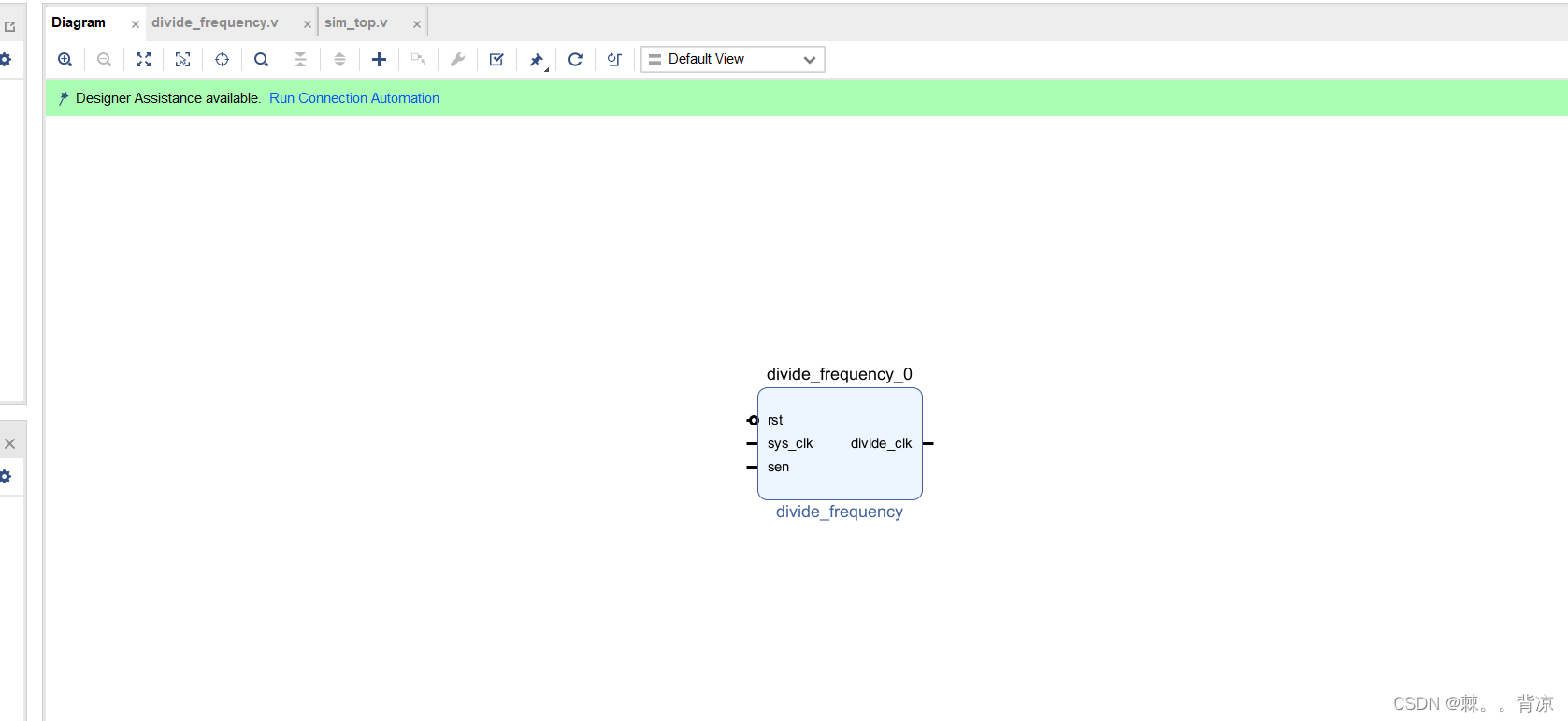

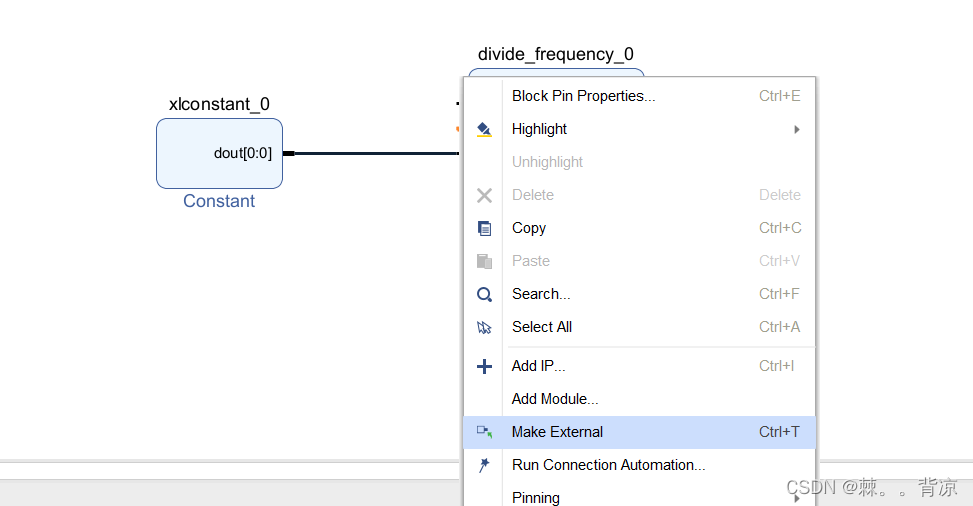

我们使用常数IP核, Constant生成一个高信号给信号sen,然后将其他引脚都接出来。

选中引脚,右键选择make external可以将引脚引出。

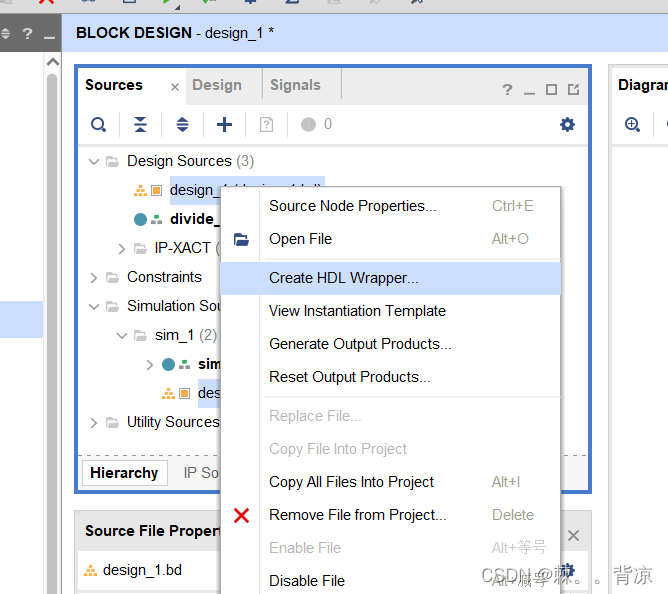

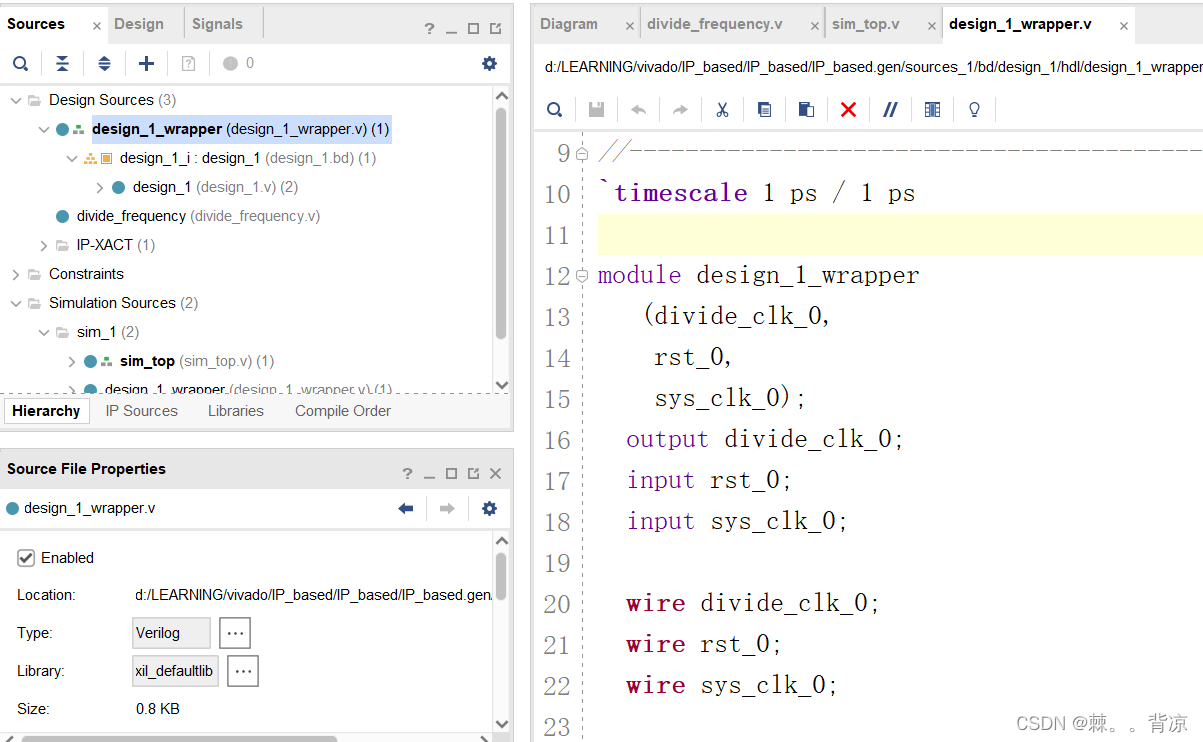

在source窗口,可以看到我们创建的BD文件,点击create HDL Wrapper 对其进行verilog代码包裹。实际上就是将其引脚用verilog代码引出方便我们使用。

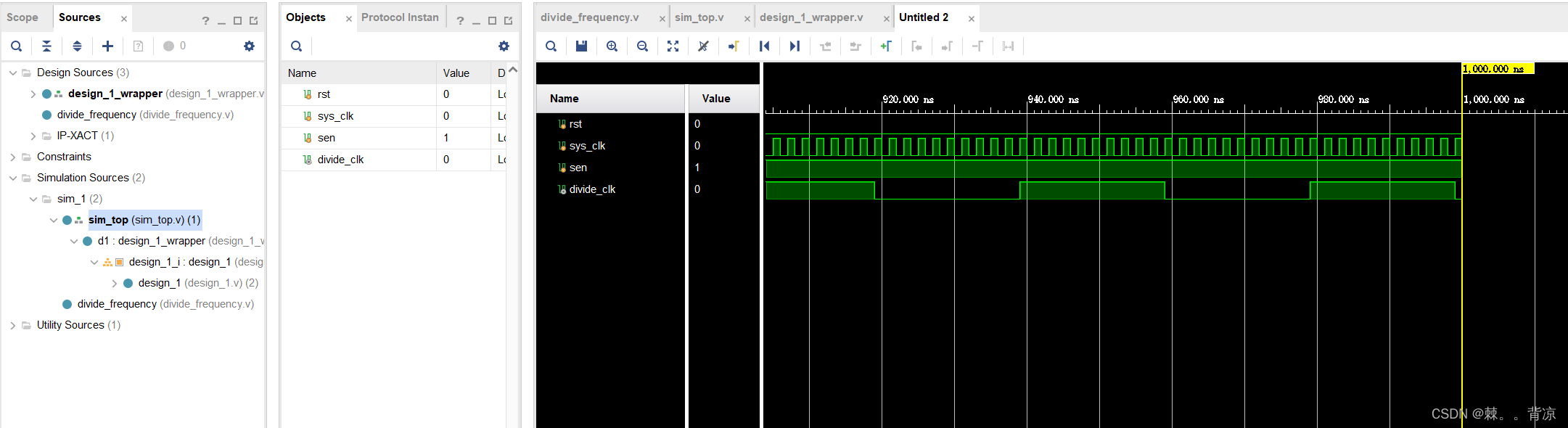

这里可以看出BD文件实际使用就是和IP核使用的方法一下,我们稍微修改一下仿真文件,就能对它进行仿真。

修改的仿真文件如下:

module sim_top(

);

reg rst;

reg sys_clk;

reg sen;

wire divide_clk;

initial

begin

rst=0;

sys_clk=0;

sen=0;

#20

rst=1;

#20

rst=0;

#50

sen=1;

end

always #1 sys_clk=~sys_clk;

//divide_frequency #(

// .DIVIDE(10)

//)di(

// .rst(rst),

// .sys_clk(sys_clk),

// .sen(sen),

// .divide_clk(divide_clk)

// );

design_1_wrapper d1

(.divide_clk_0(divide_clk),

.rst_0(rst),

.sys_clk_0(sys_clk));

endmodule

vivado确实是十分强大,这样就大大简化了开发流程。

705

705

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?