第2章 层次建模的概念

设计方法学&自底向上和自顶向下设计方法&Verilog模块和实例的区别&4中抽象角度&激励块和功能块

2.1设计方法学

- 一般两种混用。设计人员自顶向下将整个设计分解为由库单元构成的结构描述,电路设计者同时自底向上创建一个底层功能块库。

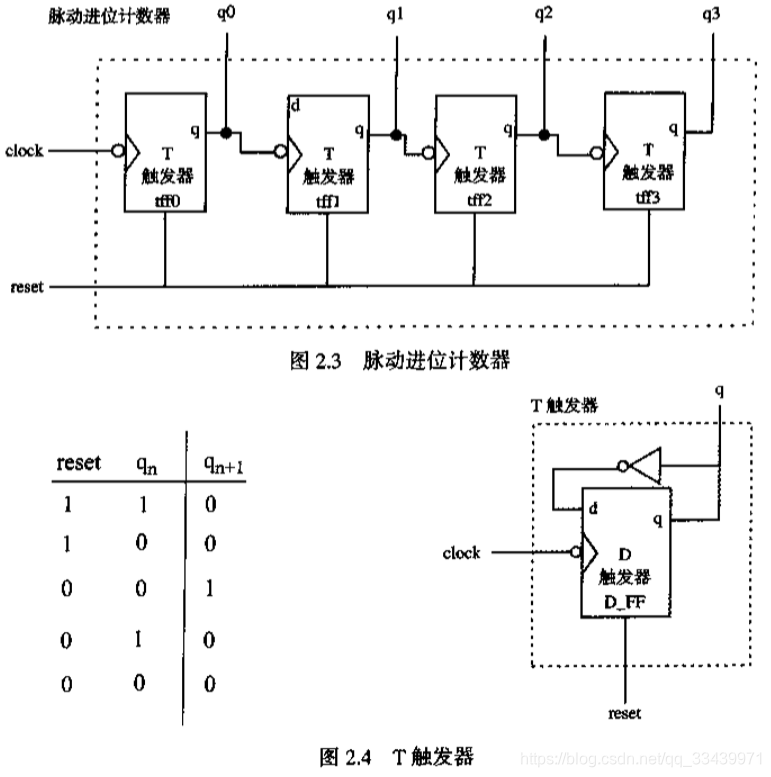

- 下降沿触发的T触发器构成的脉动进位计数器(Clk 0->1时,T触发器的Q跳变)

- 自顶向下:说明功能,用T触发器搭建顶层模块;再用D触发器和反相器实现T触发器

- 自底向上:先搭建D触发器

2.3模块module

- Verilog用元件构建在设计中多个地方使用的功能块。

- 模块:元件/低层模块的组合。通过接口(IO)被高层模块调用,但隐藏内部实现细节。

- 模块端口列表描述输入输出端口,模块名惟一地识别模块。↓

module <模块名>(<模块端口列表>);

…

<模块的内容>

…

endmodule

- 实例 下降沿触发的T触发器

module T_FF (q, clock, reset);

…

<T触发器功能描述>

…

endmodule

- Verilog可进行行为描述/结构描述,允许在一个模块中混合使用多个抽象层次。

- 模块内部可以对以下4个抽象层次描述(对外界透明):

- 行为或算法级:Verilog支持的最高抽象层次。只关注其实现的算法,不关注硬件实现细节。

- 数据流级:说明数据流程。关注数据在各个寄存器间的流动&如何处理数据。

- 门级:组成电路的逻辑门及其互连关系。类似于门级逻辑简图。

- 开关级:Verilog支持的最低抽象层次。开关、存储节点及其互连关系。关注开关级实现细节。

- RTL(寄存器传输级)面搜狐:能被逻辑综合工具接受的行为及和数据流级混合描述。

- 抽象层次越高,设计灵活性和工艺无关性越强。

2.4模块实例

- 实例化:从模板创建对象的过程。该对象为实例。

- Verilog中,不允许在模块什么中嵌套模块。即module和endmodule中不含模块声明。

- 用实例引用来相互调用。!模块调用必须通过实例化。

- 实例 下降沿触发的脉动进位计数器 的设计块↓。创建4个实例,每个T触发器实例化1个D触发器和1个反相器。

// 定义 ripple_carry_counter(脉动进位计数器)模块;

//引用4个T触发器

module ripple_carry_counter (q, clk, reset);

output [3:0] q; //输入输出端口的信号和向量声明

input clk, reset;

//生成了4个T触发器T_FF的实例

//每个实例都是T_FF模块的副本。有名字,且传递一组信号

T_FF tff0 (q[0], clk, reset);

T_FF tff1 (q[1], q[0], reset);

T_FF tff2 (q[2], q[1], reset);

T_FF tff3 (q[3], q[2], reset);

endmodule

//定义名为T_FF的T触发器的模块,引用了一个D触发器D_FF

module T_FF (q, clk, reset);

output q;

input clk, reset;

wire d;

D_FF dff0 (q, d, clk, reset); //调用D_FF,取名dff0

not n1 (d, q); //非门not(是Verilog内部源语部件primitive)

endmodule

// 定义带异步复位的D触发器(D_FF)

module D_FF (q, d, clk, reset);

output q;

input d, clk, reset;

reg q;

always @(posedge reset or negedge clk)

if (reset)

q <= 1'b0;

else

q <= d;

endmodule

2.5逻辑仿真的构成

- 激励块/测试台:完成测试功能的块。对设计模块施加激励,检测器输出正确性。

- 激励块的两种设计模式:①图2.6 在激励块中调用并直接驱动设计块;②图2.7 在一个虚拟的顶层模块中调用激励块和设计块,二者通过接口交互。

- 应将激励块和设计块分开设计。

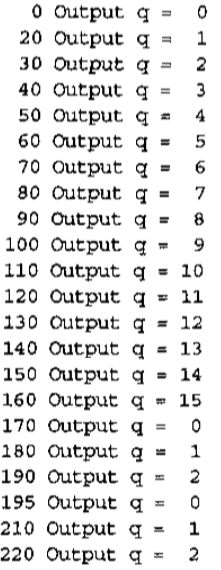

- 实例 下降沿触发的脉动进位计数器 的激励块↓ (接2.4中的设计块)。检查计数器功能&复位机制。

// 定义 ripple_carry_counter(脉动进位计数器)模块;

module stimulus ;

reg clk ;

reg reset ;

wire [3:0] q ;

ripple_carry_counter r1 (q, clk, reset); // 引用模块实例

// 控制时钟信号,时钟周期为10个时间单位

initial

clk = 1'b0 ; // clk置零

always

#5 clk = ~clk ; // 每5个时间单位时钟翻转一次

// 控制reset信号 0~15 = 1; 195~205 = 1; 其余为0

initial

begin

reset = 1'b1 ;

#15 reset = 1'b0 ;

#180 reset = 1'b1 ;

#10 reset = 1'b0 ;

#20 $finish ; // 终止仿真

end

// 监视输出

initial

$monitor ($time, " Output q = %d", q) ;

endmodule

- 测试信号

- 仿真测试输出结果:

1583

1583

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?