8. DRAM Device Organization: Basic Circuits and Architecture

在本章中,将描述DRAM设备的基本电路和体系结构。现代DRAM设备是三十多年来演化发展的结果,不可能在单一章节中提供完整的概述和深入的电路和各种DRAM设备的体系结构。本章的有限目标是提供现代DRAM设备中常见的电路和功能块的广泛概述,然后在后续章节中继续描述由本章中描述的常见电路和功能块组成的DRAM设备的更大内存系统。

本章通过首先提供对快页模式(FPM)DRAM设备的粗略概述,然后深入研究现代DRAM设备的基本构建模块,继续进行。在本章中,将研究诸如DRAM存储单元、DRAM阵列结构、电压感应放大器、译码器、控制逻辑块、数据输入/输出结构和封装考虑等基本构建模块。具体的DRAM设备,如SDRAM、DDR SDRAM和D-RDRAM设备,以及DRAM设备的一般演化将在第12章中进行详细讨论。

8.1 DRAM Device Organization

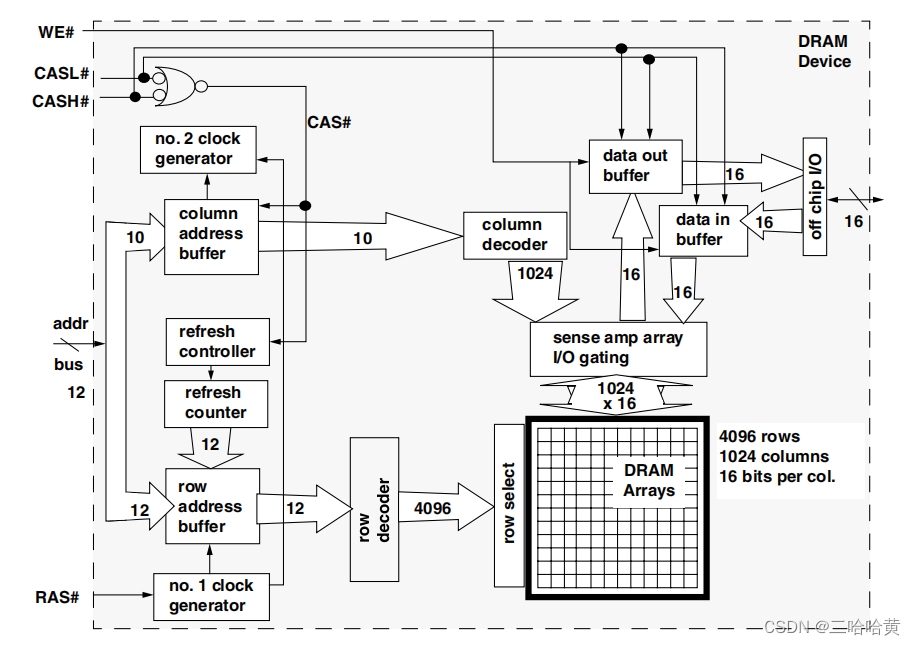

图8.1展示了在1980年代和1990年代早期广泛使用的FPM DRAM设备的组织和结构。在图8.1中,FPM DRAM设备内部的DRAM存储单元被组织为4096行,每行1024列,每列有16位数据。在该设备中,每次进行行访问时,会在地址总线上放置一个12位地址,并由外部内存控制器激活行地址 strobe (RAS)。在DRAM设备内部,地址总线上的地址会被行地址缓冲器缓存,然后发送到行解码器。行地址解码器接受12位地址,然后选择4096行存储单元中的一行。所选行中的数据值随后由感应放大器阵列读取并保持活动状态。在图8.1中所示的DRAM设备中,每一行的DRAM单元由1024列组成,每列有16位。也就是说,16位宽的列是该设备中的基本可寻址内存单元,并且在行访问之后的每次列访问都会从同一行的DRAM中读取或写入16位数据。

图8.1中所示的FPM DRAM设备允许通过使用单独的列访问 strobe high (CASH) 和列访问 strobe low (CASL) 信号来独立访问16位列中的每个8位半部分。然而,由于数据总线宽度为16位,因此该设备中的数据列宽度为16位而不是8位。类似地,现代DRAM设备使用数据屏蔽信号来实现在单个列内进行部分数据写入操作。一些其他的DRAM设备,如XDR设备,使用复杂的命令编码来控制子列读取和写入操作。

在图8.1中所示的FPM DRAM设备中,列访问命令的处理方式与行访问命令类似。对于列访问命令,内存控制器会在地址总线上放置一个10位地址,然后激活适当的列访问 strobe (CAS#) 信号。在内部,DRAM芯片接收这个10位的列地址,解码它,并从1024列中选择1列。然后,根据普通的列读取命令,DRAM设备将该列的数据放置在数据总线上,或者根据写使能 (WE) 信号,用来自内存控制器的数据覆盖它,具体情况取决于写使能信号的状态。

所有DRAM设备,从备受推崇的FPM DRAM设备到现代的DDR SDRAM设备,再到高速的XDR DRAM设备、低延迟的RLDRAM设备和低功耗的MobileRAM设备,都共享一些基本的电路和功能模块。在许多情况下,同一DRAM设备制造商的不同类型的DRAM设备共享相同的存储单元和相同的阵列结构。例如,所有DRAM设备中的DRAM单元都被组织成一个或多个阵列,每个阵列都按照一定的行和列排列。所有DRAM设备还具有一些逻辑电路,用于控制设备操作的时序和顺序。图8.1中显示的FPM DRAM设备具有内部时钟生成器以及内置的刷新控制器。FPM DRAM设备保留下一个需要刷新的行的地址,因此当发出刷新命令时,可以从内部刷新计数器加载要刷新的行地址,而不必从芯片外部的地址总线加载。在DRAM设备中包含刷新计数器可以使内存控制器免于跟踪刷新周期中的行地址。

高级DRAM设备,如ESDRAM、Direct RDRAM和RLDRAM,已经发展,包括比本章中所述的基本DRAM设备更多的芯片上逻辑电路和功能。例如,在FPM DRAM设备中只有一个DRAM阵列,而现代DRAM设备具有多个DRAM阵列的存储区(bank),一些DRAM设备还具有额外的行缓存或写缓冲,允许进行读写绕过(read-around-write)操作。本章的讨论仅限于基本电路和体系结构,通常不在标准DRAM设备上找到的高级性能增强逻辑电路将在有关具体DRAM设备和内存系统的讨论中单独描述。

254

254

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?