FPGA使用sv生成虚拟单音数据

之前一直使用matlab生成虚拟的数据,导出到txt或是coe文件中,再导入到fpga中进行仿真测试。

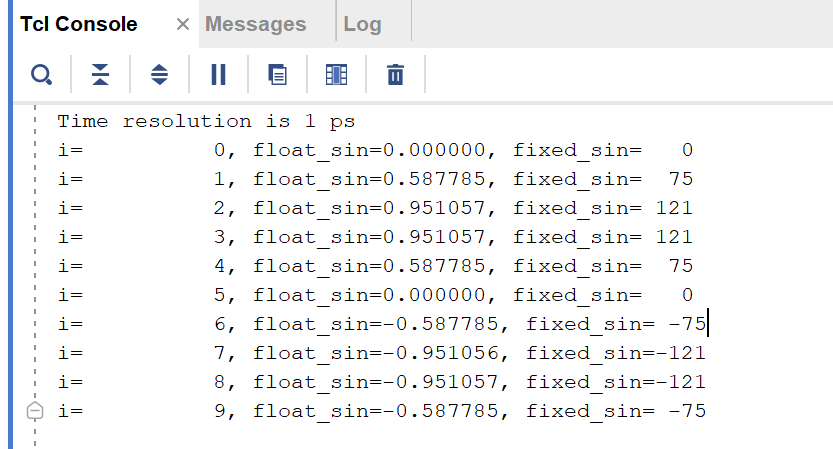

复杂的数据这样操作自然是必要的,但是平日使用正弦数据进行测试的话,这样的操作不免复杂,今日尝试使用systemverilog虚拟单音数据,并存入到txt文件。

module top_tb(

);

localparam FRACTIONAL_BITS = 7; // 7位小数,1位符号

localparam SCALE = 1<<FRACTIONAL_BITS;

logic signed [7:0] fixed_sin[0:9];

real float_sin;

int file;

initial

begin

// 生成正弦数据

for (int i = 0;i<10;i++)

begin

float_sin = $sin(2*3.1415926 *i/10);

fixed_sin[i] = $rtoi(float_sin*SCALE);

$display("i=%d, float_sin=%f, fixed_sin=%d",i,float_sin,fixed_sin[i]);

end

// 写入文件

file = $fopen("../../../../fixed_sin.txt","w");

$fdisplay(file,"虚拟生成的正弦数据:");

for (int i = 0;i<10;i++)

begin

$fdisplay(file,"%d",fixed_sin[i]);

end

$fclose(file);

end

endmodule

2230

2230

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?