数字芯片的功耗分为动态功耗和静态功耗两大部分。动态功耗是芯片正常工作时由于信号翻转产生的功耗,而静态功耗是电路在没有翻转时,晶体管中漏电流造成的功耗。

动态功耗

对于CMOS电路来说,动态功耗又分为开关功耗和短路功耗。开关功耗为电路翻转时对负载电容进行充放电导致的功耗; 短路功耗为输入翻转时,由于信号的翻转不是在瞬时完成的,那么在翻转的过程中总有一段时间会导致NMOS和PMOS同时导通,那么相当于在VDD和GND之间形成了短路,瞬间短路电流形成的功耗。

开关功耗

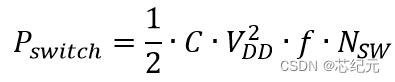

开关功耗可以用如下公式表示:

式中,C为结电容,VDD为供电电压, f为系统时钟频率,Nsw为单周期内翻转晶体管数目。

短路功耗

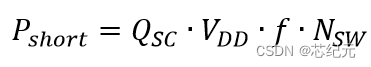

短路功耗可以用如下公式表示:

式中,Qsc为翻转过程中的短路电量,VDD为供电电压,f为系统时钟频率,Nsw为单周期内翻转晶体管数目。

因此,动态功耗可以用如下公式表示:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2842

2842

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?