step

1 建立vivado项目,verilog语言

具体参考

https://blog.csdn.net/leon_zeng0/article/details/78441871

2 项目中增加verilog文件

3 编写.v文件

`timescale 10ns / 1ns

//

// Create Date: 2019/12/25 22:54:05

// Design Name:

// Module Name: RS_FF

//

//RS触发器模块

module RS_FF(Q,Qbar,R,S);

input R,S;

output Q,Qbar;

nand #1(Q,R,Qbar);

nand #1(Qbar,S,Q);

endmodule

//测试模块

module test();

reg tR,tS;

wire tQ,tQbar;

RS_FF T_RS(tQ,tQbar,tR,tS);

initial

begin

tR=0;

tS=0;

#5 tS=1;

#5 tS=0;

tR=1;

#5 tS=1;

tR=0;

#5 tS=0;

#5 tR=1;

end

//输出显示

initial

$monitor("at time %t ,",$time,"tR=%b,tS=%b,tQ=%b,tQbar=%b",tR,tS, tQ,tQbar);

endmodule

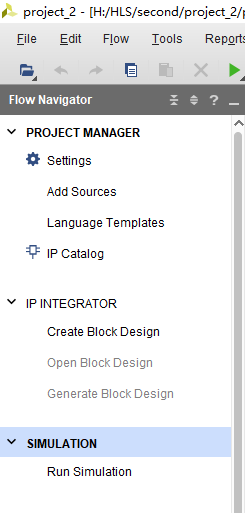

4 运行仿真

5 结果输出

1571

1571

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?