引言

在设计中,很多情况下需要编写很多结构相同但是参数不同的赋值语句或者逻辑语句,如果在参数量很大的的情况下,原本的列举就会显得心有余而力不足。c语言中常用for语句来解决此类问题,verilog则为我们提供了generate语句。

generate语句有generate-for,generate-if,generate-case三种语句。

生成实例可以是以下的一个或多个类型:

(1)模块;(2)用户定义原语;(3)门级语句;(4)连续赋值语句;(5)initial和always块。

用法

- 必须使用genvar声明一个正整数变量,用作for循环的判断变量;

- for循环内部的的语句必须写在begin-end里面;

- begin-and语句快需要一个命名。

generate for

eg

利用generate_for来复制assign语句

尤其是当参数化位宽时,input[NUM-1:0],能够实现assign举例不能完成的功能

module generate_for(

input [7:0] data_in ,

output [1:0] t0 ,

output [1:0] t1 ,

output [1:0] t2 ,

output [1:0] t3

);

wire [1:0] temp [3:0]; //定义位宽为2,深度为4的temp

genvar i; //利用genvar声明正整数变量

generate for(i=0;i<4;i=i+1) //复制模块

begin : gfor //begi_end的名字

assign temp[i] = data_in[2*i+1:2*i];

end

endgenerate

assign t0 = temp[0];//assign temp[0] = data_in[1:0];

assign t1 = temp[1];//assign temp[1] = data_in[3:2];

assign t2 = temp[2];//assign temp[2] = data_in[5:4];

assign t3 = temp[3];//assign temp[3] = data_in[7:6];

endmodule

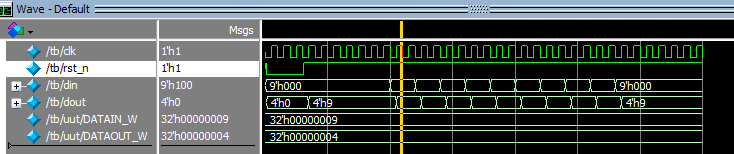

`timescale 1ns/1ps

module tb;

reg [7:0] data_in ;

wire [1:0] t0 ;

wire [1:0] t1 ;

wire [1:0] t2 ;

wire [1:0] t3 ;

initial begin

data_in=8'd0;

#200;

data_in = 8'b1100_0011;

#200;

data_in = 8'b0011_1100;

#300;

end

generate_for generate_inst(

.data_in (data_in ) ,

.t0 (t0 ) ,

.t1 (t1 ) ,

.t2 (t2 ) ,

.t3 (t3 )

);

endmodule

传递的方法:

1、module_name #( parameter1, parameter2) inst_name( port_map);

2、module_name #( .parameter_name(para_value), .parameter_name(para_value)) inst_name (port map);

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?