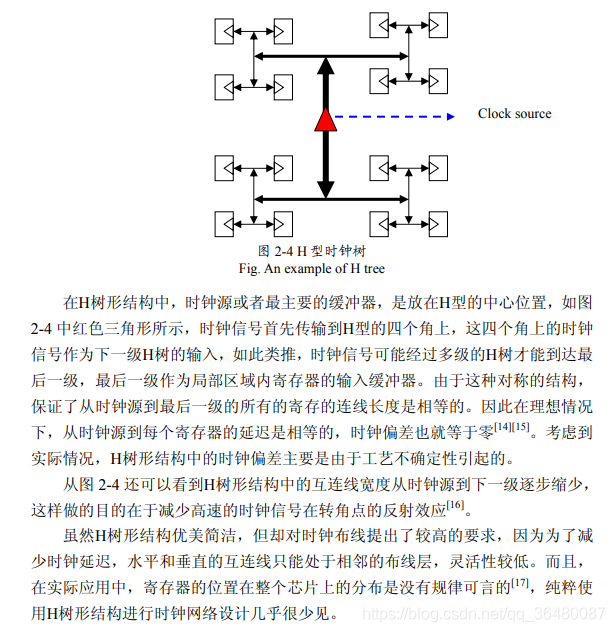

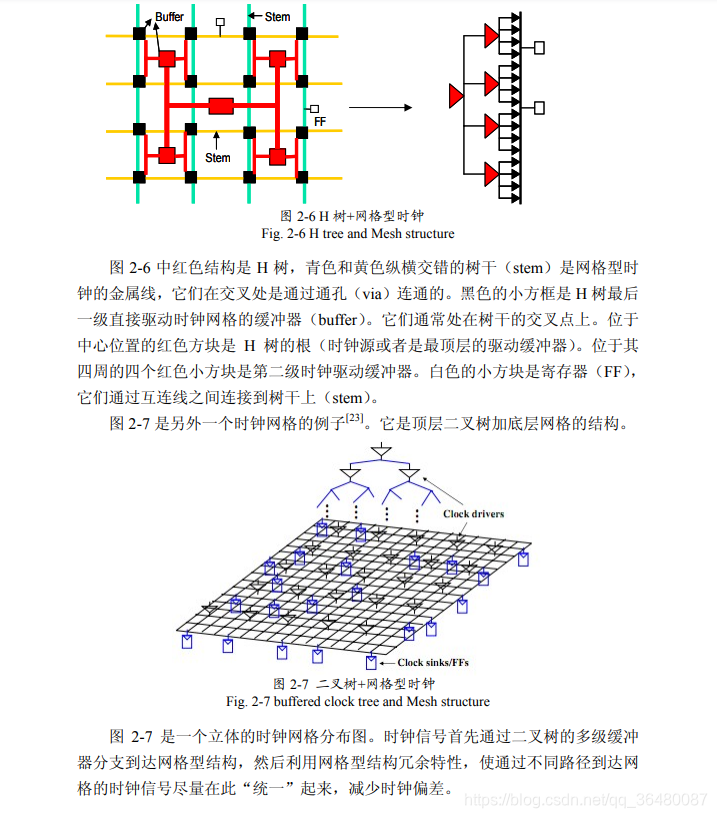

H tree

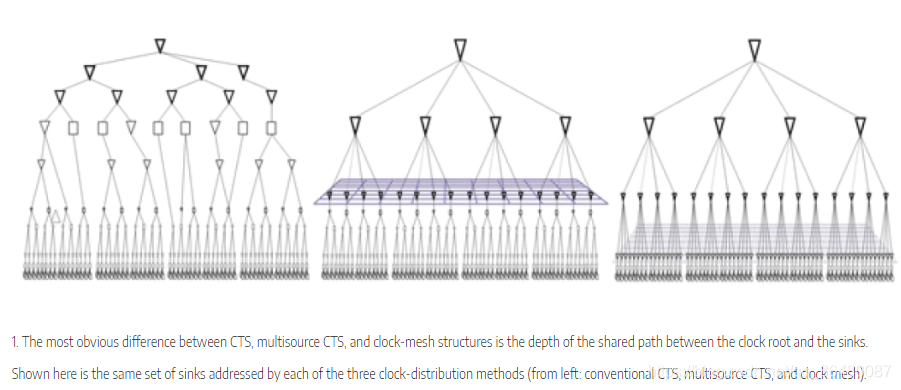

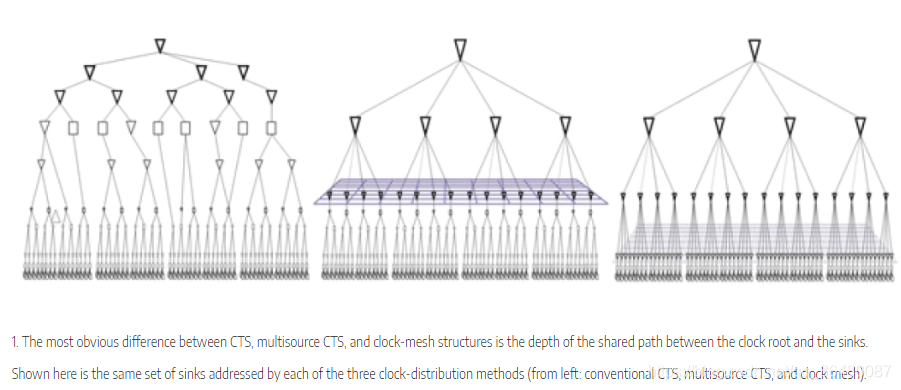

Multi Point CTS / Multi Source CTS

Analysis of Clock trees for optimization through Multi point Clock Tree Synthesis

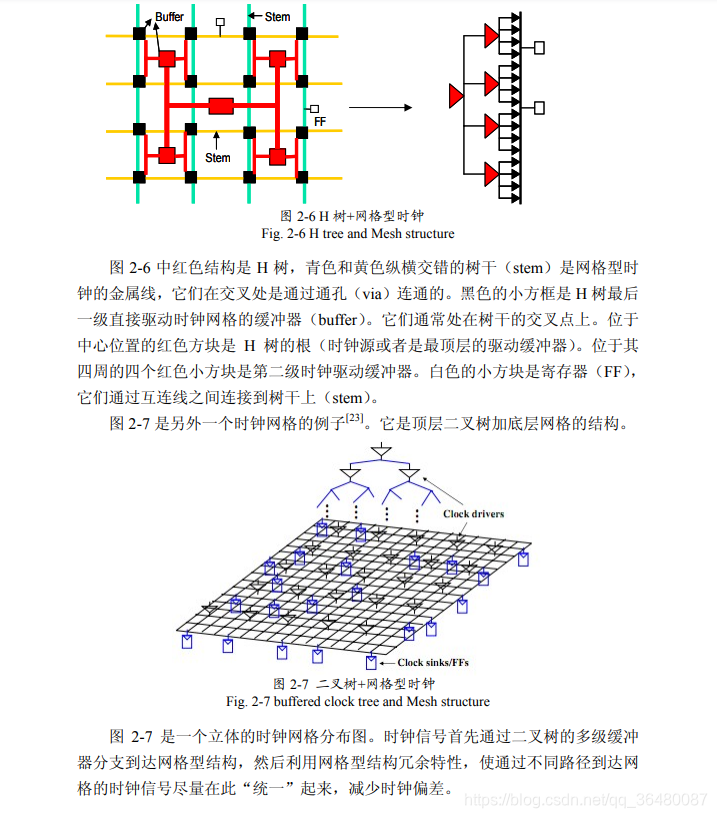

Clock Mesh

参考:

全芯片时钟网络的综合与优化方法

几种结构的关系和区别

个人理解:对于Multisource CTS

Analysis of Clock trees for optimization through Multi point Clock Tree Synthesis

参考:

全芯片时钟网络的综合与优化方法

个人理解:对于Multisource CTS

941

941

2733

2733

5044

5044

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?