低功耗设计基础:Power Gating详解

isolation cell是shutdown模块和always on模块之间的接口。

当信号从一个module传入另一个module,如果shutdown模块的电源关闭,则输出信号可能出现不可预测的数值,若此数值传递给always on模块,可能会导致功能出现问题。因此需要将电源关闭module的输出信号和其他module隔离开来,给所有的边界信号加入isolation cell(ISO)。

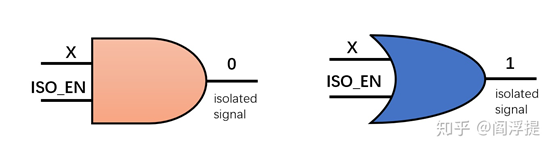

Isolation cell的作用在于在电源关掉之后,将某个信号电位固定到高电位或低电位,保证输出的信号是一个确定值(1或0)。其原理也很简单,基本上等同于AND或者OR门。

而电源打开时,Isolation cell则表现的像一个Buffer,输出等于输入即可。同时,如果被关断的电路输入固定电压,也可能产生对地的电流,Isolation cell可对该部分电流进行保护。一般来说Isolation Cell的输出部分有较大的电容负载,也就是说Isolation Cell的延时将会比较大,对时序有一定的影响,是需要注意的。

为了保证isolation cell能够在power down的时候仍然能够正常工作,一般来说isolation cell都会有一个primary power和一个secondary power,后者能够保证前者power down时器件仍然能够工作。

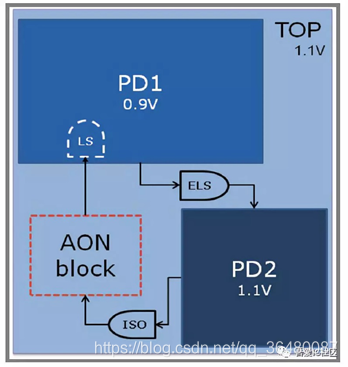

关于isolation cell的插入位置,我们需要决定是放在power gated module (source module)内还是always-on module (destination module)内。

摆放在 source module 的ouput 端一是可以节省所需要的 isolation cell 数量(考虑一个模块引脚的输出连到多个模块引脚的输入的情况),二是便于check。

摆放在destination module的input 端优点是 isolation cell 需要 always-on 的 power。若放在 source module的output端,还需要引 always-on 的 power rail 过来。

不管放在那里,其power的连接都需要额外的注意。isolation放置的地方都需要gated power和always-on power同时存在并且物理和逻辑连接都正确,因此经常会把isolation cell指定一个固定的区域放置,可以选择在此区域中打上两种不同的power stripe和power rail来连接它们,抑或选择让工具以自动routing的方式将secondary power连接起来,后者主要在非先进工艺中才可能出现。

对于数字后端实现而言,这个Isolation cell需要在综合阶段编写upf,让工具自动插入。

如果在source module进行 output isolation,那么需要避免power-gated buffer被插入到isolation cell的输出信号后面。

如果在destination module进行input isolation,在布局布线阶段,需要将ISO cell的input pin设置dont_touch,防止在PD2 输出信号和ISO cell之间插buffer。(个人理解:因为ISO cell是用来保证PD2关断之后,将PD2输出的X态信号转换成稳定的高/低信号,而如果在PD2输出信号和ISO cell之间插入了buffer,在PD2关断时,PD2的输出是X态,插入的这个buffer的状态就会有问题。)

本文详细介绍了低功耗设计中的PowerGating技术,并重点探讨了隔离单元(Isolation Cell)的工作原理及其在电源关闭时如何确保信号稳定。此外,还讨论了隔离单元在不同模块间的最佳放置位置。

本文详细介绍了低功耗设计中的PowerGating技术,并重点探讨了隔离单元(Isolation Cell)的工作原理及其在电源关闭时如何确保信号稳定。此外,还讨论了隔离单元在不同模块间的最佳放置位置。

2832

2832

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?