引言:

对于testbench是数字电路设计中不可或缺的一项设计方法,主要是提供的是激励。

尽管现在各种开发工具都通过绘制波形图的方法生成测试激励,测试书写的代码,但是其不可移植性,不可通用性,还有有些功能无法是实现,如监视变量的值的变化,显示数据的状态等。

一个完整的testbench包含下列几个部分:

(1)module的定义,一般无输入输出端口。

(2)信号的定义,定义哪些是你要输入,输入的定义为reg类型,输出的定义为wire型

(3)实例化待测试的模块

(4)提供测试激励

前仿也称功能仿真,testbench就是要对仿真的模块提供激励。

1

)时钟信号的产生

initial

begin

clk = 0;

forever //forever 必须写在initial里面

#clk_period/2 clk = ~clk;

end

**或者是**

always

begin

#clk_period/2 clk = 0;

#clk_period/2 clk = 1;

end

产生时钟的原理,是利用always或者是initial + forever产生不断重复的信号,构成时钟信号。

**或者是**

reg clk;

always #3.125 clk = ~clk; //160mhz always #10 clk = ~clk; 则为100mhz

initial

begin

clk = 0;

end

(2)复位信号的产生

复位信号就是在复位电平下延时一段时间,然后再将复位电平信号取反即可。如:

initial

begin

rst = 0;

# 100;

rst = 1;

end

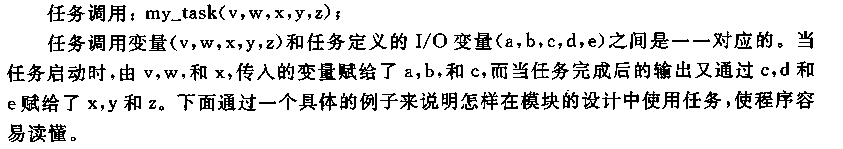

在实际应用将其封装为task,使用时掉调用即可。

调用如下:

initial

begin

sys_rst (100); //复位100个时间单位

end

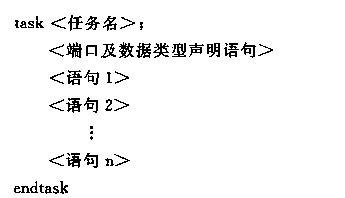

任务的定义如下:

task sys_rst ;

input [10:0] rst_time; //调用task的时候,将参数赋值给rst_time

begin

rst = 0;

#rst_time;

rst_time = 1;

end

endtask

testbench是一种验证的手段。

首先,任何设计都是会有输入输出的。但是在软环境中没有激励输入,也不会对你设计的输出正确性进行评估。那么此时便有一种,模拟实际环境的输入激励和输出校验的一种“虚拟平台”的产生。在这个平台上你可以对你的设计从软件层面上进行分析和校验,这个就是testbench的含义。

testbench里面包含了三个东西:

1、激励生成。也就是我们刚才初级时候说的所谓的“testbench”。英文么就是simulator,这个只用来生成输出,他自己没有输入,只是按照一定的规律去给你的设计激励,激励通过设计的输入端口送到你的设计中。其余的事情不管。这里的激励,都是预先设想好的,比如根据某个协议,或者某种通信方式传递。

2、你的设计。英文可以叫做DUT:design under testbench或者DUV:design under verification。当然咯。这个是你主要目标。

3、输出校验。校验你的输出。英文叫markerboard,他所管的事情就是,接收你设计的输入,然后通过校验,找出对应的问题。然后报错,或者统计错误。等等。通俗的讲,你设计它就是把你自己解脱出来,让他来帮你找错误。他输出给你的可能就是通过打印啊,通知啊,等等方法了解你设计的正确性。

initial repeat(13) #5 clk =~clk; //控制只产生13个时钟。

`timescale 1ns/10ps //单位时间/精度

附录:

testbench的几种思路:

一、只在testbench中实例化DUT(design under test),激励输入是在testbench中临时产生的,只能用于简单逻辑。优点:简单,易操作。缺点:复用性差 ,效率低

二、DUT的输入由单独的一个文件产生,在testbench中实例化两上entity,可以复杂输入,简单输出的模块。

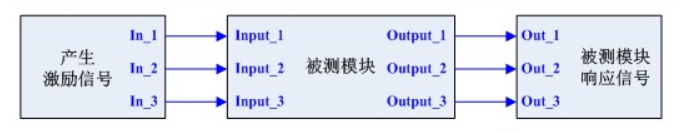

三、DUT的输入与测试输出各由单独文件产生,在testbench由三个实例化模块产生,用于具有复杂输入以及输出的模块。

四、可以根据仿真输出来修改输入激励的,可以自动通过输出来修改输入,使验证更加准确。

五、有文件做为testbench的输入,输出的模型。仿真中需要顺序的输入大量数据,以及接收相应的数据,可以通过从文件中读入数据,然后将产生的数据存入文件,使复杂系统验证更加方便。

六、可以将激励同时输入自己设计的模块和已经验证了相同模块,比较二者输出。。

Testbench用于测试模块的示意图如图

712

712

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?