在STA阶段经常会提到signoff corner , signoff view,这到底是什么?

其实这是我们做STA时候,需要考虑到的所有的情况的集合。signoff corner即PVT corner。

PVT:process/voltage/temperature。

1. overview

process

芯片制造工艺越发先进,技术节点越来越高,满足搞集成度的同时,也会带来其他问题,如芯片制造过程中的die to die variation,wafer to wafer的variation都不可避免,那么相应的std cell所受到的影响,我们在check timing 时候都需要考虑进来,这主要是工艺制造造成的偏差,有ocv/aovc/pocv等增量使我们的timing check更加精确。

voltage

1)假设我们选定的电压工艺,或者说我们给所做芯片规定1V的正常工作电压,那么实际的工作过程中,电压可能到不了1V,可能到0.95V,或者超过了1V到1.01V,都是有可能的。不同的电压对于同一个std cell,产生的delay是不同的,因此做signoff需要考虑到芯片的实际工作电压,一般会对标准电压进行百分比的检查,如1V的电压,会查1.1V~0.9V下是否timing 符合要求

2)另外为了low power,可能会做dvfs等功能,这样就造成我们芯片需要在多个电压下进行工作,因此会在1)的基础上对多个电压都进行检查

temperature

实际的芯片的工作温度,取决于芯片处于的环境温度和自身产生的热量,同一时刻,在哈尔滨和在厦门,芯片的工作温度必然不同,因此,需要对芯片进行高低温的timing check,一般-40C~125C进行signoff。对于功耗的检查一般在TT温度下85C

2.corner 边界/signoff corner

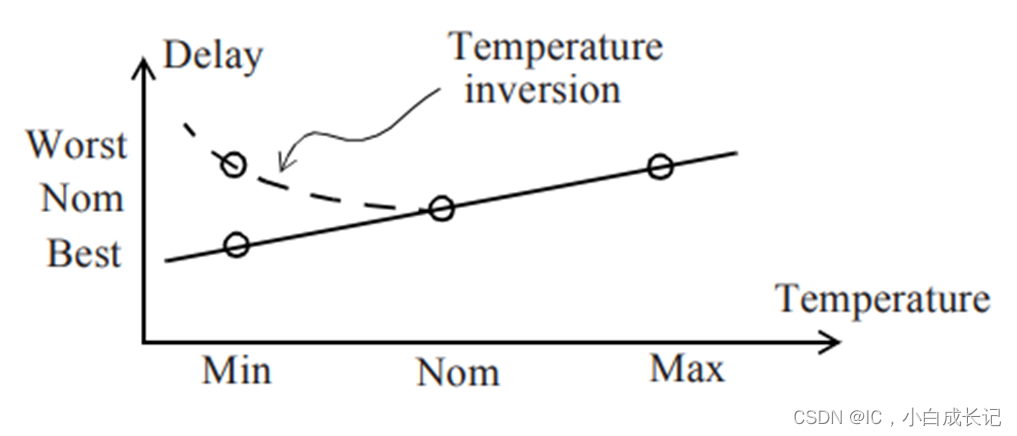

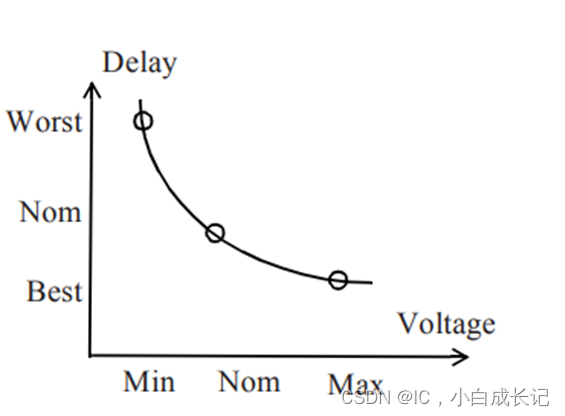

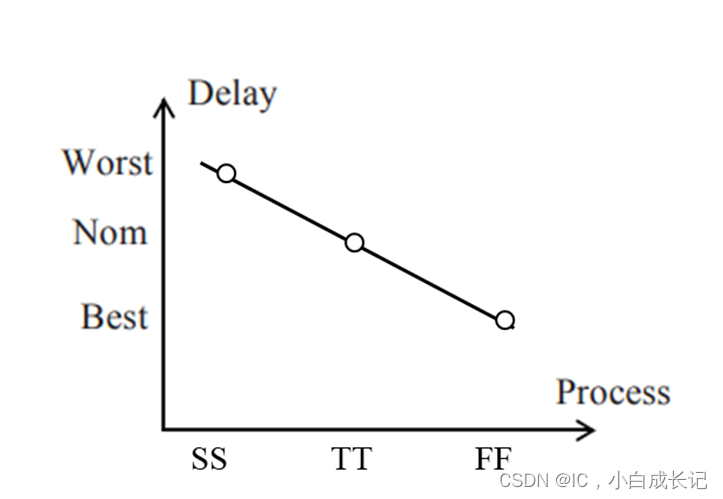

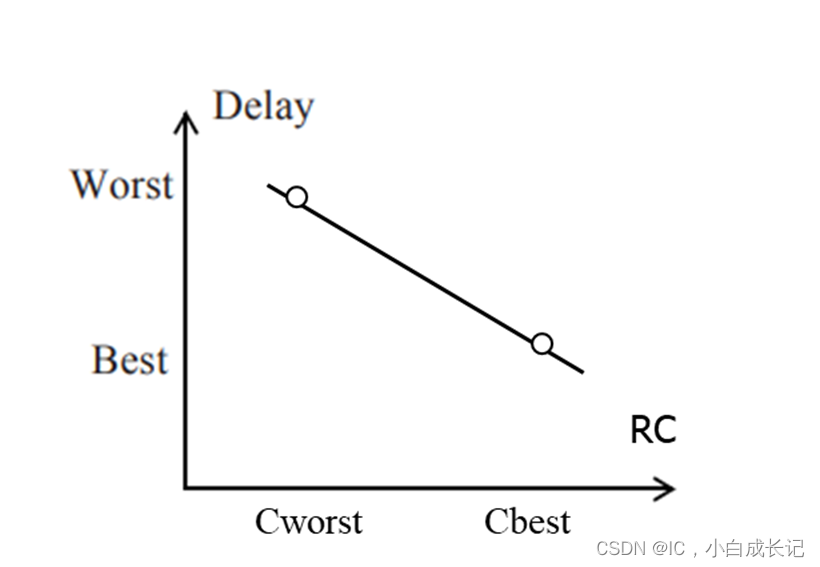

如下图所示,分别对应cell delay和温度/电压/process/RC的相关性。

温度越高,cell delay值越大,温度越低,cell delay 值越小。这个在比较老的工艺,如0.18/0.09um下是成立的,但是到了更先进的

工艺,如7nm,由于沟道变得非常短,会出现温度越低,cell delay反而越大的情况。电压越高,载流子流动速度越快,cell 的delay也就越小,反之,电压越小,cell delay越大。

ss对应cell delay较大的情况,ff对应cell delay较小的情况,TT对应normal情况。这种ss/ff/TT都由工艺制造的好坏决定。制造过程中,相同的cell,在不同的wafer或者不同的die,制造出来的cell delay大小都会有区别,尤其是先进工艺,本身Cell delay就小,这个差别就更加明显了。此处的cworst和cbest也是对于工艺来说的,cworst认为是耦合电容最差的情况,对应Cell delay也最大,cbest对应最小的情况。

由上面四个单独的线性关系,我们可以组合起来,得到signoff corner的边界如下图所示:101对应cell delay最大的corner,此时电压最低,温度最高,cworst,ss情况下。而104是cell delay最小的情况,对应电压最高,温度最低,cbest,ff情况下。途中的阴影部分面积为我们一个std cell所有可能的cell delay值的集合。我们在做timing signoff时候,就需要对其边界处的点进行timing 检查,理论上边界处的timing ok了,那么内部就不会有问题。

有时候一个大的design,可能会有超过200个signoff corner。因此STA也是一个很大的工作量。

974

974

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?