这里的部图片引用尤老师时序分析公开课,B站可以找到。

PT(Prime Time)简介

PT简介

PrimeTime是Synopsys的一个单点的全芯片、门级静态时序(STA)分析器。

静态时序分析(英语:Static Timing Analysis, STA),或称静态时序验证,是电子工程中,对数字电路的时序进行计算、预计的工作流程,该流程不需要通过输入激励的方式进行仿真。

功能:分析大规模、同步、数字ASIC的时序。

优点:不依赖于激励,且可以穷尽所有路径,运行速度很快,占用内存很少;它完全克服了动态时序验证的缺陷,适合进行超大规模的片上系统电路的验证,可以节省多达20%的设计时间。

相关概念

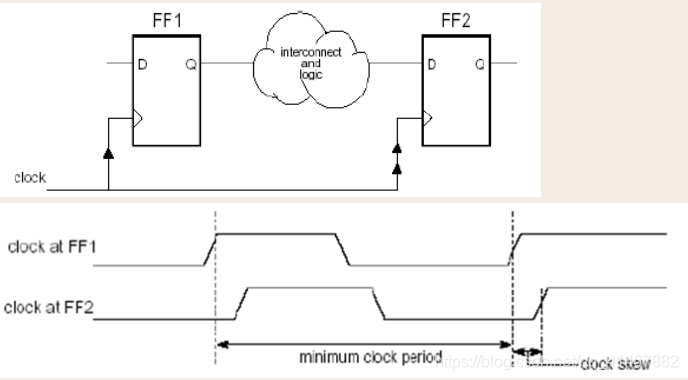

时钟偏斜(Clock Skew)

定义:集成电路中一个时钟翻转的到达时间在空间上的差别,如下图所示:

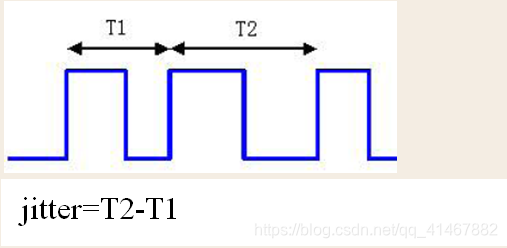

时钟抖动(Clock Jitter)

定义:指两个时钟周期之间存在的差值,这个误差是在时钟发生器内部产生的

引起因素:

时钟信号的产生本身就会引起抖动

材料的纯度引起的器件的参数不一致

金属互连线长度不同

环境变化(温度和电源)

电容耦合

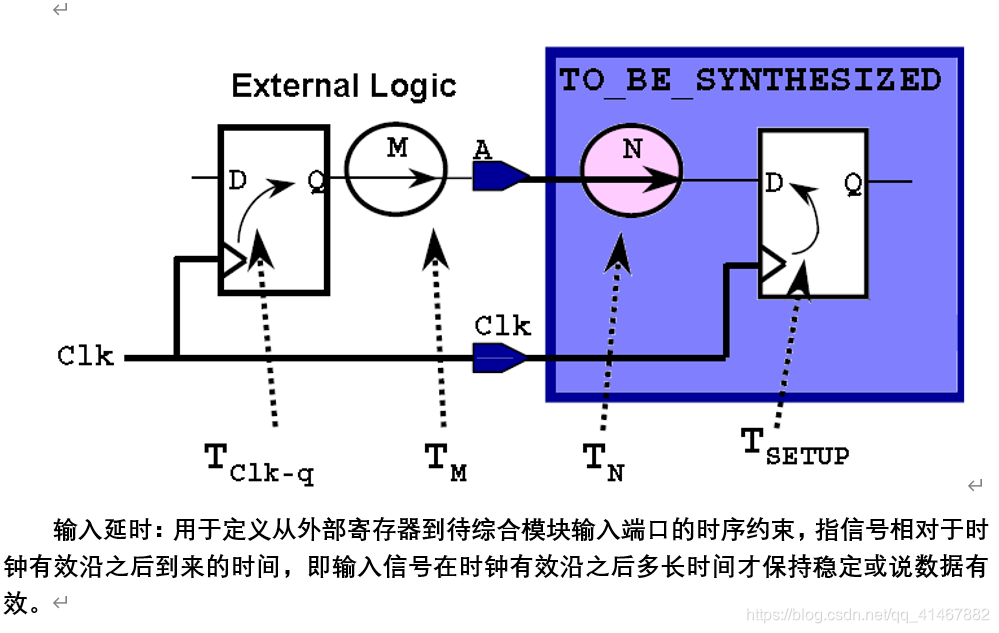

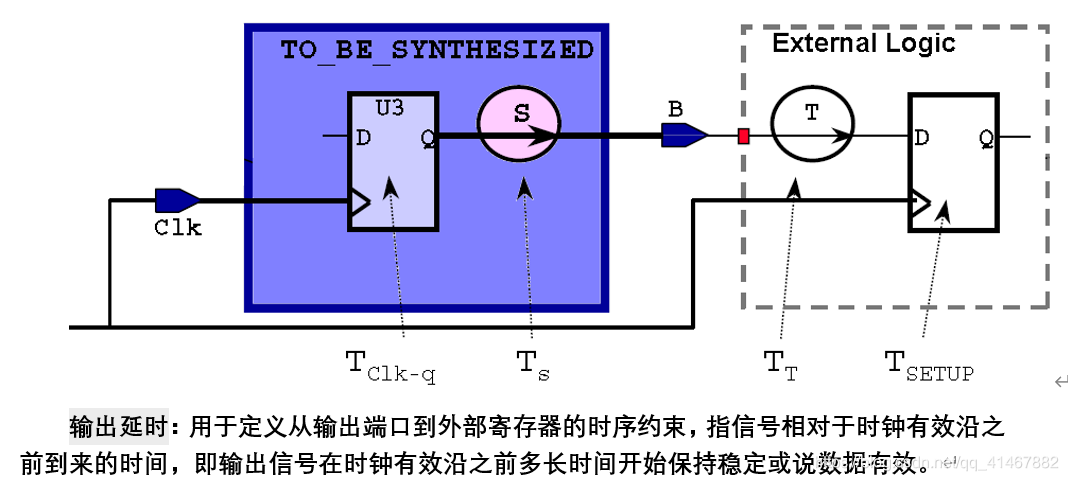

输入输出延时

这里根据定义,加上输入延时的计算为

Tdin=Tclk-q+Tm+Tn+Tsetup

这里的时间Tn是不需要进行约束的,时序分析工具是知道其内部的时间延时的,而外部的时序信息相关的延时是怎么样的,这个就需要我们对其进行约束,也就是我们所说的input delay

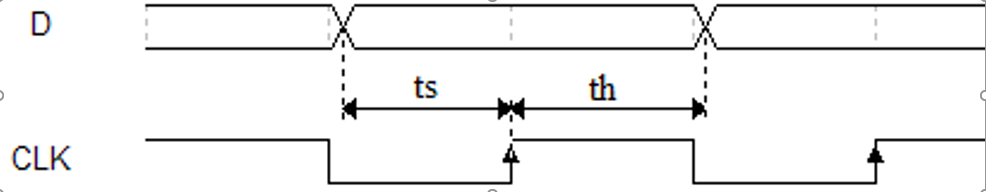

建立时间与保持时间

在这里插入图片描述

建立时间(ts):指寄存器的时钟信号有效沿到来之前数据必须稳定的最小时间。

保持时间(th):指寄存器的时钟信号有效沿到来之后数据必须稳定的最小时间。

这里笔者理解的是建立时间与保持时间其实对于一个给定的器件应该是确定的。

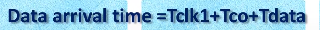

数据到达时间

Def:数据从一级寄存器输入段到达二级寄存器的输入端的时间

Tco为数据在寄存器中传输的延时

Tdata为数据经过一级寄存器(或经过组合逻辑),进入二级寄存器输入端的延时时间

Tclk1为基准时钟与时钟到达一级寄存器的偏斜时间

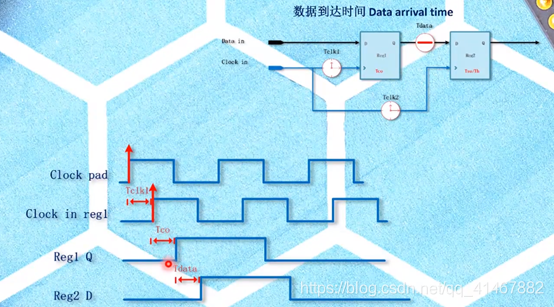

要求数据到达时间

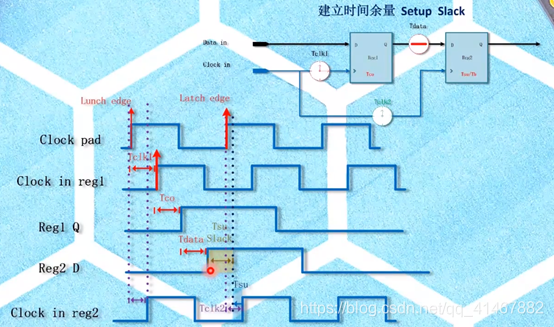

Define:根据两级寄存器的是时钟偏移,加上数据的建立时间,计算要求数据到达的时间,就是说数据可以比这个时间早,一旦晚于这个时间,可能会出现某些问题。

Tsu:建立时间(时钟采样到来前数据理论上应该保持的时间)

Tcycle:Lunch edge(发射沿)到达Latch edge(锁存沿)的时间

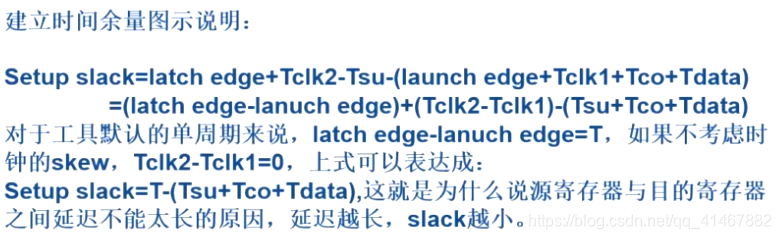

建立时间余量

这里理解的建立时间其实应该是一个确定的时间,就是时钟上升沿到来之前数据必须准备好的时间。

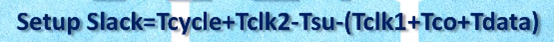

这里的建立时间余量就是数据最晚到来的时间减去数据实际到来时间就是建立时间余量。公式如下:

最小时钟周期

这里其实根据这个建立时间裕度的计算图可以看出,当裕度为0的时候,即可得到最小时钟周期,即为1/(数据到达时间+建立时间-二级寄存器的时钟偏移时间)

以上计算仅供参考

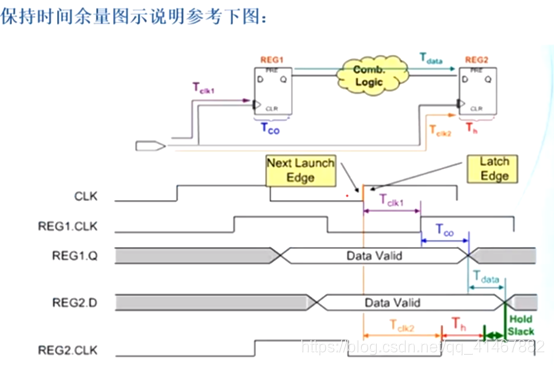

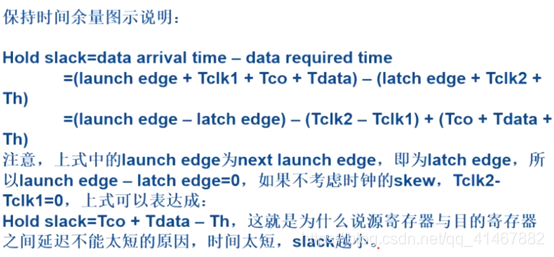

附录保持时间计算

这里先简单自己分析下,首先我们看到,数据到达时间等于数据要求达到时间(二级寄存器时钟偏移以及保持时间)+保持时间余量。因此这里假设中0偏移,保持时间余量为零(保持时间define:上升沿到达后数据应该保持的时间),所有要满足时序的要求,极限情况就是Tco+Tdata=Th。这里理解其实就是怕这个数据还没有取到,而下一个数据已经来了,因此就会使得错过这个数据,因此要求下一个数据到来的瞬间取到数据就是极限,也就是上边的极限情况的公式,假设不忽略时钟的偏移,直接从图中也能看出,

Tclk1+Tco+Tdata=Tclk2+Th+Thold_slack

下面的图是老师PPT的分析截图

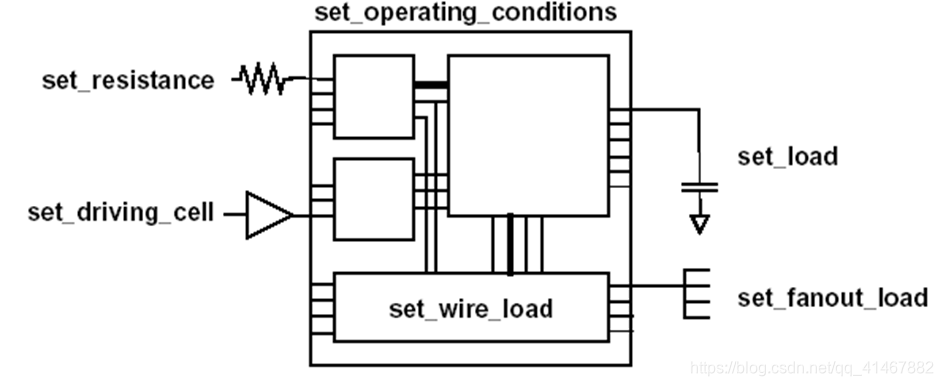

需要进行的约束

定义设计环境

在对设计作时序分析之前,必须要定义好设计环境以使得在那些情况下满足限制条件。时钟,输入、输出延迟,输入端口的外部驱动,电容负载,运作条件,连线负载电容。

时序声明

- 说明时钟信息

- 描述一个时钟网络

- 说明时钟门锁建立和保持时间

- 建立内部生成的时钟

- 说明输入延时

- 说明时钟端的输入延时

- 说明输出延时

时序例外

Prime Time缺省地认为所有的电路都是单时钟周期的。

在某些情况下,电路不是工作在这样的方式下。对具体的一条路径来说不适用单始终周期时序,所以必须对这些缺省的时序假设作例外说明。否则,时序分析将不能反映真实电路的工作情况

相关内容:

- 单时钟周期(缺省)路径延时限制

- 设置失败(False)路径

- 设置最大和最小路径延时

- 设置多时钟周期路径

- 路径说明方法

- 有效地说明例外情况

- 例外情况的优先级

- 报告例外情况

- 忽略例外情况

- 去除例外声明

其他概念

反标记

一个布局器或一个布线器提供更详细和更精确的延时信息, 可以用来提供给PrimeTime作更精确的分析。这个过程被称作反标(back-annotation)。反标信息经常是以标准延时格式Standard Delay Format(SDF)提供的。

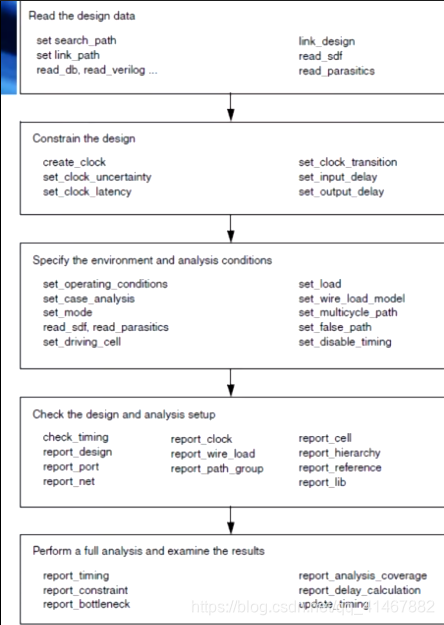

PT工作流程

下面的这个流程图很好的介绍了相关的步骤以及命令,因为是截图的老师的PPT,所以不是很清楚…这里简单进行分析总结

首先读入,其次约束设计,接下来设置环境以及时序例外,然后检测综合,最后就可以查看相应的报告了,这里需要对那些进行约束,DC部分以及本节前面的定义已经在一些方面进行了介绍,以后有时间在具体写一篇分析。

常用命令

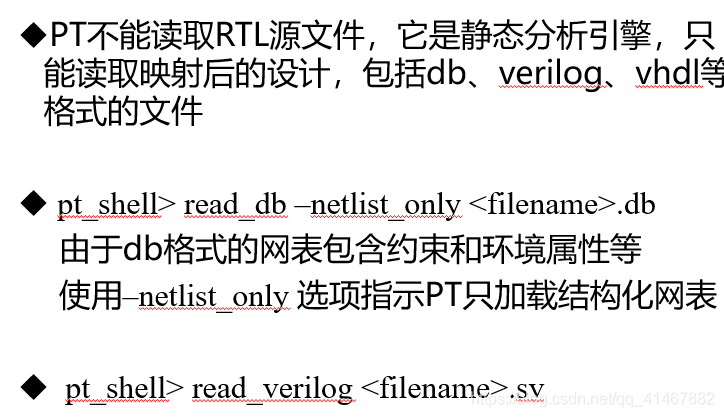

设计输入

时序规范

创建时钟

![create_clock -period period_value[-name clock_name][-waveform edge_list][source_objects]pt_shell>create_clock -period 4 -waveform [list 0 2] –name\ clk [get_ports clk]](https://i-blog.csdnimg.cn/blog_migrate/cf8e9c6f2c1442caedaa15d066dc5fd7.png)

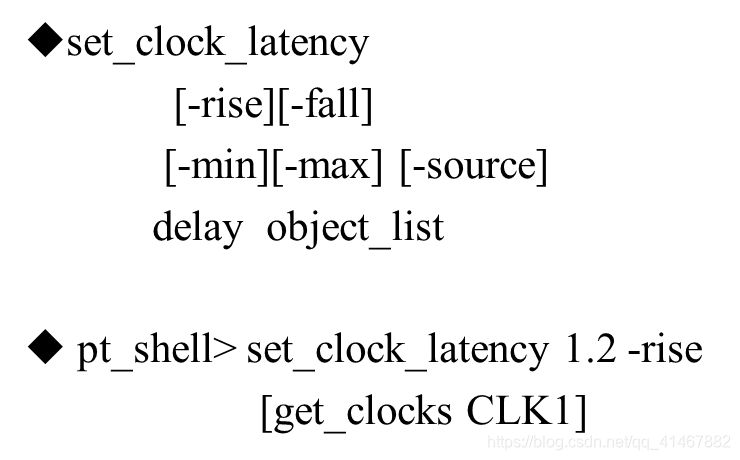

时钟延时

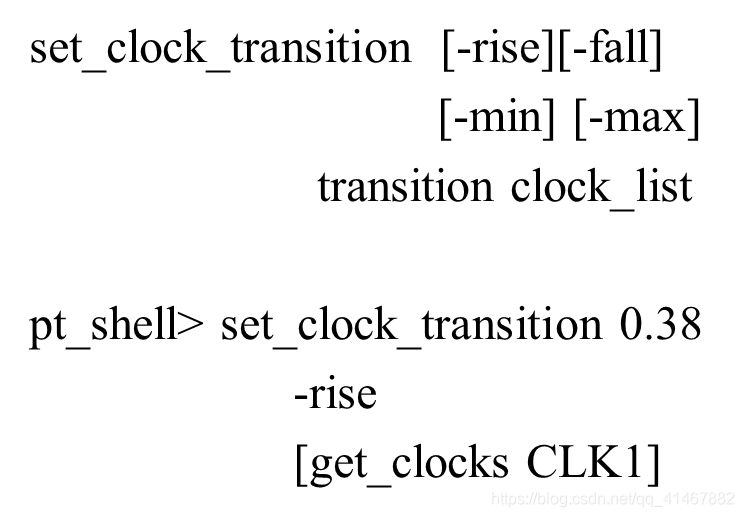

时钟转换

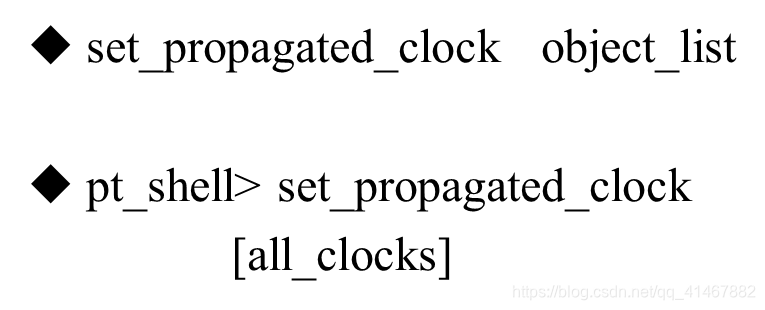

传播时钟

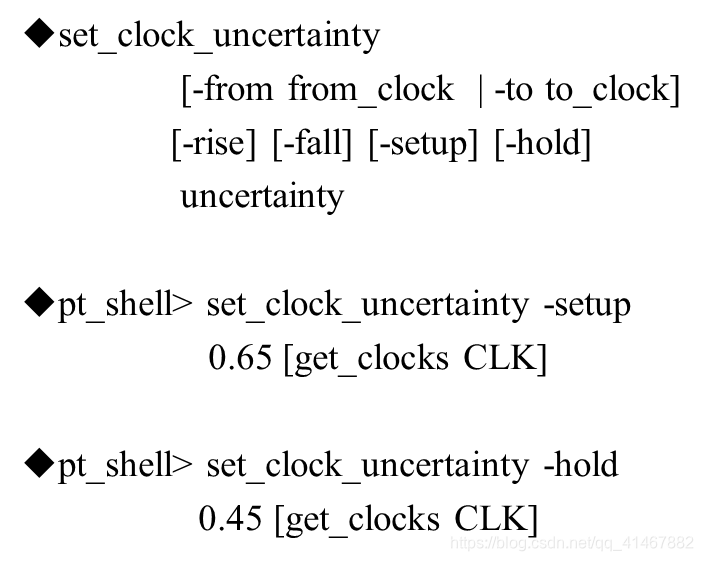

时钟歪斜

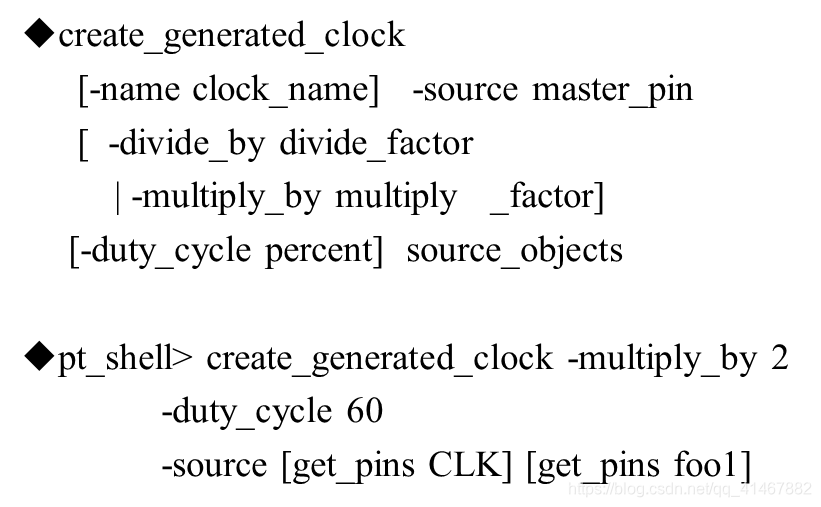

指定生成的时钟

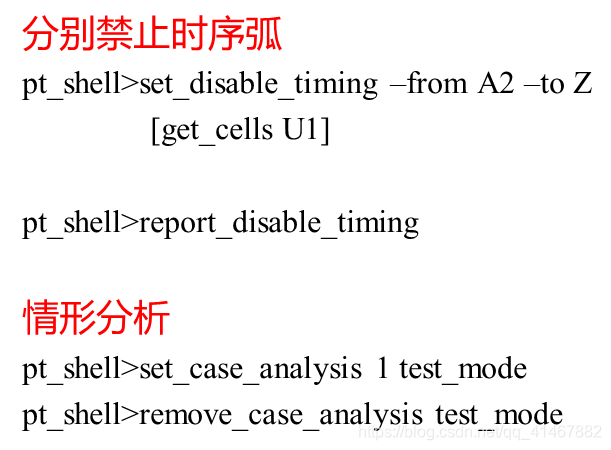

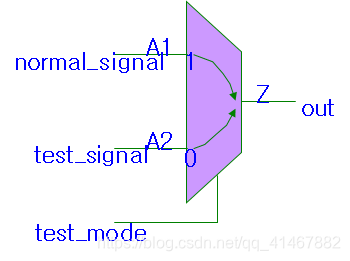

禁止时序弧(时序例外)

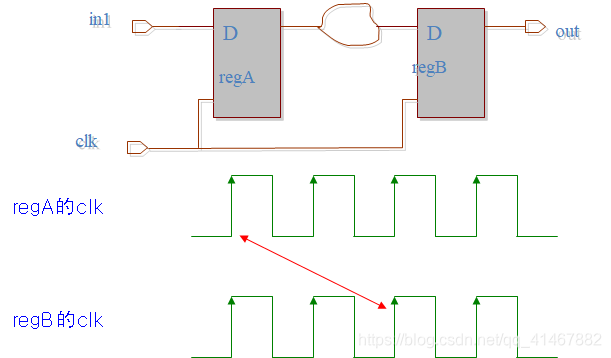

多周期路径(时序例外)

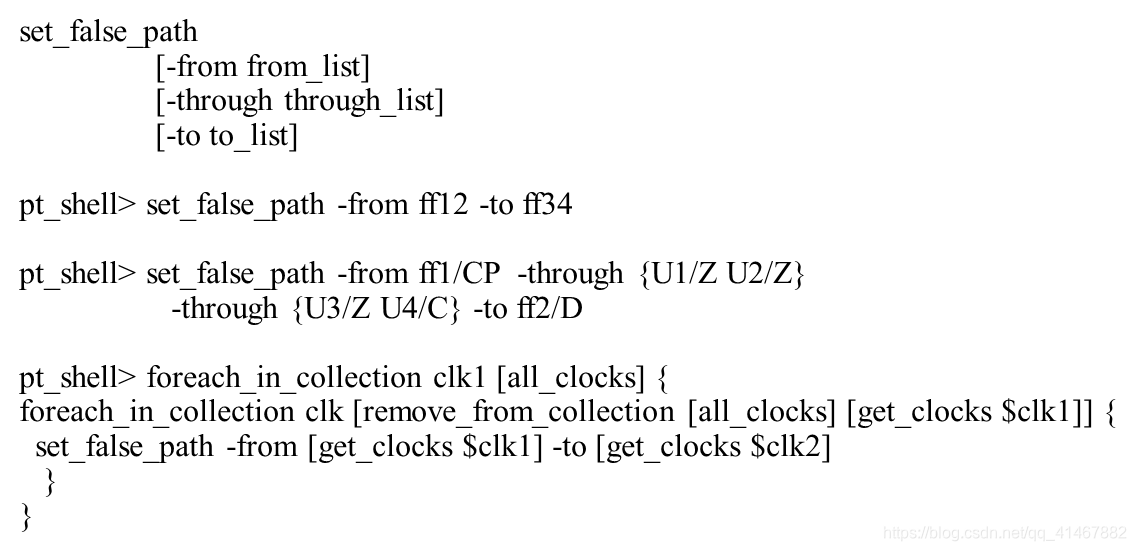

虚假路径(时序例外)

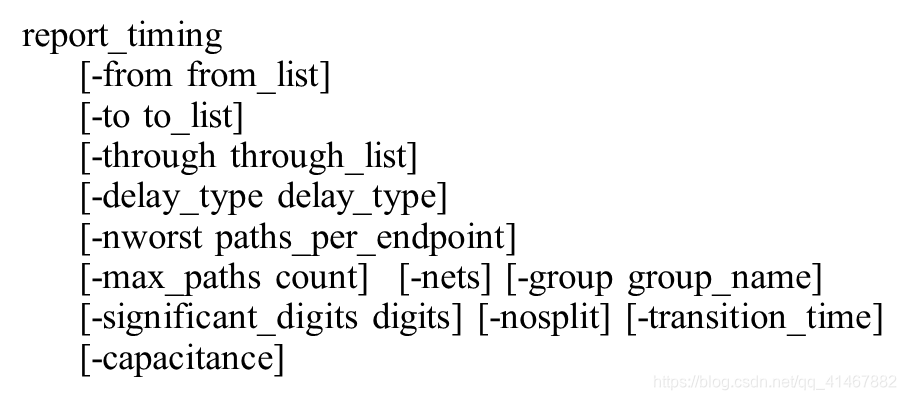

生成报告

1064

1064

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?