关于Altera和Xilinx芯片的复位使用

概述

1、对于Altera的FPGA而言,因为里面的flip-flop只支持低有效的异步复位,所以推荐使用低有效的异步复位。

2、对于xilinx 7系列的FPGA而言,flip-flop支持高有效的异步复/置位和同步复位/置位。对普通逻辑设计,同步复位和异步复位没有区别,当然由于器件内部信号均为高有效,因此推荐使用高有效的控制信号,最好使用高有效的同步复位。输入复位信号的低有效在顶层放置反相器可以被吸收到IOB中。如下3点是Xilinx器件的复位准则:

(1)尽量少使用复位,特别是少用全局复位,能不用复位就不用,一定要用复位的使用局部复位;

(2)如果必须要复位,在同步和异步复位上,则尽量使用同步复位,一定要用异步复位的地方,采用“异步复 位、同步释放”;

(3)复位电平选择高电平复位;

Global Reset Isn’t Timing-Critical:全局复位不是时序关键

- 全局复位的典型驱动:

(1)按键开关:复位信号接一个按键,反应非常慢(ms级别),并且非常不确定(按键抖动?);

(2)电源状态输出:上电后由电源芯片产生一个监测信号复位系统,可以长时间的保持,直到电源稳定后进行正常工作;

(3)微处理器等控制芯片:控制芯片产生复位脉冲;

以上所有情况下,复位信号似乎是缓慢的,因此,我们也可以有把握地认为,它对时序不会造成关键影响。当为您的FPGA设计指定定时约束时,这个信号通常会被分配一个长周期(低频)。

但是,全局复位不是时序关键的假设并不全对,随着时钟频率的增加,全局复位对时序会带来很大的影响。虽然复位脉冲可以用比时钟周期更长的持续时间,并保证所有触发器都可以被成功复位,但是复位信号的释放应该被认为是一个时间关键事件。

FPGA内部的全局置位/复位(GSR)信号也是一个全局复位,这也是FPGA器件内部的一个高扇出网络(high fan-out)。在一个设计中,虽然启动序列可以与“用户时钟”同步,但不能保证它不能与所有时钟都同步。FPGA器件有多个DLL/DCM/PLL模块,每个模块都能够产生多个不同频率和相位的时钟。

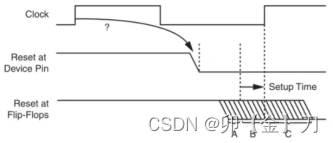

在图1中,一个复位信号在两个时钟边沿之间的某个时间被释放。复位信号经过一段时间传播到各种触发器,在每个触发器中,复位信号都应该在下一个有效的时钟边沿的“Set-up time”(建立时间)前就无效。很明显,当时钟频率上升时,可以用来分配给复位信号释放的时间就会减少。考虑到复位信号是一个高扇出网络,所以复位释放的时序不易收敛。

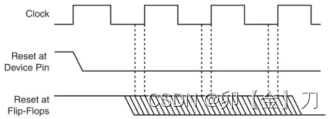

如果复位的释放与时钟异步(通常就是这种情况),那么就无法保证所有触发器都能在同一个时钟边缘释放(图2)。

当在A时刻释放reset时,触发器将在第一个时钟边沿检测到有效的释放信号;在C时刻释放reset时,复位的释放将直到下一个时钟边沿才被检测到;B时刻时钟上升沿时触发器检测到的reset状态很难确定(可能高电平,也可能低电平),可能导致亚稳态。

随着时钟频率的提高和与大型器件潜在的分布倾斜,几乎不可避免的是,无法保证所有的触发器的复位都能在同一个时钟边沿被释放(图3)。

Does It Really Matter?:复位真的是必须的吗?

好消息是,在99.99%的情况下,全局复位的异步释放对系统没什么影响,所以大多数电路都能正常工作。如果一个电路不工作,那可能恰好是遇到了另外的0.01%,不幸地在错误的时间释放了复位。

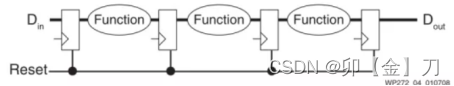

在图4所示的流水线场景中,复位释放的时间并不重要。

当数据通过流水线进程时,复位的释放时间无关紧要。即使出现了错误,在经过一定时钟周期后整个系统就能恢复。这种情况下,复位是没有意义的。当有效的数据输入时,初始状态或者未知的状态将从系统中清除。

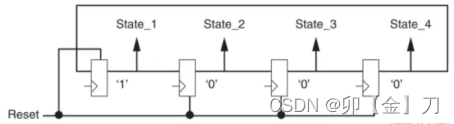

但是,在图5显示了独热码状态机场景中复位释放的时间非常重要。

在上面的独热码状态机中,有明显的失败可能性。如果第一个触发器在第二个触发器的前一个时钟周期释放,那么独热码的热状态将丢失,状态机将永远变冷(状态机无法恢复)。将所有的触发器尽可能的靠近布局能够降低错误的发生概率(在局部重置网络上的低倾斜)。然而,除非Set-up timie建立时间得到保证,否则这种错误情况仍有可能发生。如果所有触发器没有在同一个时钟周期中释放,编码后的状态机可能进入意外状态或则会非法状态。

最后,需要仔细考虑复位的是包含反馈路径的电路。

没有反馈的电路实际上根本不需要复位。在数字信号处理应用中,有限脉冲响应滤波器(FIR)是没有反馈的。在有效数据填充了所有的抽头之前,输出样本实际上没有有效的值,所以复位抽头寄存器没有任何效果。然而,无限脉冲响应滤波器(IIR)包含反馈。如果因为不干净的复位释放而产生了一些不符合预期的输出,该输出结果又会返回到输入,那么会在很长一段时间内无法获取真实的输出结果(反馈环路互相影响了)。在最坏的情况下,由于不稳定,滤波器可能会完全失效。

Automatic Coverage of the 99.99% of Cases:自动覆盖99.99%的案件

当配置或重配置Xilinx FPGA时,内部所有的单元都被初始化(图6)。这是master reset复位的结果,因为它涉及的远不止简单的触发器。

上电配置与全局复位具有相同的寄存器复位效果,但除此之外,上电的配置还初始化了所有RAM单元。随着FPGA器件上RAM资源的增加,这是一个非常有用的特性。所有RAM内容的初始状态都是已知的,这对于仿真和操作是非常理想的,并且消除了使用启动序列来清除内存的要求。

由于处理器也嵌入到Xilinx设备中(无论是硬核还是软核),所有程序和数据区域的初始状态在处理器执行第一条指令之前就已经定义了。在这样的前提下,为了重置一些触发器的初始状态而消耗宝贵的可编程资源是没有意义的。仿真器应该能够对这个初始化(通常称为上电复位)建模,这再次避免了在设计中对复位信号的任何要求。

Strategy for the 0.01% of Cases:针对0.01%违例的策略

最重要的是,有一种策略来处理设计中的复位。设计的关键部分在于必须在相关的时钟域同步释放,可以插入一个局部的高性能复位网络来控制那些需要局部复位的触发器。

图7中的电路是控制局部复位网络的一种可能有用的机制,该电路的优点是使用外部复位信号时的效果和使用器件上电配置产生的效果一样(异步复位、同步释放,避免了释放带来的亚稳态)。

在配置FPGA或异步复位信号期间,链中的所有触发器都预设为1。链上的最后一个触发器几乎立即将一个有效的复位信号驱动到局部复位网络。随着全局置位/复位(GSR)或者异步复位的释放,移位寄存器链开始在每个时钟周期填满0。

链中触发器的数量决定了传输到局部复位网络的复位脉冲的最小持续时间。链路的最后一个触发器进行一个从高电平到低电平的转换,局部复位与时钟同步释放。复位的触发器可以采用同步置位(FDS)或同步复位(FDR),从而实现完全同步设计,并易于时序规范和分析。

Reset Costs More Than You Think!:复位成本比你想象的要高!

在实现设计时,大多忽略了HDL代码中全局复位的代价,但是全局复位的代价可能是巨大的:

(1)布线资源

♦ 减少了其他连接的自由度;

♦ 可能会降低系统性能,由此需要更高速度等级的FPGA,增加了成本;

♦ 增加的布线时间;

(2)逻辑资源

♦ 触发器专用复位的使用;

♦ 在D输入或专用复位输入之前需要有额外的逻辑门;

♦ 几乎肯定会影响设计的尺寸;

♦ 额外的逻辑层次几乎肯定会影响系统性能;

♦ 增加布局和布线的时间;

(3)无法使用高效率的特性,如SRL16E

♦ SRL16E可以在每个LUT中实现多达16个虚拟触发器(Xilinx器件的高效应用);

♦ 上述实现的虚拟触发器不支持复位,当HDL指定复位时,综合工具就无法使用SRL16E来减少触发器的使用;

♦ 高达16倍的尺寸和产品成本的增加;

♦ 额外的大小可能会降低系统性能;

♦ 增加布局和布线的时间;

关于复位信号如何影响资源利用率的讨论,请参见WP275 Get your Priorities Right - Make your Design Up to 50% small。

另可查看最新xilinx手册ug949_UltraFast设计方法指南中相关介绍。

Summary:总结

在Xilinx FPGA中实现的设计不需要插入全局复位网络。 对于绝大多数设计,所有触发器和RAM的上电后的初始化状态比任何的逻辑复位都要全面,不需要为了仿真而插入复位,因为没有任何东西是未定义的。由于Xilinx FPGA已经经过了全面测试,因此在设计中不需要扫描逻辑和运行测试向量。因此,全局复位也不需要作为这个过程的一部分。

插入全局重置将影响开发时间和产品成本。随着时钟和完整系统在芯片上实现更高速度的趋势,可靠性问题必须得到重视。必须确定系统中真正需要复位的关键部件,并且在启动或运行过程中,必须像控制同步电路中的任何其他信号一样小心地控制这些复位的释放。

当设计每个部分时,都要问一问:“这个部分需要复位吗?”

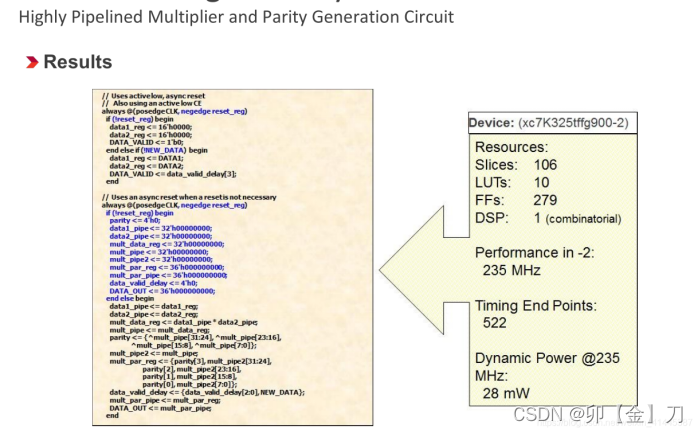

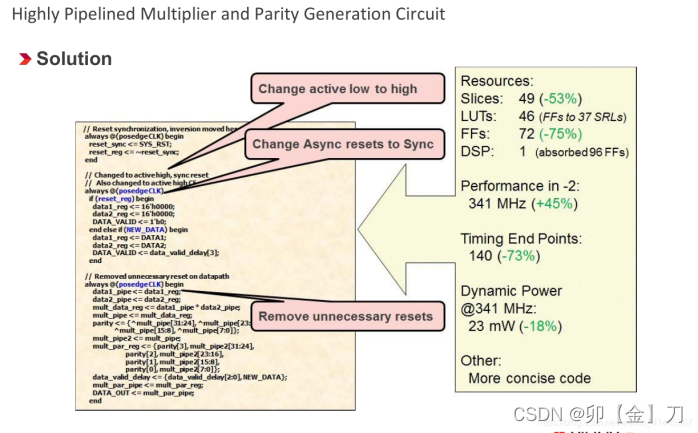

在vivado中验证这一理论时发现没有太大区别。

如下图为同步复位和异步复位的综合区别:

创作不易,希望大家多多点赞!!!如有错误或者不同的见解,欢迎评论区提问。

9542

9542

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?