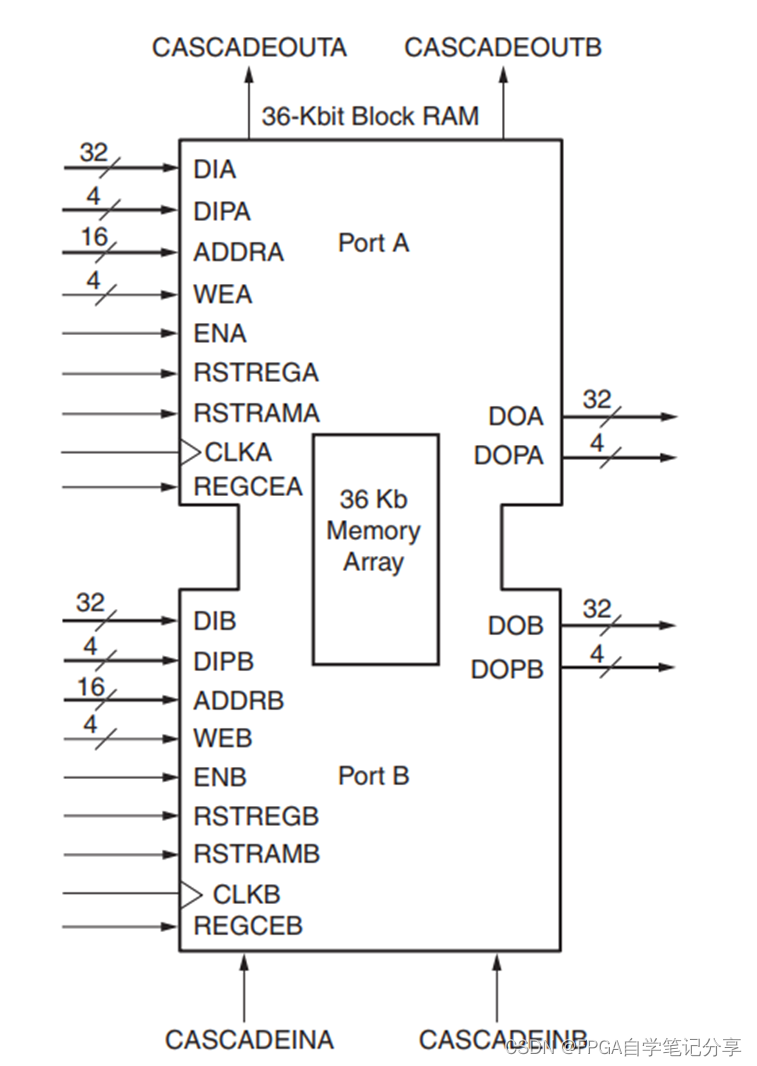

Xilinx7系列FPGA中的块RAM可存储36 Kb的数据,可以配置为两个独立的18 Kb RAM或一个36 Kb RAM。在简单双端口模式下,每个36 Kb块RAM可以配置为64K x 1(与相邻的36 Kb块内存级联时)、32K x 1、16K x 2、8K x 4、4K x 9、2K x 18、1K x 36或512 x 72。在简单双端口模式下,每个18 Kb块RAM可以配置为16K x 1、8K x2、4K x 4、2K x 9、1K x 18或512 x 36。

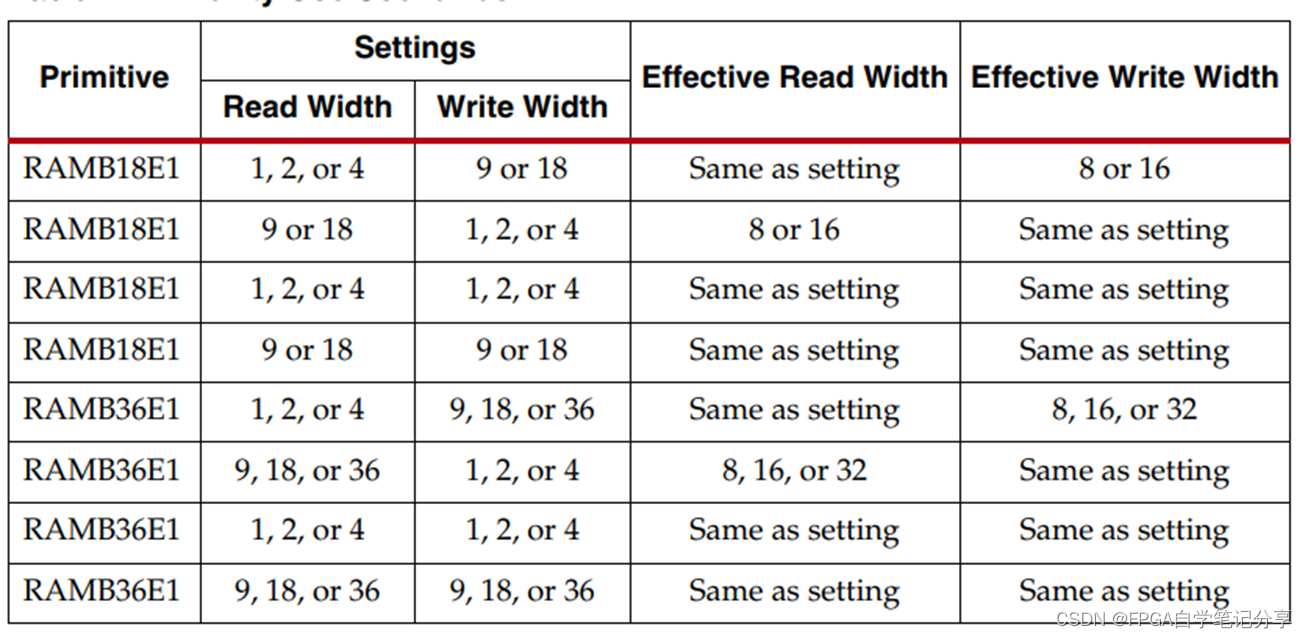

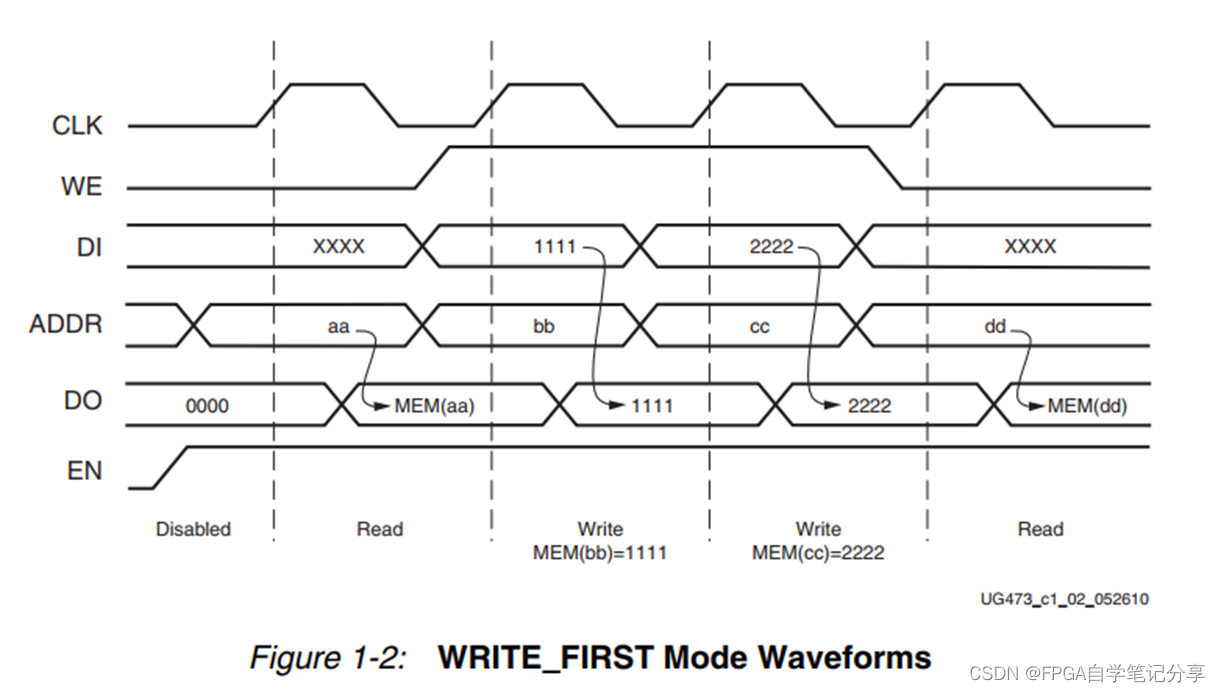

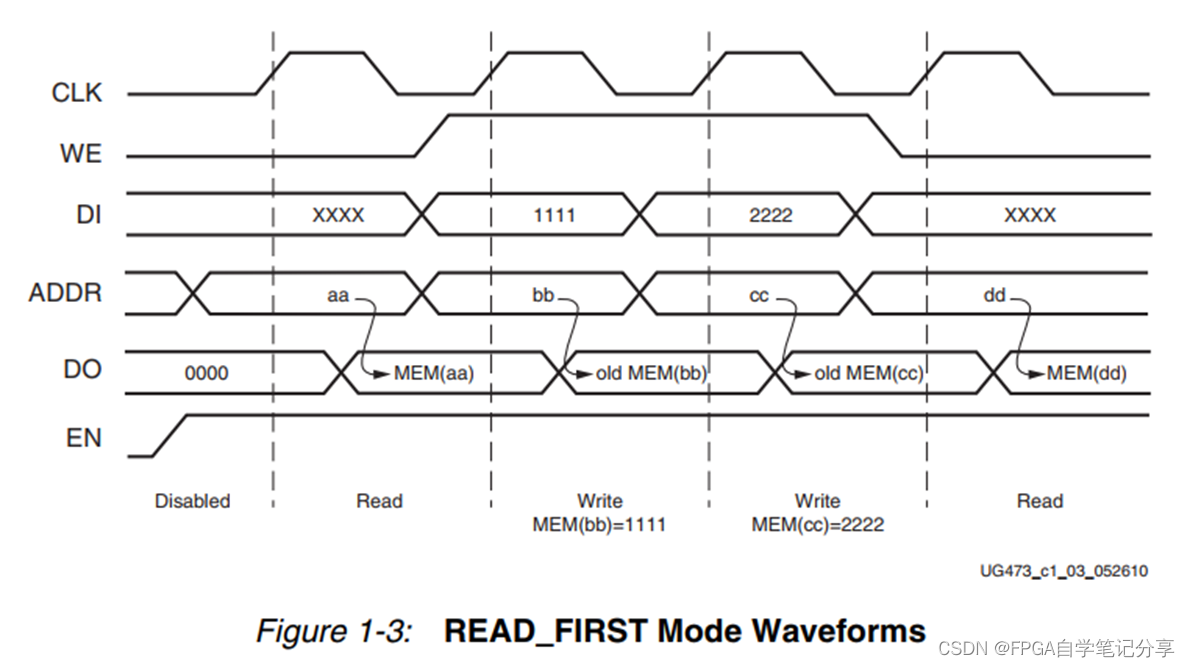

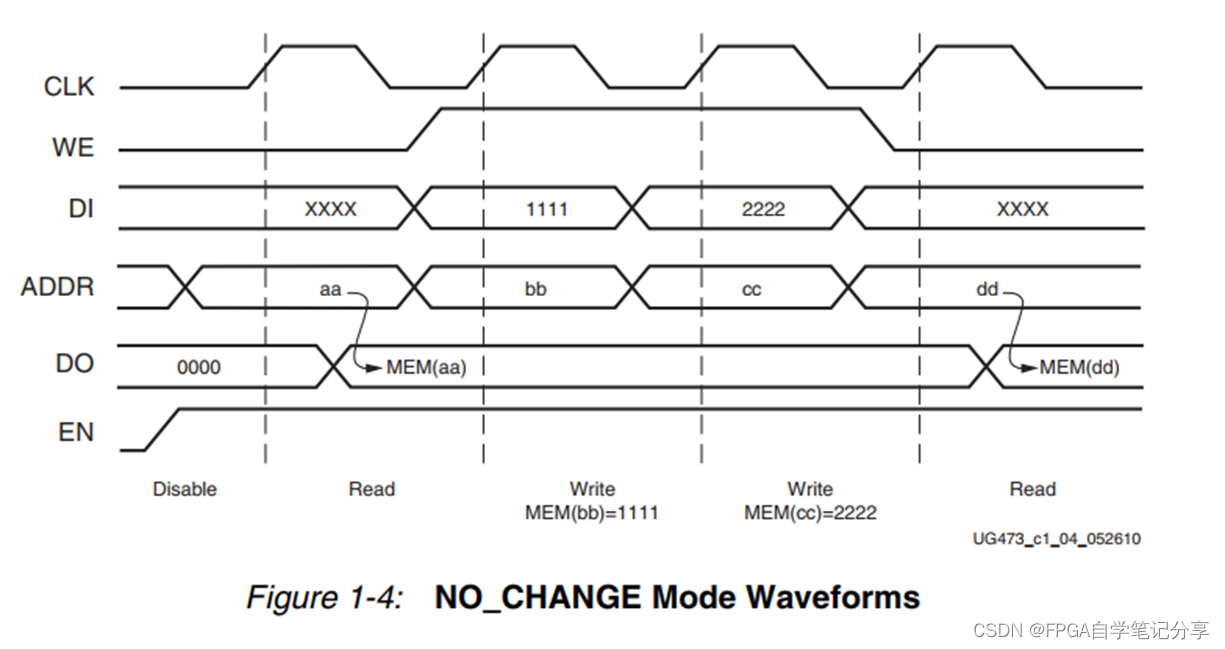

两个端口对称且完全独立,仅共享存储的数据。每个端口可以独立于另一个端口以一个可用宽度进行配置。此外,每个端口的读端口宽度可以不同于写端口宽度。可以通过配置位流初始化或清除内存内容。在写入操作期间,可以将内存设置为数据输出保持不变,反映正在写入的新数据或正在覆盖的先前数据。

7系列FPGA块RAM功能包括:

•每个块内存存储能力,其中每个块RAM最多可存储36 kbit的数据。

•支持两个独立的18Kb块,或一个36Kb块RAM。

•每个36Kb块RAM可设置为简单双端口(SDP)模式,将块RAM的数据宽度加倍至72位。18Kb块RAM也可以设置为简单的双端口模式,将数据宽度加倍至36位。简单双端口模式定义为具有一个只读端口和一个具有独立时钟的只读端口。

•简单双端口RAM在一侧支持固定宽度数据端口设置,另一侧支持可变数据端口宽度设置。

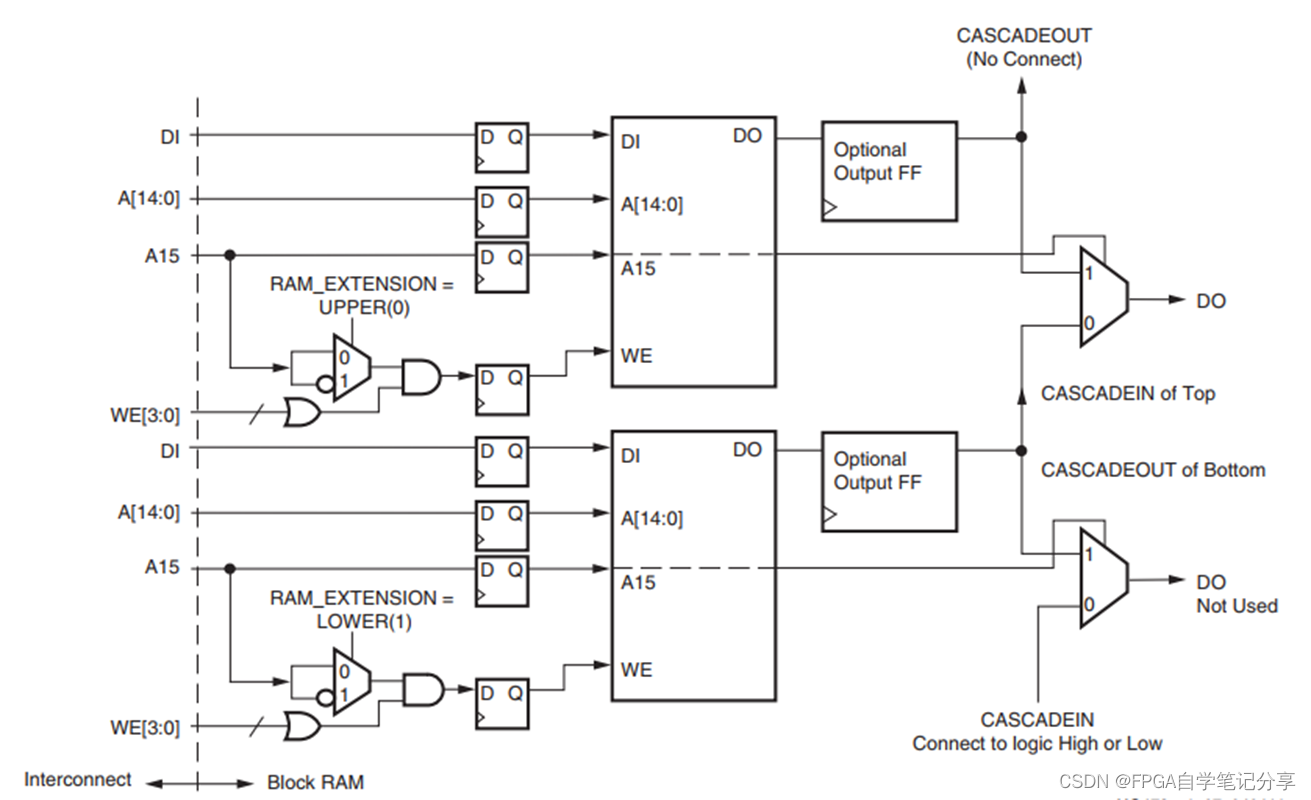

•两个相邻的块RAM可以组合到一个更深的64K x 1内存中,无需任何外部逻辑。

•每36 Kb块RAM或36 Kb FIFO提供一个64位纠错编码块。单独的编码/解码功能可用。在ECC模式下注入错误的能力。

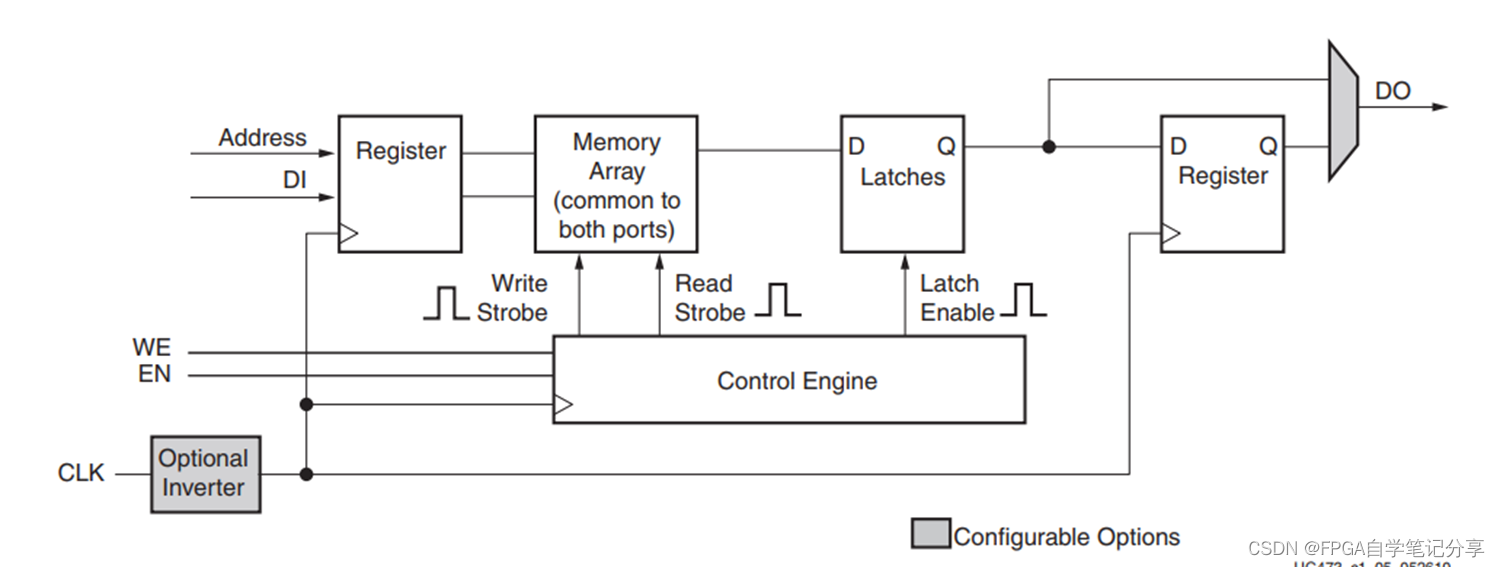

•对于块RAM输出的锁存和寄存器模式,可将输出同步设置/重置为初始值。

•独立的同步设置/复位引脚,独立控制块RAM中可选输出寄存器和输出锁存级的设置/复位。

•18、36或72位宽的块RAM端口可以具有每个字节的单独写入。此功能在与微处理器接口时很受欢迎。

•每个块RAM包含可选的地址排序和控制电路,作为内置双时钟FIFO存储器运行。在7系列体系结构中RAM可以配置为18 Kb或36 Kb FIFO。

•所有输出都具有读取功能或写入期间读取功能,具体取决于写入启用(WE)引脚的状态。

•写入操作需要一个时钟边沿。

•读取操作需要一个时钟边沿。

两个相邻的块RAM可以组合到一个更深的64K x 1内存中,无需任何外部逻辑。

时钟可反向,输出可以选择是否经过reg:

bram的三种读写方式:

2685

2685

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?