How to Insert Test Points and Perform Scan

Stitching Using Third-Party Tools

您可以使用Tessent Shell执行测试点分析。这些测试点的插入和扫描链拼接可以使用第三方工具完成。分析测试点后,使用report_test_points编写报告。

ANALYSIS> analyze_test_points

ANALYSIS> report_test_points > test_points.list

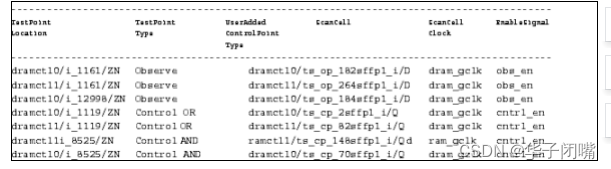

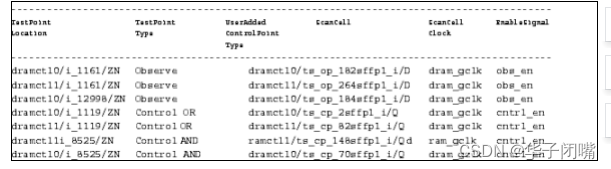

An example report

TestPointLocation列指定需要拦截功能网络的位置。ScanCell时钟列指定要插入的测试点触发器的实例名称。TestPoint Type(测试点类型)列指定测试点的类型。需要连接的时钟在扫描单元时钟列中指定到测试点触发器。测试点可以作为连接到压缩器和压缩扫描链插入。Mentor Graphics建议您将测试点缝合到各自独立的扫描链中,以便更高效地生成低功耗EDTpattern。

Test Point Usage Scenarios

Test Points for ATPG Pattern Count Reduction

Test Points for Reducing Pattern Count

The

测试点的目标主要是减少EDTpattern count。测试点也可以提高测试覆盖率,但影响可能很小。必须首先分析测试点并将其插入网表,以减少模式计数,从而改进压缩。可以使用扫描前设计或扫描后缝合网表。测试点分析完成后,可以报告所需数量的测试点,也可以将其插入设计中。可以写出已插入测试点的修改网表和包含设计流程下一步所需信息的flow。

Requirements for Test Point Analysis and Insertion

Requirements for Test Point Analysis and Insertion

执行测试点分析和插入有一定的要求。

必须遵守以下规定:

•测试点插入需要门级Verilog网表和测试单元库。

•可以读取功能性SDC,因此该工具将省略向多周期路径或错误路径添加任何测试点。请参阅read_SDC命令。

•该工具识别潜在的扫描候选,以进行正确的可控性/可观测性分析。为了确保最终的非扫描单元不会用作观察点的目的地或控制点的源,您应该在测试点插入期间使用add_nonscan_instances命令声明所有非扫描存储器元件。

•应该使用add_black_boxes命令定义黑框,以便测试点分析可以包含此信息。

•如果正在具有未连接时钟网关的预扫描网表上执行测试点分析,则应将“set_clock_gating on”命令添加到您的数据文件中

Specify Test Point Type

默认情况下,该工具生成专门用于减少确定性pattern count 的测试点。可以指定测试点类型。

Prerequisites

•

The tool must be in SETUP mode to specify the test point type.(定义类型)

Procedure

<

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

883

883

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?