目录

引言

按照视频的讲解进度,继续学习 VCS的使用。

前两篇文章:

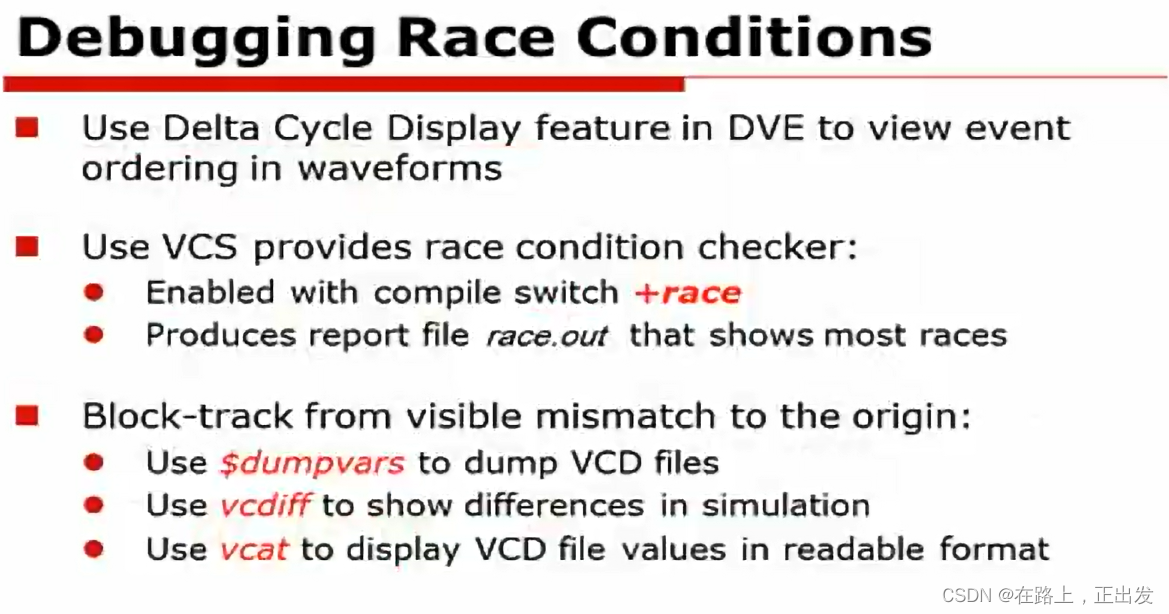

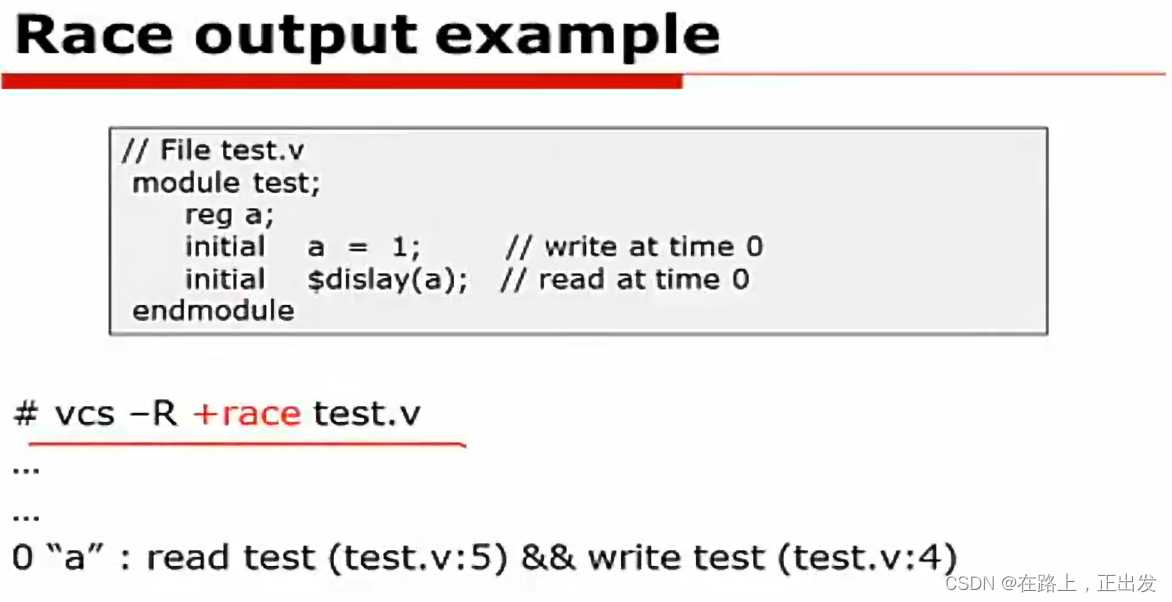

本文主要是 debug一些和预想功能不匹配的仿真。

本系列文章建议电脑端查看~~

方法

使用例子:

原因

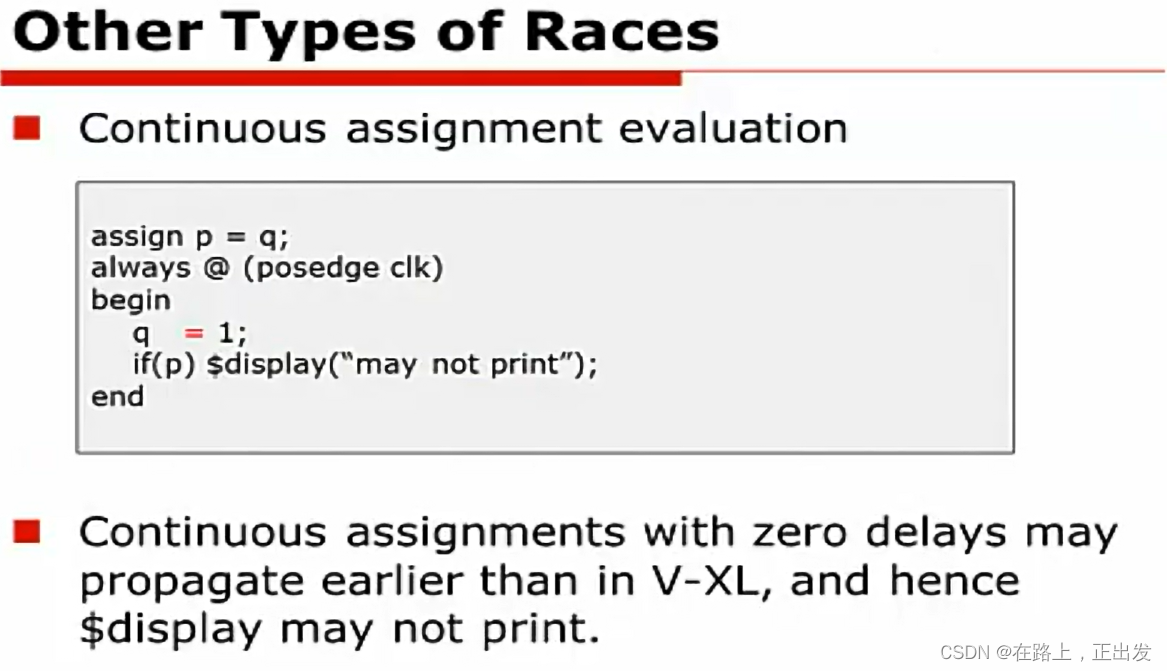

竞争冒险条件

仿真事件队列

0时刻不匹配

时序冒险

规则

实际操作

根据视频中的示例给出设计和仿真代码:

设计代码:

// |-------------------------------------------------------

// | Description: two stages flip-flop design and compare

// | Date:2022-11-08

// | Author:Xu Y. B.

// |-------------------------------------------------------

`timescale 1ns/1ns

module DFF_EXP (

// -------------- input / output ports specify ------------

input I_CLK,

input I_RSTN, // Asynchronous reset active low

input I_D,

output reg O_Q

);

// -------------- module internal signal specify ----------

reg R_Q1;

// -------------- module internal logic -------------------

`ifdef DEF_CORRECT

always @(posedge I_CLK or negedge I_RSTN)

begin

if(~I_RSTN)

begin

R_Q1<= 0;

end

else

begin

R_Q1 <= I_D;

end

end

always @(posedge I_CLK or negedge I_RSTN)

begin

if(~I_RSTN) begin

O_Q<= 0;

end

else

begin

O_Q <= R_Q1;

end

end

`else

always @(posedge I_CLK or negedge I_RSTN)

begin

if(~I_RSTN) begin

R_Q1 = 0;

end

else

begin

R_Q1 = I_D;

end

end

always @(posedge I_CLK or negedge I_RSTN)

begin

if(~I_RSTN) begin

O_Q = 0;

end

else

begin

O_Q = R_Q1;

end

end

`endif

endmodule仿真代码:

// -------------------------- testbench for module DFF_EXP ----------------------------

// Date:2022-11-09

// Author:Xu Y. B.

// ------------------------------------------------------------------------------------

module TB();

// -------------- input / output ports specify ------------

reg I_CLK;

reg I_RSTN; // Asynchronous reset active low

reg I_D;

wire O_Q;

// clock generate

initial I_CLK <= 0;

always #5 I_CLK <= ~I_CLK;

// ctrl and input generate

initial

begin

I_RSTN <= 1'b1;

I_D <= 1'b0;

repeat(5) @(posedge I_CLK);

I_RSTN <= 1'b0;

repeat(5) @(posedge I_CLK);

I_RSTN <= 1'b1;

repeat (10)

begin

@(posedge I_CLK);

I_D <= ~I_D;

end

$finish;

end

initial

begin

`ifdef VPD_TEST

$vcdpluson(1,INST_DFF_EXP);

`endif

end

// instantiate module

DFF_EXP INST_DFF_EXP

(

.I_CLK(I_CLK),

.I_RSTN(I_RSTN),

.I_D(I_D),

.O_Q(O_Q)

);

endmodule

makefile

.PHONY: com cov clean debug

# output file name

OUTPUT = simv_DFF

# define

VPD_SW_DEFINE = +define+VPD_TEST

FUNC_SW_DEFINE = +define+DEF_CORRECT

# code coverage command

CM = -cm line+cond+fsm+branch+tgl

CM_NAME = -cm_name $(OUTPUT)

CM_DIR = -cm_dir ./$(OUTPUT).vdb

# vpdfile name

VPD_NAME = $(OUTPUT).vpd

# compile command

VCS = vcs -full64 -cpp g++-4.8 -cc gcc-4.8 -LDFLAGS -Wl,--no-as-needed \

-sverilog +v2k -timescale=1ns/1ns \

-debug_access+r \

-Mupdate \

+notimingcheck \

+nospecify \

+vcs+flush+all \

$(VPD_SW_DEFINE) \

-o $(OUTPUT) \

-l compile.log

# $(CM) \

# $(CM_NAME) \

# $(CM_DIR) \

# simulation command

SIM = ./$(OUTPUT) \

-l $(OUTPUT).log

# $(CM) $(CM_NAME) $(CM_DIR) \

# $(VPD_NAME) \

# start complie

com:

find -name "*.v" >filelist.f

$(VCS) -f filelist.f

# start simulation

sim:

$(SIM)

mv vcdplus.vpd $(VPD_NAME)

# show the coverage

cov:

dve -covdir -vdb &

debug:

dve -vpd $(OUTPUT).vpd &

# start clean

clean:

rm -rf ./csrc *.daidir *.log *.vpd *.vdb simv* *.key *race.out* *.so.*至于操作的细节和过程和视频中的相同,此处就不再赘述。~~~

6082

6082

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?