在DC/DC芯片的应用中,我们需要提前来规划EMC的设计,避免在后期把太多的时间和精力花在整改和优化上。

说到EMC优化设计,我们要从EMC的三要素来分析和考虑:干扰源→耦合路径→敏感设备。我们通过抑制干扰源、切断耦合路径、保护敏感设备三个措施,来优化EMC设计。在DC/DC芯片应用中,DC/DC芯片通常是系统中常见的干扰源,我们主要从DC/DC这个干扰源的抑制来优化EMC设计。

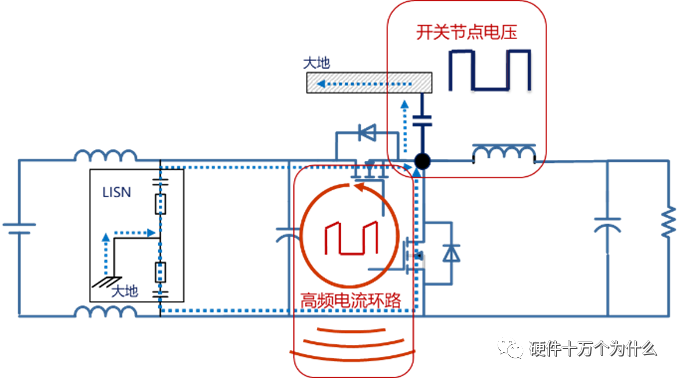

在DC/DC电源中,Buck是最常见的电路拓扑,我们以Buck为例分析噪声源。Buck电路的主要噪声源是高频电流环路(Hot loop)和高频开关节点(SW note), 包含了比较宽频段的谐波分量,如图14.23所示。

图 14.23 高频电流环路(Hot loop)和高频开关节点(SW note)

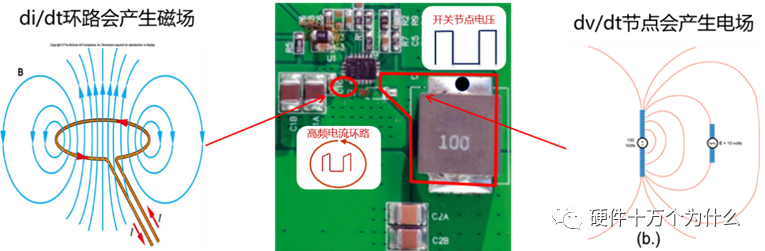

高频电流环路和高频开关节点分别产生时变的磁场和电场,其在PCB中的位置如图14.24所示。

图 14.24 高频电流环路和高频开关节点PCB中位置

以Buck电路为例,输入电流环路有梯形波的di/dt波形,而电感上存在三角波的di/d

【细说Buck】Buck电路的噪声源的抑制

最新推荐文章于 2024-05-18 19:58:32 发布

订阅专栏 解锁全文

订阅专栏 解锁全文

1932

1932

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?