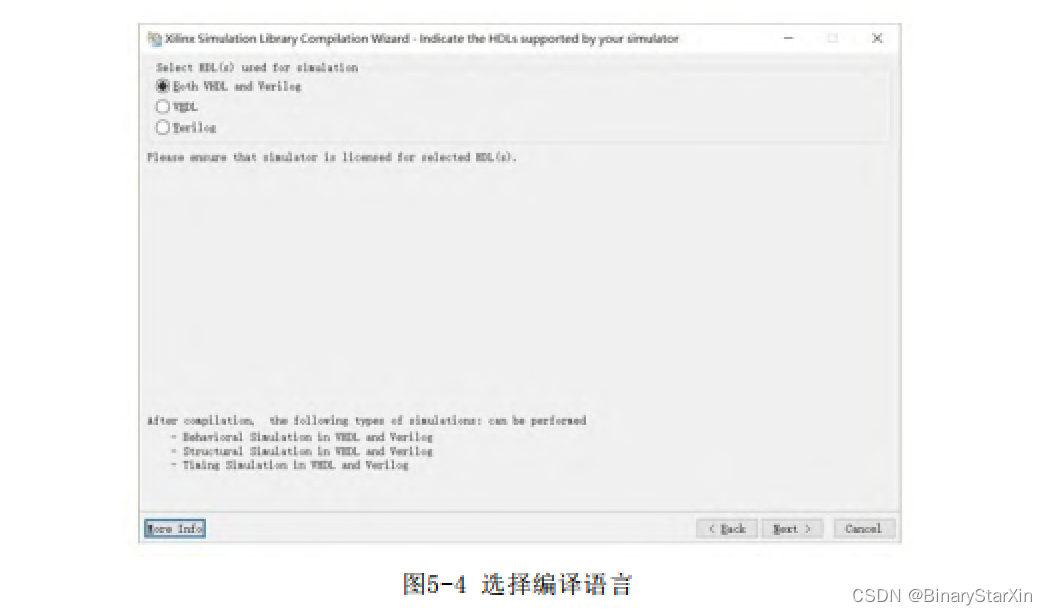

所选择的Modelsim版本为Modelsim SE,选中Modelsim的安装路径下的win32文件夹,默认配置文件和日志文件,单击“下一步”。选择编译语言,如图5-4所示。

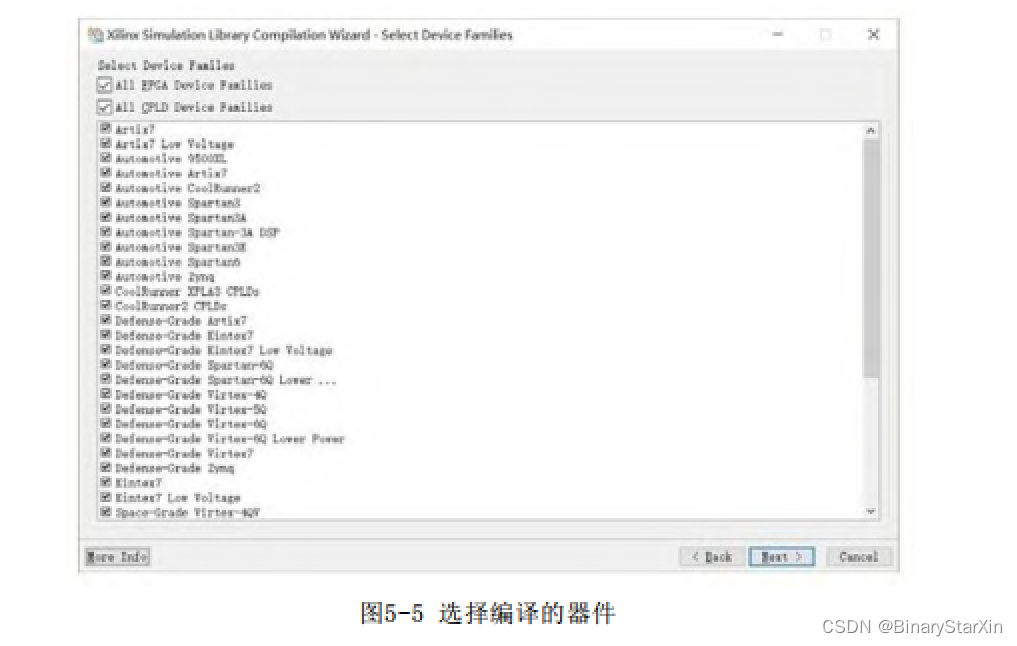

根据所用的语言选择编译语言,接着,单击“下一步”,选择编译的器件,如图5-5所示。

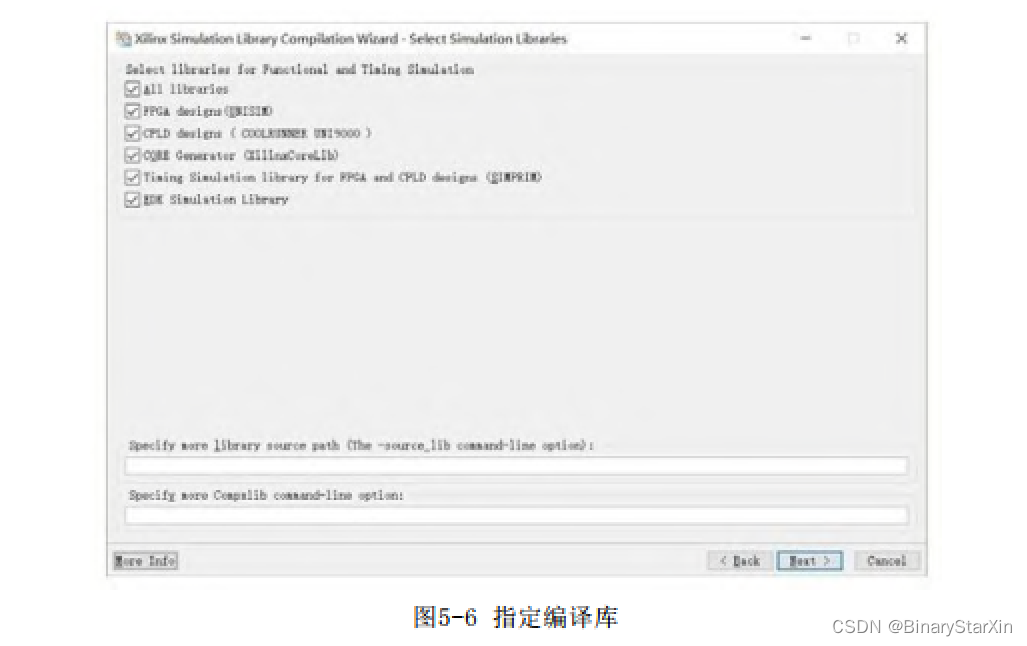

选择需要编译的器件,可以取消选择不用的器件,以便节省编译时间。接着单击“下一步”,指定编译库,如图5-6所示。

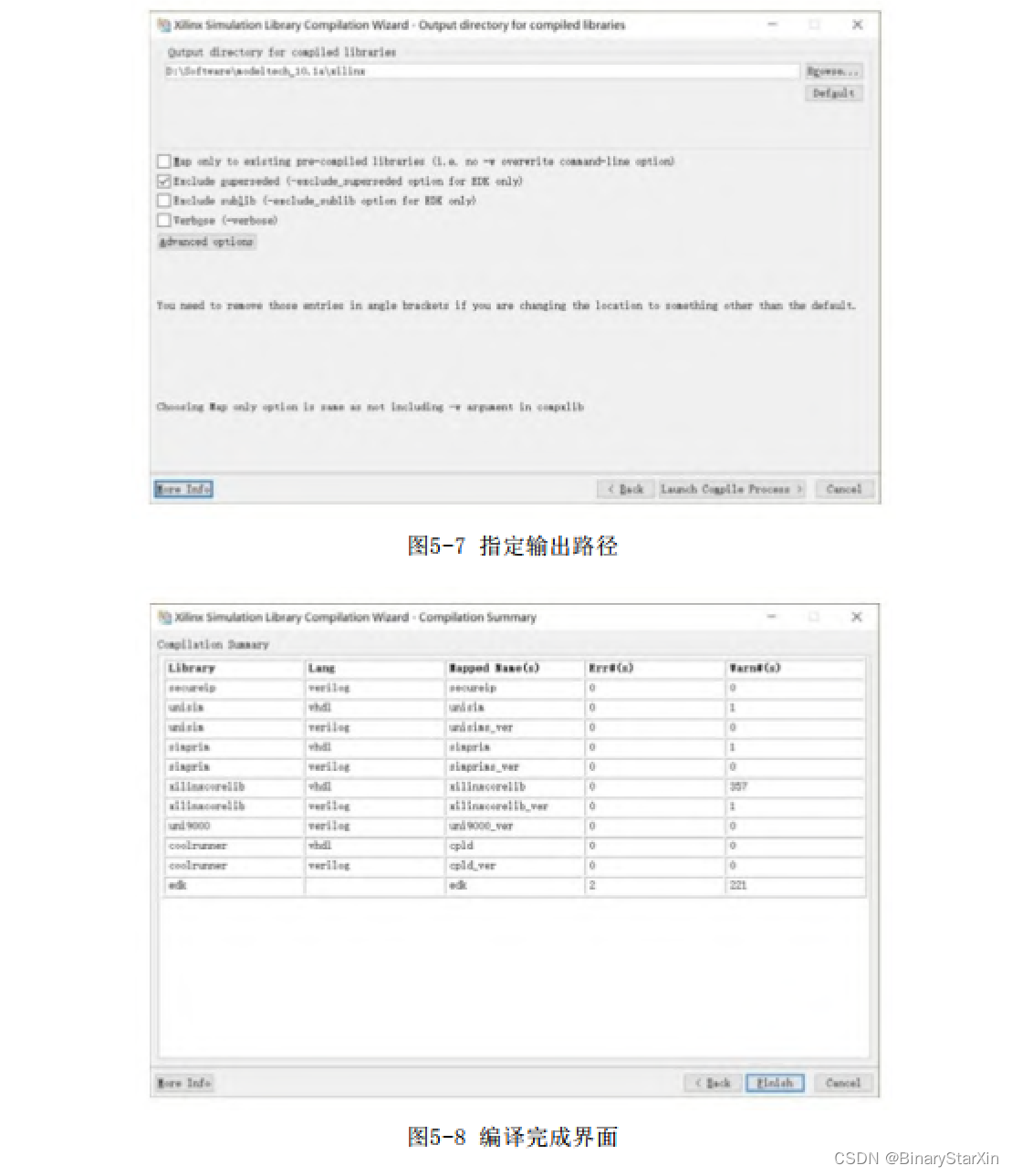

指定编译后的四个库,直接单击“下一步”,指定输出路径,如图5-7所示。

选择编译后的输出路径(我们选择将其保存到Modelsim的安装目录下的xinlinx文件夹),单击“Launch Compile Process”。接下来就是漫长的编译过程了。编译完成后的界面如图5-8所示。

将编译好的库路径添加到Modelsim安装路径下的modelsim.ini文件中,如下所示:

[Library]

secureip = $MODEL_TECH/../xilinx/secureip

unisim = $MODEL_TECH/../xilinx/unisim

unimacro = $MODEL_TECH/../xilinx/unimacro

unisims_ver = $MODEL_TECH/../xilinx/unisims_ver

unimacro_ver = $MODEL_TECH/../xilinx/unimacro_ver

simprim = $MODEL_TECH/../xilinx/simprim

simprims_ver = $MODEL_TECH/../xilinx/simprims_ver

xilinxcorelib = $MODEL_TECH/../xilinx/xilinxcorelib

xilinxcorelib_ver =

$MODEL_TECH/../xilinx/xilinxcorelib_ver

uni9000_ver = $MODEL_TECH/../xilinx/uni9000_ver

cpld = $MODEL_TECH/../xilinx/cpld

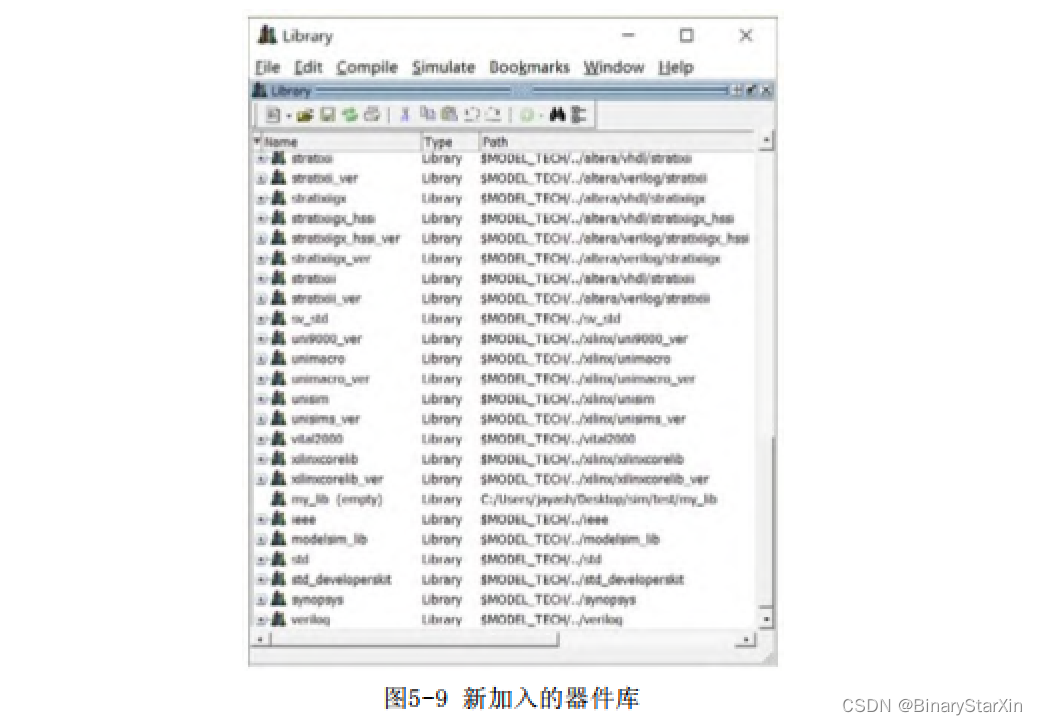

cpld_ver = $MODEL_TECH/../xilinx/cpld_ver重新启动Modelsim,即可出现新的Xilinx IP库,如图5-9所示。

Altera公司并没有提供相应的编译工具,因此,必须手动进行编译。Altera的仿真库存放目录为quartus\eda\sim_lib。编译过程首先需要新建库,并找到sim_lib文件夹的相应文件添加到指定库里面,进行编译,编译完成后将编译后的文件夹路径添加到modelsim.ini文件中去。下面以altera_mf_ver库为例来进行说明。

(1)首先新建一个工程。

( 2 )将 quartus\eda\sim_lib\altera_mf.v 添 加 到 工 程 中 并 编译。

(3)找到工程目录,work文件夹下即为编译好的库文件。可以将此文件夹重命名为altera_mf_ver,并将其复制到Modelsim的安装路径下的altera\verilog文件夹(新建)下面。

(4)在Modelsim中[Library]段下面添加如下部分:altera_mf_ver = $MODEL_TECH/../altera/verilog/altera_mf

(5)重新启动软件即可(需关闭当前工程)。鉴于整个过程比较繁琐,本书提供已经编译好的Altera的仿真库和器件库,可登录http://www.hxedu.com.cn下载。读者只需把整个文件夹复制到Modelsim安装目录下,并修改目录下的modelsim.ini文件即可。添加内容如下:

apex20k = $MODEL_TECH/../altera/vhdl/apex20k

apex20ke = $MODEL_TECH/../altera/vhdl/apex20ke

apexii = $MODEL_TECH/../altera/vhdl/apexii

220model = $MODEL_TECH/../altera/vhdl/220model

alt_vtl = $MODEL_TECH/../altera/vhdl/alt_vtl

flex6000 = $MODEL_TECH/../altera/vhdl/flex6000

flex10ke = $MODEL_TECH/../altera/vhdl/flex10ke

max = $MODEL_TECH/../altera/vhdl/max

maxii = $MODEL_TECH/../altera/vhdl/maxii

stratix = $MODEL_TECH/../altera/vhdl/stratix

stratixii = $MODEL_TECH/../altera/vhdl/stratixii

stratixiigx = $MODEL_TECH/../altera/vhdl/stratixiigx

cyclone = $MODEL_TECH/../altera/vhdl/cyclone

stratixiigx_hssi =

$MODEL_TECH/../altera/vhdl/stratixiigx_hssi

apex20k_ver = $MODEL_TECH/../altera/verilog/apex20k

apex20ke_ver = $MODEL_TECH/../altera/verilog/apex20ke

apexii_ver = $MODEL_TECH/../altera/verilog/apexii

altera_mf_ver = $MODEL_TECH/../altera/verilog/altera_mf

altera_ver = $MODEL_TECH/../altera/verilog/altera220model_ver = $MODEL_TECH/../altera/verilog/220model

alt_ver = $MODEL_TECH/../altera/verilog/alt_vtl

flex6000_ver = $MODEL_TECH/../altera/verilog/flex6000

flex10ke_ver = $MODEL_TECH/../altera/verilog/flex10ke

max_ver = $MODEL_TECH/../altera/verilog/max

maxii_ver = $MODEL_TECH/../altera/verilog/maxii

stratix_ver = $MODEL_TECH/../altera/verilog/stratix

stratixii_ver = $MODEL_TECH/../altera/verilog/stratixii

stratixiigx_ver =

$MODEL_TECH/../altera/verilog/stratixiigx

cyclone_ver = $MODEL_TECH/../altera/verilog/cyclone

cycloneii_ver = $MODEL_TECH/../altera/verilog/cycloneii

sgate_ver = $MODEL_TECH/../altera/verilog/sgate

stratixiigx_hssi_ver =

$MODEL_TECH/../altera/verilog/stratixiigx_hssi

stratixiii_ver = $MODEL_TECH/../altera/verilog/stratixiii

stratixiii = $MODEL_TECH/../altera/vhdl/stratixiii当然也可以根据需要屏蔽不需要的库(前面加分号即可)。

2.添加和编译设计文件

所用到的设计源文件如下:

//test.v

'timescale 1ns/1ns

module test(

clk,

rst_n,

din_a,

din_b,sum

);

parameter DW = 8;

input [DW-1:0]din_a;

input [DW-1:0]din_b;

input clk,rst_n;

output reg[DW:0]sum;

always @(posedge clk or negedge rst_n)

begin

if(~rst_n)

sum <= {DW+1{1'b0}};

else

sum <= #1 {1'b0,din_a} + {1'b0,din_b};

end

endmodule

测试用的例子如下:

//test_tb.v

'timescale 1ns/1ns

module test_tb;

parameter DW = 8;

reg clk;

reg rst_n;

reg [DW-1:0]din_a;

reg [DW-1:0]din_b;

wire [DW:0]sum;

test u0(

.clk(clk),.rst_n(rst_n),

.din_a(din_a),

.din_b(din_b),

.sum(sum)

);

defparam u0.DW = DW;

initial

begin: init

rst_n <= 1'b0;

#(50000);//reset the sysytem

rst_n <= 1'b1;//release the system

end

//clk generate : 25MHz

always @(rst_n or clk)

begin

if ((~(rst_n)) == 1'b1)

clk <= 1'b0;

else

clk <= #20 (~clk);

end

always @(posedge clk or negedge rst_n)

begin

if(~rst_n)

begin

din_a <= {DW{1'b0}};

din_b <= {DW{1'b0}};

endelse

begin

din_a <= #20 {$random} % {1'b1,{DW{1'b0}}};//

生成随机数

din_b <= #20 {$random} % {1'b1,{DW{1'b0}}};//

生成随机数

end

end

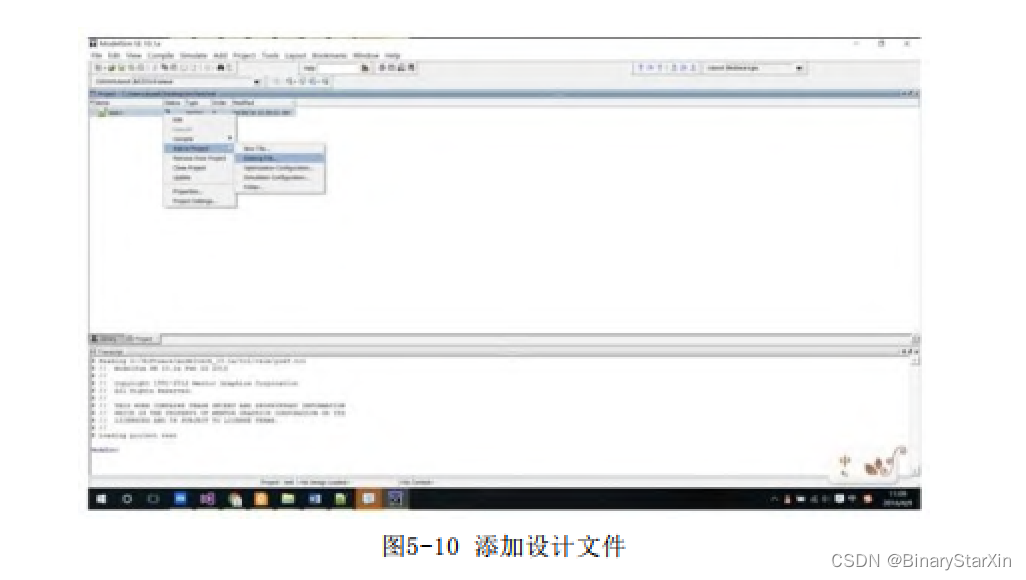

endmodule 在 project 窗 口 内 , 单 击 鼠 标 右 键 , 选 择 Add to Project->ExitingFile,选择写好的test.v和test_tb.v,如图5-10所示。单击右键进行编译即可。

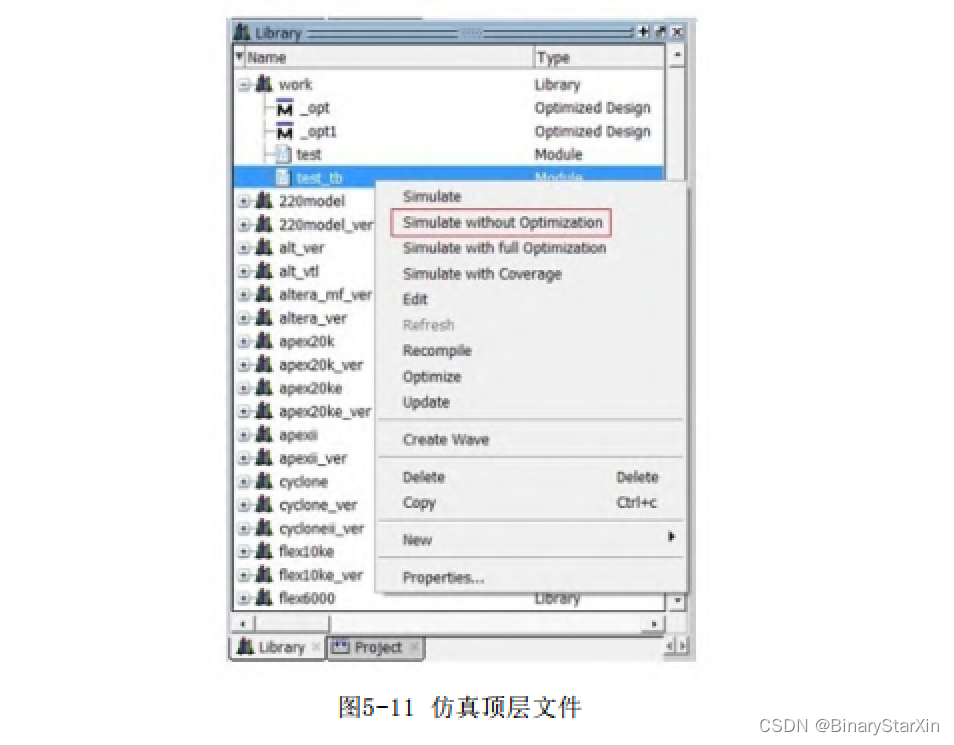

3.进行仿真

编 译 完 的 下 一 步 就 可 以 进 行 仿 真 了 , 在 library 窗 口 , 选 中test_tb,用右键选择Simulate without Optimization,即不进行优化,如图5-11所示。

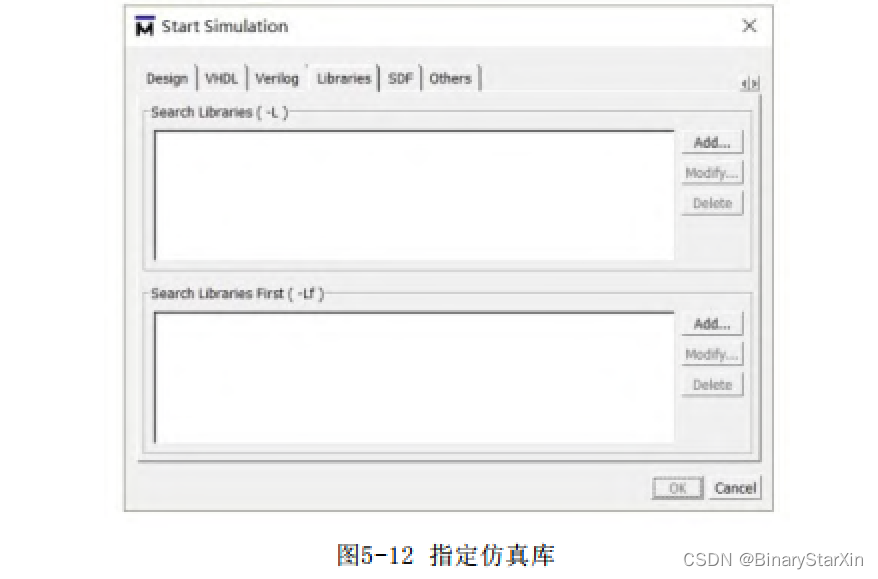

如果设计时用到了IP核或是外部库,就可能会报错而找不到设计单元,这时候需要指定仿真库(虽然本例不需要)。方法是单击菜单栏的Simulate->Start Simulation,如图5-12所示。

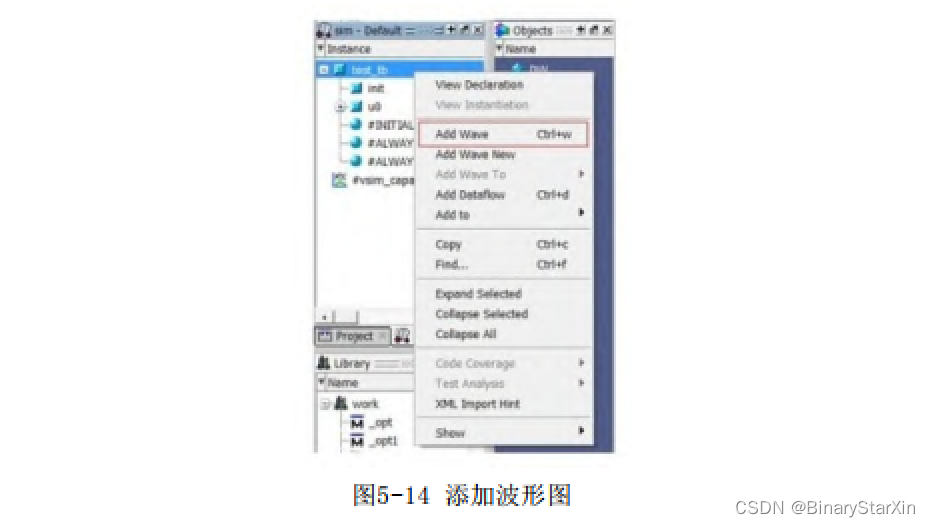

在Library选项卡添加需要用的库,例如需要用到altera_mf_ver库,如图5-13所示。然后选择设计单元test_tb进行仿真即可。加载成功后,在sim窗口选中test_tb设计实例,用右键选择Add

Wave,将顶层文件添加到Wave窗口,如图5-14所示。

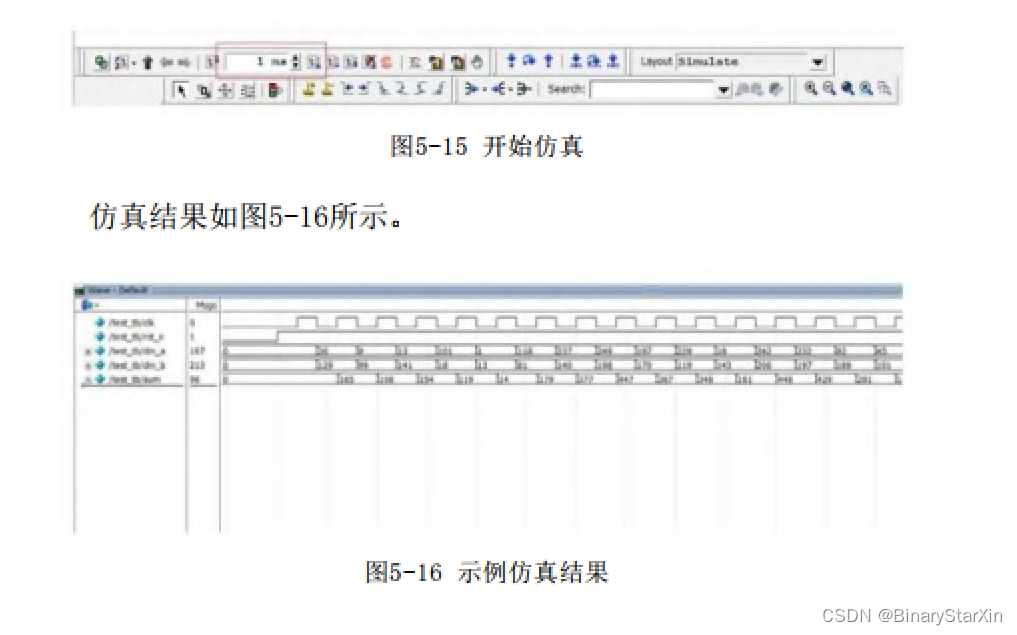

在工具栏设置仿真时间为1ms,并单击run按钮,如图5-15所示。

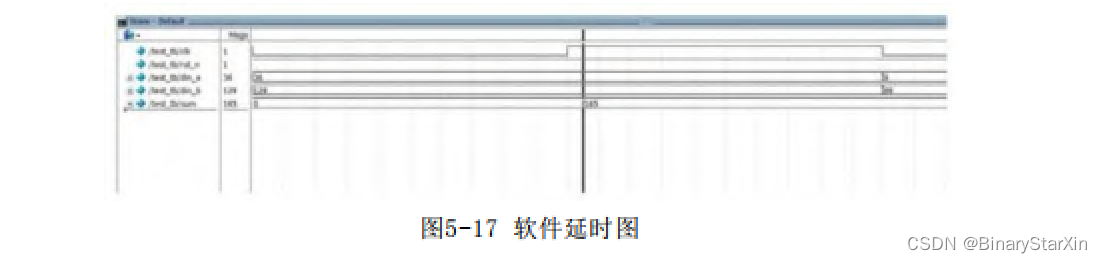

将上述仿真图局部放大,如图5-17所示。输出延时了clk上升沿1个ns,这是由于在代码设计的时候已经考虑了寄存器的工作时序。当然这个是不准确的,需要进行时序仿真来进行逼近。

5.1.3 使用脚本命令来加速仿真

Modelsim完美支持tcl脚本语言及批处理命令do文件。使用脚本文件可以大大减轻工作量,提高仿真效率。

gui界面操作起来非常繁琐,特别是在调试过程中,常常有一些重复性的工作。例如,在发现问题并修改代码后,重新进行仿真,这个用gui单步操作就会显得乏味和耗时。此外,在大型的设计中,要找出并添加一个特定的信号往往是令人崩溃的。在某些情况下,还可能只是对模块进行一些简单的激励测试,这时候写testbench就比较麻烦,可以用简单的测试激励脚本来实现。

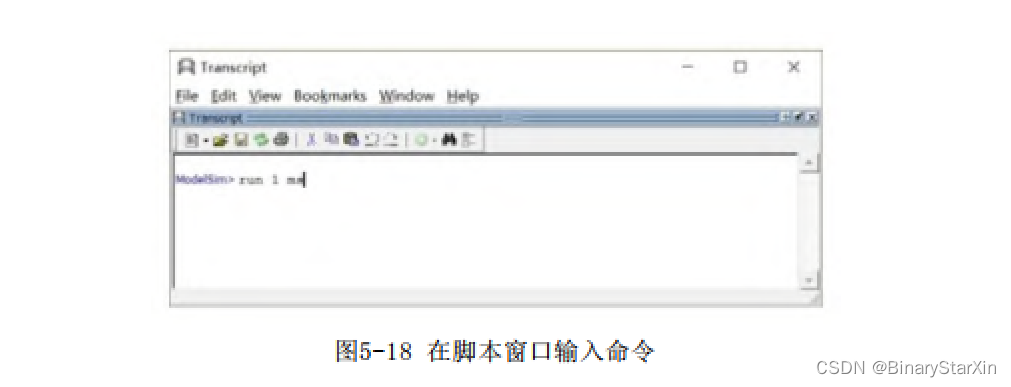

用户可以在脚本窗口来输入命令,如图5-18所示。

1.常用tcl脚本命令

下面将会列出一些常用的脚本命令。

#打开现有工程

project open C:/Users/jayash/Desktop/sim/ImageProcess

#新建一个库

vlib my_lib

#将其映射到work

vmap my_lib work

#删除指定库

vmap -del my_lib

#添加指定设计文件

project addfile src/verilog/test.v

#编译工程内的所有文件

project compileall

#编译指定verilog文件

vlog src/verilog/test.v

#编译指定vhdl文件,同时检查可综合性

vcom -check_synthesis src/video_cap.vhd

//仿真work库下面的test_tb实例,同时调用220model_ver库,不

进行任何优化,仿真分辨率1ns

vsim -t 1ns -L 220model_ver -gui -novopt work.test_tb

#取消warning,例如’x’,’u’,’z’信号的警告,对提高编译

速度很有帮助

set StdArithNoWarnings 1

#查看objects

view objects

#查看局部变量

view locals

#查看source

view source

#添加模块顶层所有信号到波形图

add wave *

#10进制无符号显示

radix unsigned

#16进制显示

radix hex

#重新进行仿真

restart

#开始仿真

run

#仿真指定时间

run 1 ms

#时钟激励50ns周期 占空比50%

force -repeat 50 clk 0 0,1 25

#指定信号置0

force rst_n 0

run 200 ns

#指定信号置0

force rst_n 1

#指定信号赋值

force din_a 123

force din_b 39

2.do文件

在实际情况下,通常会直接运行do文件。do文件是由一系列的顺序命令脚本,例如,打开工程,编译指定文件,添加指定信号,添加信号后开始执行。这对于很多重复的机械性工作的效率提升是非常之大的。

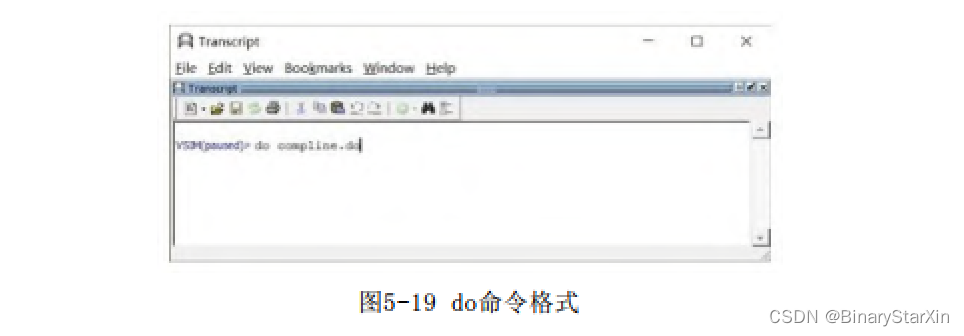

在Modelsim中执行do文件也是十分简单的,直接在控制台输入即可,如图5-19所示。

当然,图5-19所示命令要保证compline.do文件要放在当前工程的目录下,也可以利用绝对路径或相对路径执行do文件。除此之外,还可以利用windows平台下的批处理文件来执行do文

件,这样可以省去打开Modelsim和输入执行do文件命令的麻烦。

示例批处理文件内容如下所示:

vsim -do C:\Users\jayash\Desktop\sim\compline.do

将上述内容复制到txt文件,另存为bat格式的批处理文件,双击此文件,系统就会自动调用Modelsim并运行指定do文件。一个典型的do文件内容如下所示:

#切换至工程目录

cd C:/Users/jayash/Desktop/sim/

#打开工程

project open C:/Users/jayash/Desktop/sim/ImageProcess

#编译相关文件(一般情况下为频繁改动的文件)

vlog C:/Users/jayash/Desktop/sim/vht/img_process_tb.v

vlog C:/Users/jayash/Desktop/sim/src/verilog/canny.v

vlog C:/Users/jayash/Desktop/sim/ip/hist_buffer.v

#开始仿真

vsim -novopt -L altera_mf_ver work.img_process_tb

#添加顶层所有的信号

add wave *

#取消警告

set StdArithNoWarnings 1

#开始运行

Run

上述do文件是重新打开一个工程,编译指定文件后开始仿真。实

际中经常遇到的情况是:

发现问题->修改代码->重新编译->重新仿真同时,面对很多个信号,我们可能只对某一些信号感兴趣,而不是一股脑地添加所有信号,此时的do文件如下所示:

#退出当前仿真

quit -sim

#编译修改后的文件

vlog C:/Users/jayash/Desktop/sim/vht/img_process_tb.v

#开始仿真

vsim -novopt -L altera_mf_ver work.img_process_tb

#添加指定信号

add wave -position insertpoint \

sim:/img_process_tb/display_transform_operation/u0/clk

add wave -position insertpoint \

sim:/img_process_tb/display_transform_operation/u0/highCn

t

add wave -position insertpoint \

sim:/img_process_tb/display_transform_operation/u0/lowCnt

#取消警告

set StdArithNoWarnings 1

#运行18 ms

Run 18 ms

此外,不必每次都输入执行do文件命令,在脚本控制台直接按上键就会显示上一个执行过的命令。

7578

7578

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?