10.3.9 图片的插入与设置

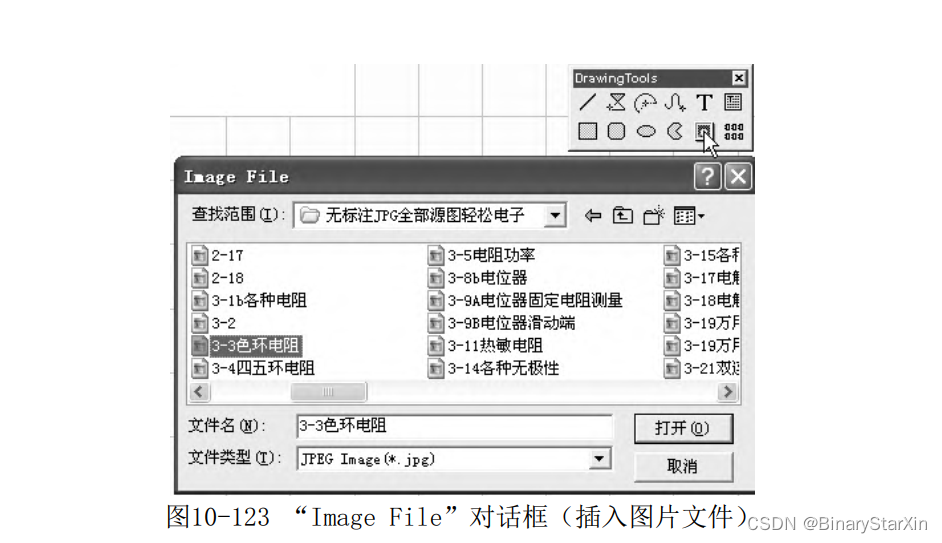

在电路设计图纸上不但可以插入说明文字,还可以插入图片。 (1)图片的插入 插入图片的操作过程如下。 ① 单击绘图工具栏中的按钮 ,或者选择“Place”→“Drawing Tools”→“Graphic”菜单命令,马上弹出“Image File”对话框, 如图10-123所示,在对话框中选择要插入的图片文件,再单击“打 开”按钮。

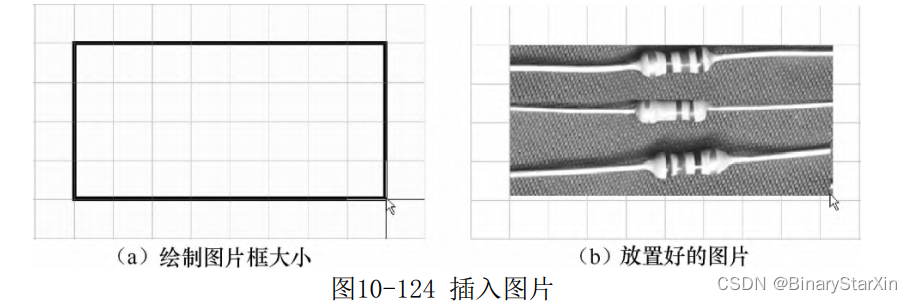

② 将光标移到图纸上某处单击,可确定图片框的左上角,如图10-124(a)所示。

③ 再将光标移到合适的位置,此时图片框大小也随光标移动而变化,单击,确定图片框的右下角,图片放置完成,此时会自动弹出“Image File”对话框,可以继续插入图片,如果不想继续插入图片,关闭对话框即可。放置好的图片如图10-124(b)所示。

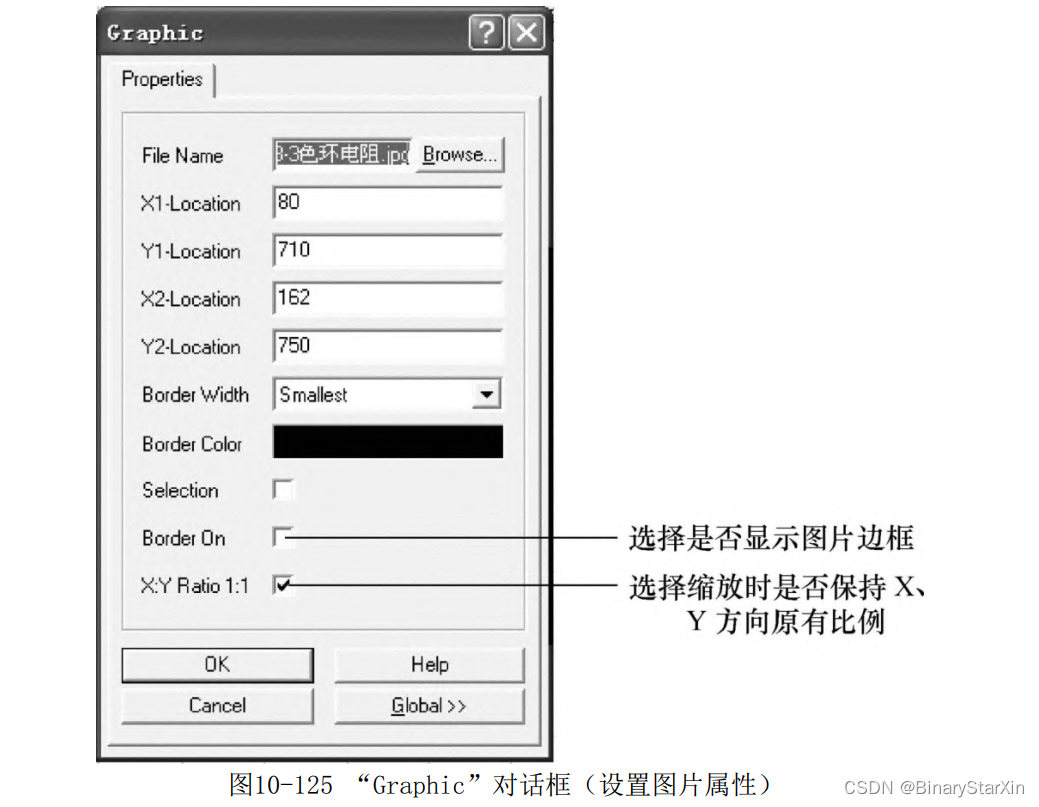

(2)图片属性的设置

进入图片属性设置界面有以下两种方法。

方法一:在放置图片时按“Tab”键,会弹出图10-125所示的“Graphic”对话框。

方法二:在已经放置好的图片上双击,也会弹出图10-125所示的 对话框。 在“Graphic”对话框中可以进行有关的设置,如果单击“File Name”(文件名)项右边的“Browse”按钮,就会弹出图10-123所示 的“Image File”对话框,可以选择要插入的图片文件。设置好有关 项后单击“OK”按钮即完成图片属性设置。如果要手动调整图片大小,可在图片上单击,此时在图片四周出 现控制点,拖动控制点就可以调节图片的大小,拖动整个图片移动就 可以改变图片的位置。

10.4 层次原理图的设计

在进行电路设计时,一些简单的电路可以设计在一张图纸上,但 对于一些复杂的电路图,一张图纸往往无法完成。解决这个问题的方 法就是将复杂的电路分成多个电路,再分别绘制在不同的图纸上,这 种方法称为层次原理图的设计。

10.4.1 主电路与子电路

层次原理图的设计思路是:首先把一个复杂的电路切分成几个功 能模块,然后将这几个功能模块电路分别绘制在不同的图纸上,再以 方块电路的形式将各功能模块电路的连接关系绘制在一张图纸上。这 里的功能模块电路称为子电路,表示各功能模块电路连接关系的方块 电路称为主电路。下面以 Protel 99 SE 自带的范例文件 Z80 Microprocessor.ddb 来说明主电路和子电路,该文件的存放地址是 C:\Program Files\Design Explorer 99SE\Examples。 打开“Z80 Microprocessor.ddb”数据库文件后,在设计管理器 的文件管理器中可以看到一个文件“Z80 Processor.prj”,如图10- 126所示。该文件即为主电路文件,又称项目文件,它的扩展名 为.prj。单击该文件前的“+”号后展开该文件,可以看见它包含有6 个子电路文件,子电路文件的扩展名是.sch。

图10-126 “Z80 Microprocessor.ddb”数据库文件的结构

单击文件管理器中的主电路文件“Z80 Processor.prj”,可以在 右边的窗口中看见该电路,如图10-127所示。从主电路中可以看出, 它由6个方块构成,每个方块表示一个子电路,另外,主电路还通过端 口和导线将子电路之间的连接关系表示出来。

在文件管理器中单击主电路文件“Z80 Processor.prj”下的子电 路文件“Memory.sch”,可以看见该电路,如图10-128所示。从图10- 128 中可以看出,子电路实际上就是电路原理图,它是通过 7个端口 与其他子电路进行连接的,在主电路的该子电路方块上也有这7个端 口。

设计管理器中的子电路文件“Serial Interface.sch”前有 “+”,表示它下面还有文件,展开后可以看见它下面还有一个子电路 “Serial Baud Clock.sch”。先打开“Serial Interface.sch”文 件,如图10-129所示。从图10-129中可以看出,该电路中除了有元件 外,还有一个方块,此方块就表示该电路下面还有子电路,此子电路 就是Serial Baud Clock.sch,打开“Serial Baud Clock.sch”子电 路文件,如图10-130所示。

综上所述,主电路以方块和端口的形式表示复杂电路的整体组成 结构和各子电路的连接关系,子电路下面还可以有子电路,各个子电 路由下到上连接起来就可以组成整个复杂电路。 10.4.2 由上向下设计层次原理图 由上向下的层次原理图设计思路是:先设计主电路,然后根据主 电路图设计子电路。设计时要求主电路文件和子电路文件都放在一个 文件夹中。 1.设计主电路 设计主电路的步骤如下。第1步:建立项目文件夹。 首先按照第9章介绍的方法建立一个数据库文件DZ3.ddb,然后在 该数据库文件中建立一个项目文件夹。 建立项目文件夹的过程是:打开“DZ3.ddb”数据库文件,再选择 “File”→“New”菜单命令,弹出“New Document”对话框,如图 10-131所示,选择“Document Folder”(文件夹)图标,再单击 “OK”按钮,就建立一个默认文件名为“Folder1”的文件夹,将该文 件夹名改为“Z80”。

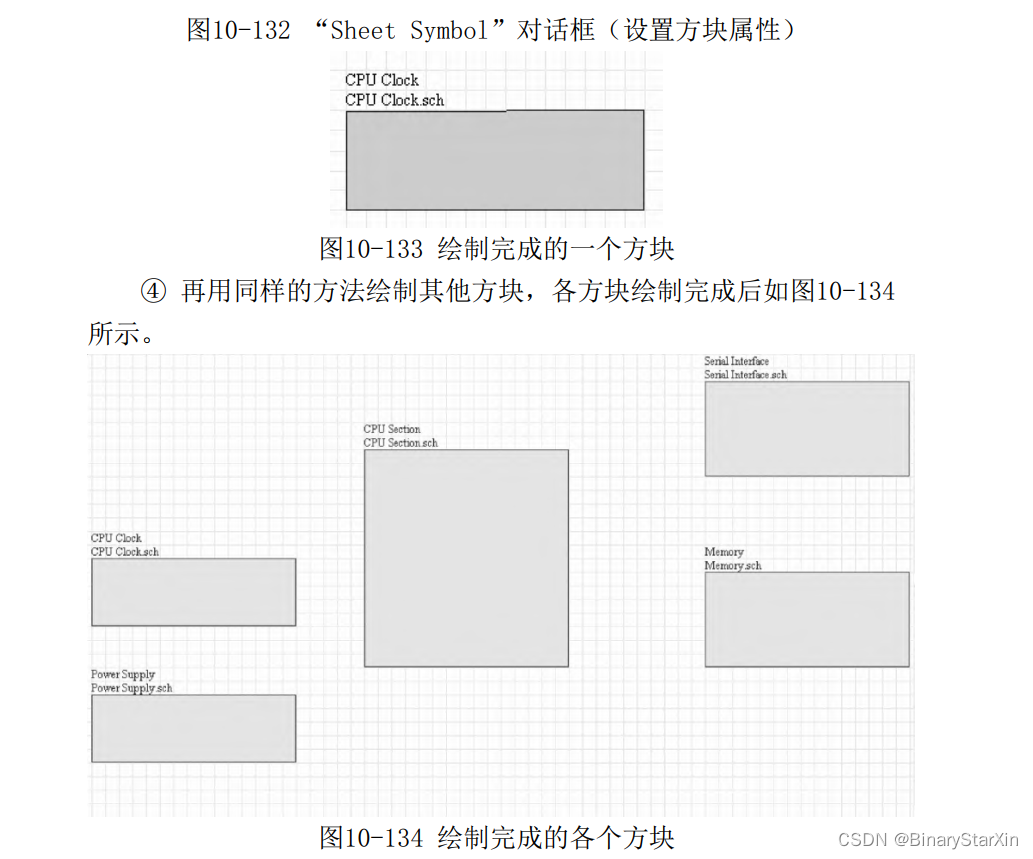

第2步:建立主电路文件。 建立主电路文件的过程是:打开“Z80”文件夹,再选择“File” →“New”菜单命令,弹出“New Document”对话框,选择 “Schematic Document Folder”图标,再单击“OK”按钮,就建立一 个默认文件名为“Sheet1.sch”的文件,将该文件名改为 “Z80.prj”。 第3步:绘制方块电路图。 绘制方块电路图的过程如下。① 打开“Z80.prj”文件,再单击绘图工具栏中的按钮 ,或者 选择“Place”→“Sheet Symbol”菜单命令,鼠标变成十字形状,并 且旁边跟随着一个方块。 ② 设置方块的属性。按Tab键,弹出“Sheet Symbol”对话框, 如图10-132所示。在该对话框中将“Filename”项设为“CPU Clock.sch”,将“Name”项设为“CPU Clock”,其他项保持默认 值,再单击“OK”按钮。 ③ 将光标移到图纸上适当的位置单击,确定方块的左上角,然后 将光标移到合适的位置单击,确定方块的右下角,图纸上就绘制了一 个方块,如图10-133所示,在方块旁边出现刚才设置的文件名“CPU Clock.sch”和方块名“CPU Clock”。

第4步:放置方块电路端口。 放置方块电路端口的过程如下。 ① 单击绘图工具栏中的按钮 ,或者选择“Place”→“Add Sheet Entry”菜单命令,鼠标变成十字形状。 ② 将光标移到方块上单击,出现一个浮动的方块电路端口随光标 移动,如图10-135所示。

③ 设置方块电路端口的属性:按Tab键,弹出“SheetEntry”对 话框,如图10-136所示。在该对话框中将“Name”项设为 “CPUCLK”,“I/O Type”(输入/输出类型)项设为“Output”, “Side”(端口放置处)项设为“Right”,“Style”(端口的样 式)项设为“Right”,其他项保持默认值,再单击“OK”按钮。 ④ 将光标移到方块上合适位置单击,就在方块上放置好一个端 口,如图10-137所示。再用同样的方法放置其他的端口,各方块上的 端口放置完成后如图10-138所示。

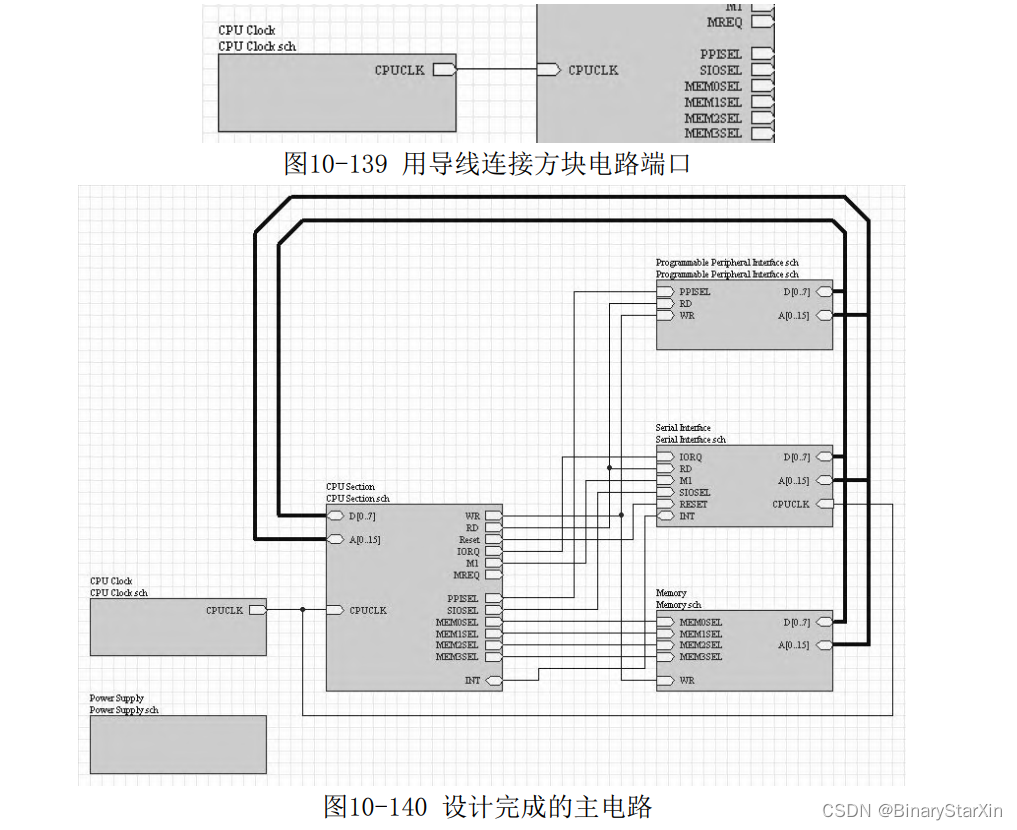

第5步:连接方块电路。将所有的方块电路和方块端口放置好后,再用导线和总线将各方 块电路的端口连接起来,如图10-139所示。将主电路中各个端口连接 好后就完成了主电路的设计,设计完成的主电路如图10-140所示。

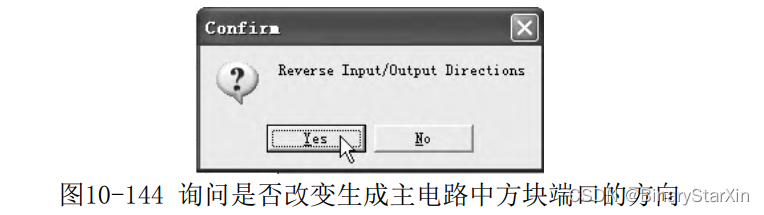

2.设计子电路 主电路设计完成后,可以利用主电路的方块自动生成相应的子电 路文件,不需要重新建立。子电路具体的设计过程如下。① 在主电路中选择“Design”→“Create Sheet From Symbol” 菜单命令,鼠标变成光标状。 ② 将光标移到需要生成子电路的方块“CPU Section”上单击, 如图10-141(a)所示,马上弹出图10-141(b)所示的对话框,询问 是否改变生成子电路中端口的方向。如果单击“Yes”按钮,生成的子 电路中的端口方向与主电路方块中的端口方向相反,即主电路的方块 中端口为输出,子电路相应的端口将变为输入;如果单击“No”按 钮,两者方向相同。这里单击“No”按钮。

③ 单击“No”按钮后,马上在文件管理器的主电路文件下自动生 成“CPU Section.sch”子电路文件,同时在右边的工作窗口中可以看 见图纸上有主电路的CPU Section方块上所有的端口,如图10-142所 示。

④ 用绘制电路原理图的方法在子电路的端口基础上绘制出具体的 子电路。 重复上述过程,设计出其他的子电路,这样就完成了复杂电路的 层次原理图设计。 10.4.3 由下向上设计层次原理图 由下向上的层次原理图设计思路是:先设计好各个子电路,然后 根据子电路图生成主电路。设计时同样要求主电路文件和子电路文件 都放在一个文件夹中。 1.设计子电路 设计子电路的步骤如下。 ① 建立子电路文件。首先建立一个数据库文件“DZ4.ddb”,然 后在该数据库文件中建立一个项目文件夹“Z80”,再在Z80文件夹中 建立一个默认文件名为“Sheet1.sch”的文件,将该文件名改为“CPU Clock.sch”。具体操作过程如前所述。② 用设计电路原理图的方法绘制出CPU Clock.sch文件的原理 图。 再用同样的方法设计出其他子电路原理图。 2.设计主电路 设计主电路的过程如下。 ① 建立主电路文件。在数据库文件 DZ4.ddb 的 Z80 文件夹中建 立一个文件名为“Z80.prj”的文件。 ② 打开“Z80.prj”文件,再选择“Design”→“Create Symbol From Sheet”菜单命令,出现一个对话框,如图10-143所示,从中选 择需要在主电路中转换成方块的电路;再单击“OK”按钮,又弹出一 个对话框,如图10-144所示,询问是否改变生成主电路中方块端口的 方向。这里单击“Yes”按钮,鼠标旁出现十字光标,并且旁边跟随着 一个方块。

③ 在图纸上合适的位置单击,方块就放置在图纸上,方块上同时带有端口,如图10-145所示。

④ 用同样的方法在主电路上放置其他子电路的方块图,所有的方 块放置好,再用导线和总线将各方块连接好。这样,一个由下向上的 层次原理图就设计完成了。

10.5 原理图报表的生成

为了实现印制电路板的自动布线和满足生产工艺的需要,Protel 99 SE提供了根据原理图生成各种报表的功能。

10.5.1 ERC报表的生成

ERC意为电气规则检查。在电路设计中可能会出现一些设计疏漏和 错误,例如电源VCC与接地GND短路、电源VCC没有与电路连接等,利用 Protel 99 SE提供的ERC功能来检测设计的电路,然后生成ERC报表, 可以找出一些设计问题。 1.电气规则检查(ERC) 电气规则检查(ERC)的操作过程如下。 打开需检查的原理图文件(如YL1.Sch),再选择“Tools” →“ERC”菜单命令,或者在图纸上双击鼠标右键,在弹出的快捷菜单 中选择“ERC”命令,马上会出现图10-146所示的“Setup Electrical Rule Check”对话框。在该对话框中有两个选项卡,“Setup”选项卡 的内容如图10-146所示,各项说明见图标注;如果切换到“Rule Matrix”选项卡,对话框呈现的内容如图10-147所示。

在图10-147所示的“Rule Matrix”选项卡中可以定义各种引脚、 输入/输出端口以及电路图的出入口之间的连接状态是否有Error(错 误)、Warning(警告)等级的电气冲突。 在图10-147中有一个正方形的区域,称之为电气规则矩阵。矩阵 中以彩色方块表示检查结果,绿色方块表示这种连接方式不会产生错误或警告信息(例如某一个输入引脚与另一个输出引脚相连接),黄 色方块表示这种连接会产生警告信息(例如输入引脚未连接),红色 方块表示这种连接方式会产生错误信息(例如两个输出引脚相连 接)。 这里的错误是指电路中有严重的违反电路原理的连线情况,例如 电源VCC与接地GND相连;而警告是指某些轻微违反电路原理的连线情 况,但因为系统无法确定它们是否真正有错误,所以用警告表示。 彩色方块矩阵是以交叉接触的形式读入的,例如要查看输入引脚 与输出引脚的检查条件,观察矩阵左边的“Input Pin”这一行和矩阵 上方的“Output Pin”这一列之间的交叉点即可。交叉点的彩色方块 表示检查结果。 交叉点的检查条件可以修改,在矩阵中的方块上单击可在绿、 黄、红3种颜色中切换。 2.ERC报表的生成 将“Setup Electrical Rule Check”对话框中有关项设置好后 (一般情况下可不用设置,保持默认值),再单击“OK”按钮,系统 就开始对电路图进行电气检查,检查后会自动生成ERC报表文件,如图 10-148所示,因为检查的原理图文件名为“YL1.Sch”,生成的 ERC 报表文件名自动为“YL1.ERC”。

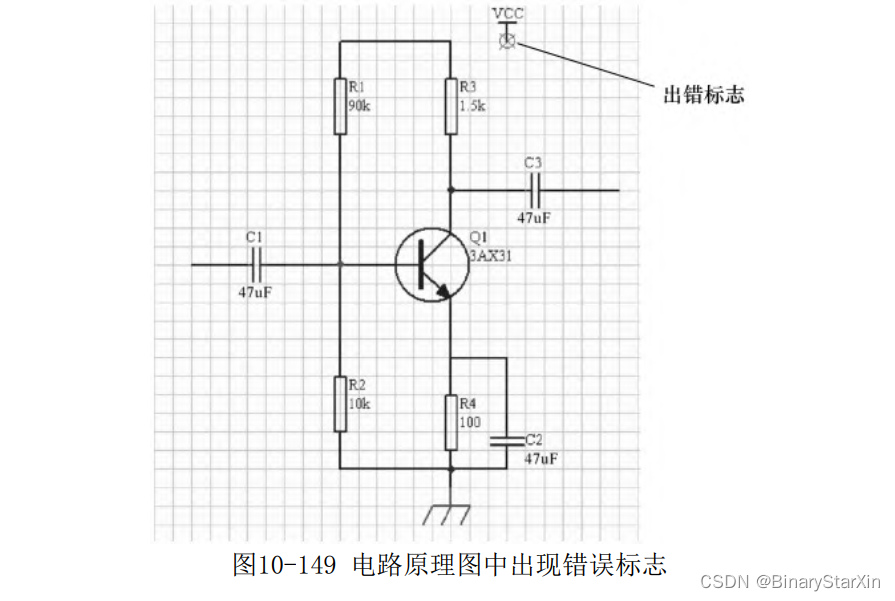

由于YL1.Sch电路中的电源符号未与电路连接,ERC后,电路中的 电源符号处出现红色带叉圆圈,以示该处有错误,如图10-149所示, 而在ERC报表文件中也可以找到相应的错误报告信息。

2490

2490

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?