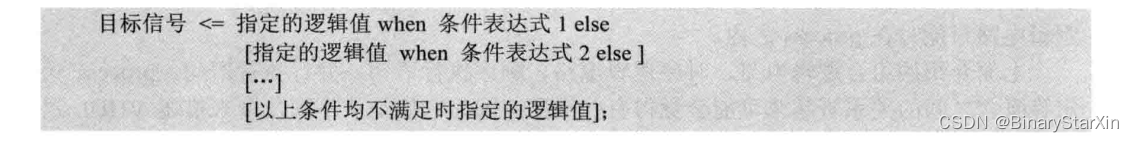

2. when-else 语句

when-else语句是并发执行语句,只能写在process之外,综合成组合逻辑电路。首先来看看语句的语法。

when-else语句的语法意义很明确,语句依次判断各条件表达式的值,当某条件表达式为真时,将指定逻辑值赋值给目标信号,同时语句终止执行,不再对后面的条件进行判断。所以,语句的条件表达式有优先级,条件表达式越靠前优先级越高。

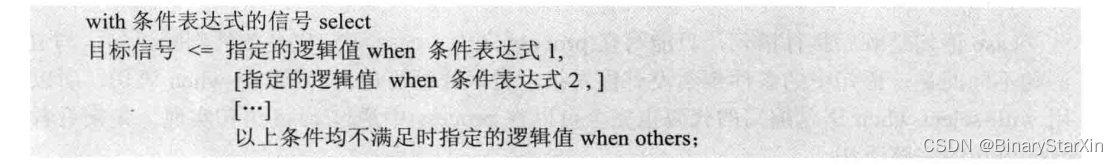

3.with-select-when 语句。

with-select-when语句是并发执行语句,只能写在process之外,综合成组合逻辑电路首先来看看语句的语法。

whith-select-when语句的语法意义很明确,语句依次判断各条件表达式的值,当某条件表达式值为真时,将指定的逻辑值指定给目标信号。与when-else语句不同的是,条件表达式之间没有优先级,也就是说即使第一个条件表达式的值为真,语句依然会继续往下执行,直到语句结束。值得注意的是,在使用这条语句时,最后的whenothers指所有条件均不满足时目标信号的逻辑值。从语句的语义上分析,这条语句非常适合用来描述译码器或不具有优先级的多路选择器电路。

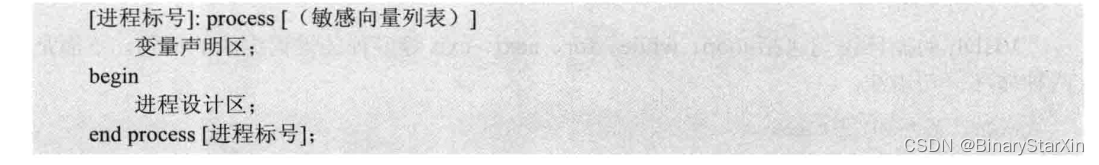

4.process 的语法结构

process(进程)是VHDL语言中最为重要的语法结构,所有时序逻辑电路均须使用process结构,本节前面介绍的几种语句也完全可以通过process的语法结构来实现。process的基本语法结构如下。

保留字process之前的进程标号可选,但如果设置了进程标号,在process结束时也必须写上进程标号。进程标号只是用来对process设置一个名称,本身不参与编译或仿真。敏感向量是指触发 process内部语句动作的信号,只有当敏感向量列表中的信号逻辑状态发生改变时,才能触发 process的内部语句执行。只有当进程设计区中出现wait语句时,不需要设置敏感向量,否则必须设置至少一个敏感向量信号。wait语句本身就决定了process内部程序的触发条件,所以不设置敏感信号。wait语句将在稍后介绍。

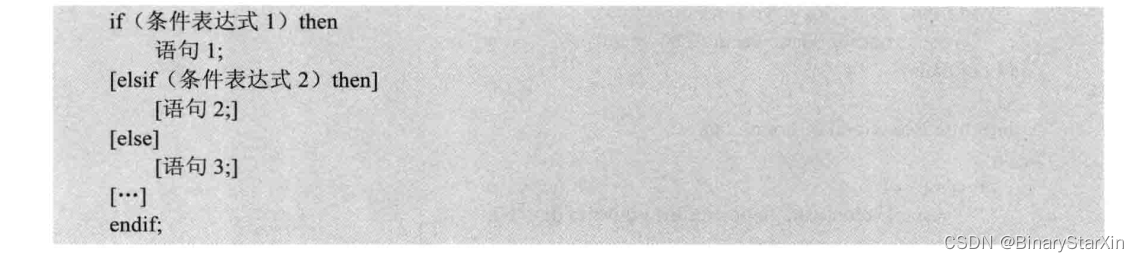

5.if 语句

if语句是顺序执行语句,只能写在process之内。if语句是 VHDL语言中使用最重要最广泛的语句,if语句的完整语法如下。

本书前面已多次使用到if语句,其语义十分明确,当相应条件成立时就执行条件下的语句。需要注意的一点是,if语句是有优先级的,这与并行执行语句when-else 相似。

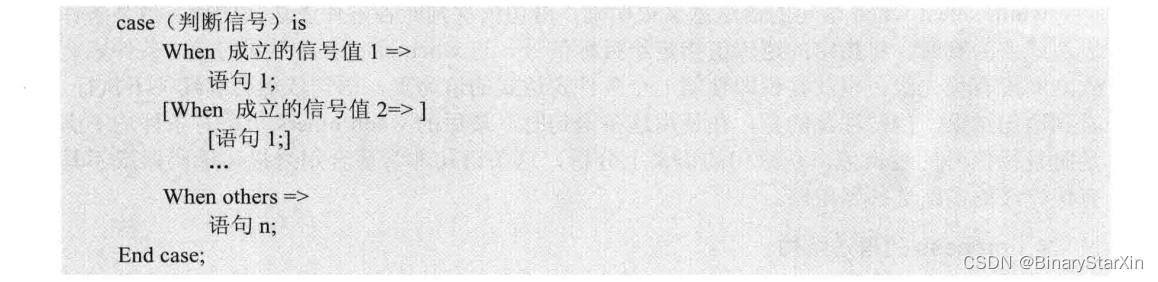

6.case 语句

case语句是顺序执行语句,只能写在process之内。case语句也是条件判断语句,与if语句不同的是,语句中的条件判断没有优先级,类似并行语句with-select-when语句,所以用 with-select-when语句编写的代码也完全可以在 process 中通过 case 语句实现。先来看看case 语句的完整语法。

case语句中的成立信号值必须包含条件成立信号的所有取值,当要求when others 后不必执行任何语句时,可用语句null 代替。null 表示没有任何操作,只能用在 process 语法结构中。

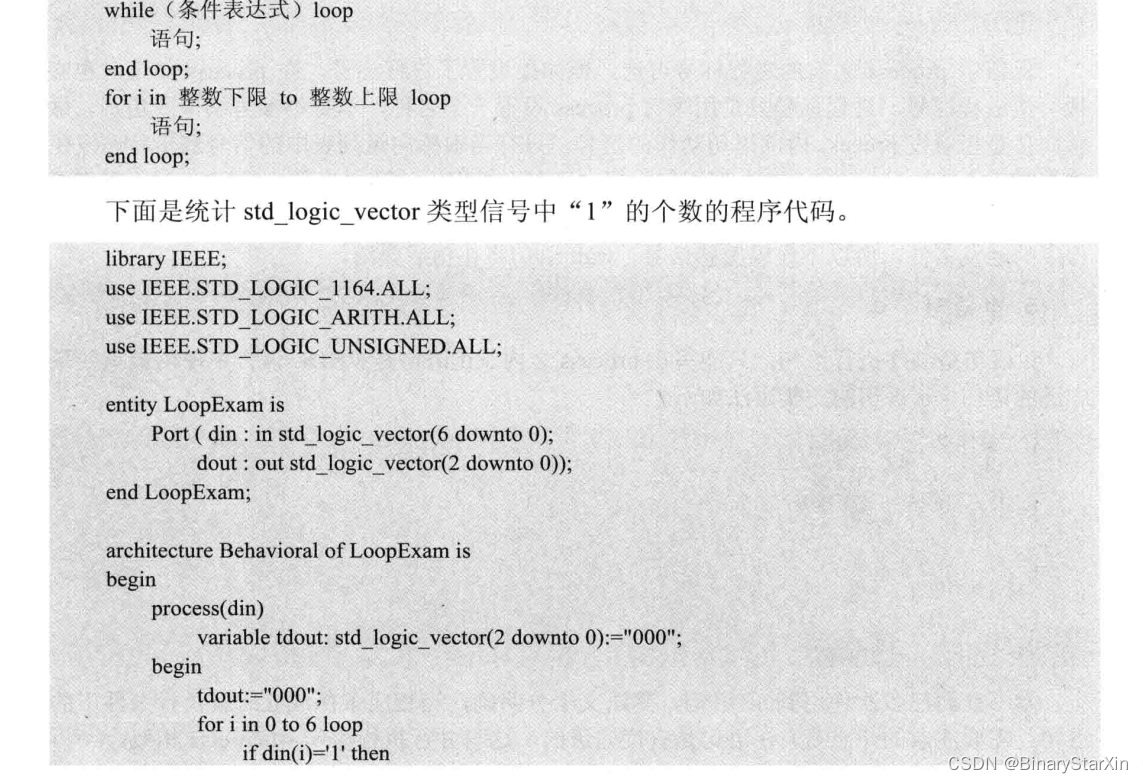

7.循环语句

VHDL 的循环语句包括 loop、while、for、next、exit 等多种关键词组成的语句。下面是两种循环语句语法。

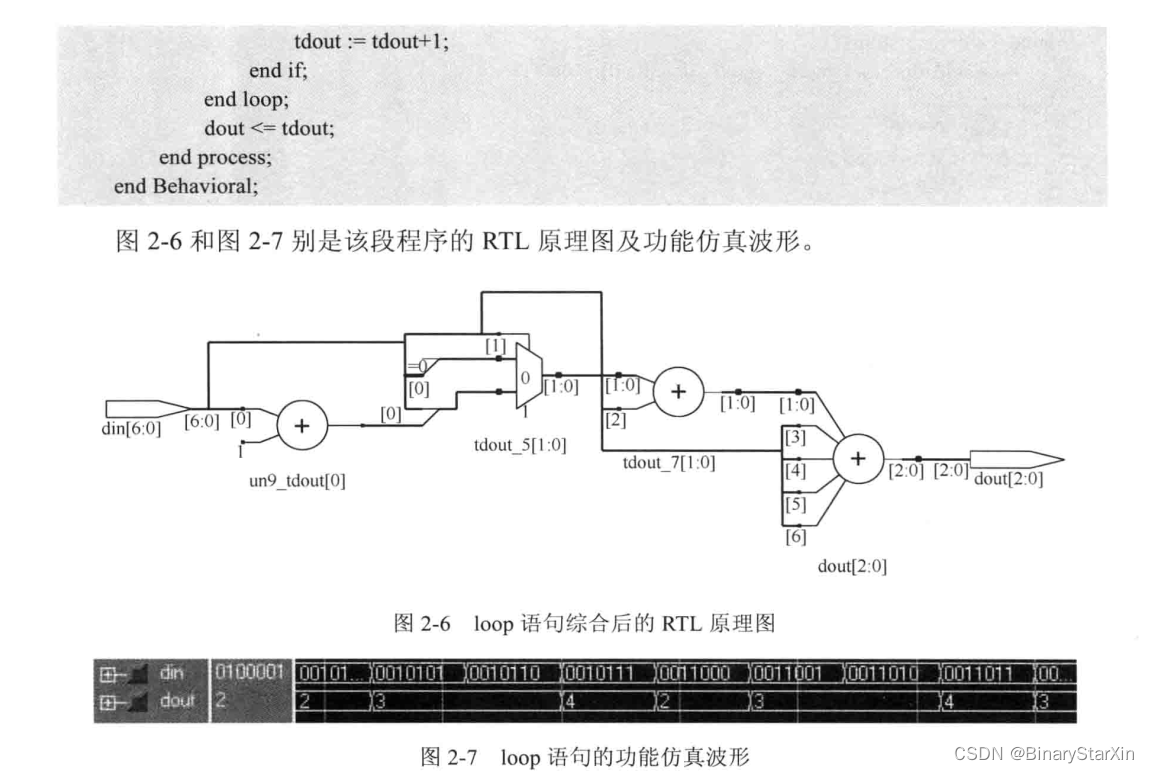

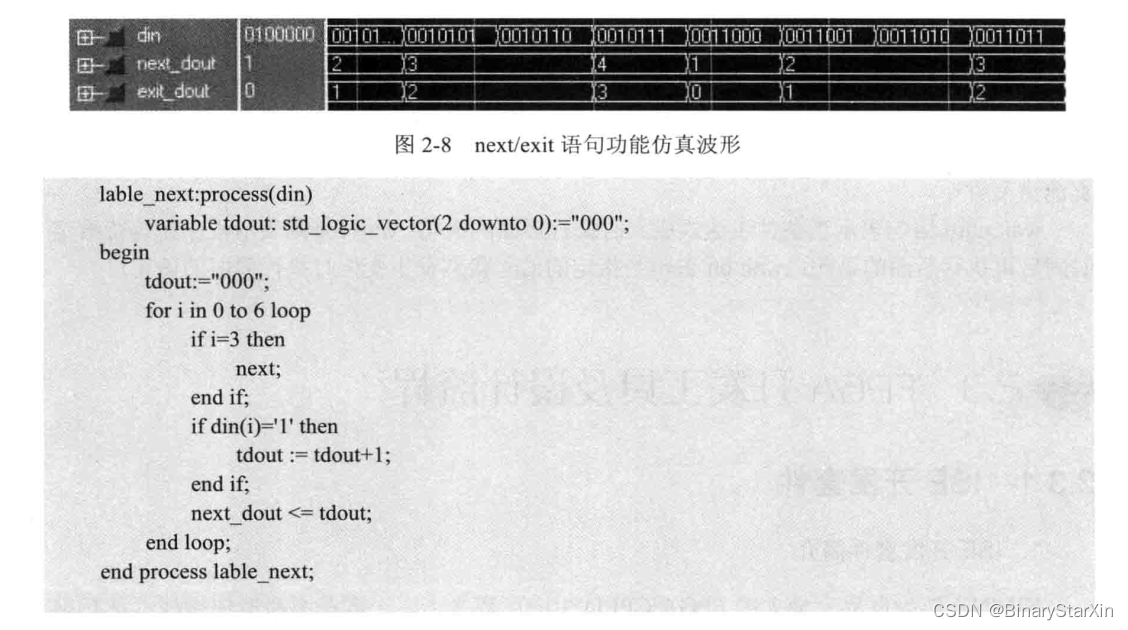

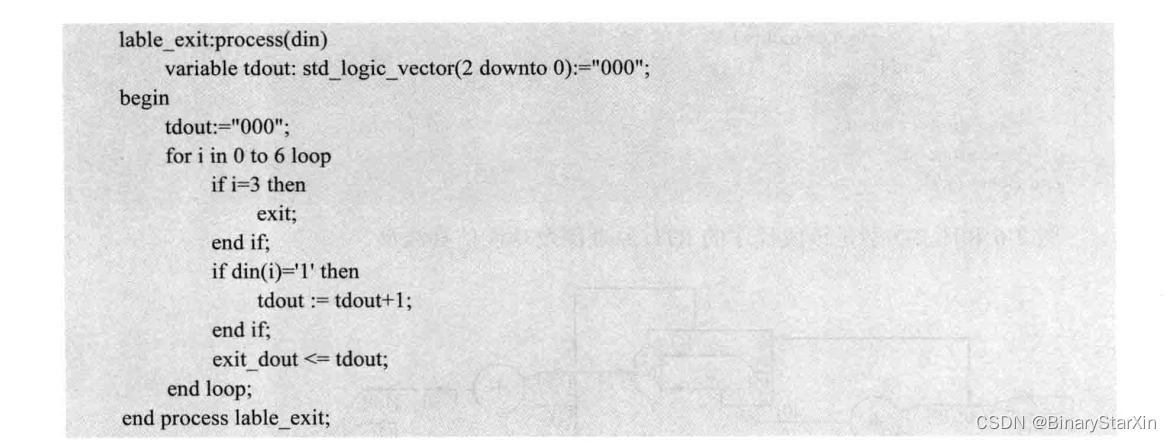

循环语句中,当程序执行到next语句时,直接跳至下一次循环入口点;当程序执行到exit语句时,直接跳出当前的循环语句。请读者分析下面两段程序的代码。图2-8为相应代码的功能仿真波形。

循环语句中,当程序执行到next语句时,直接跳至下一次循环入口点;当程序执行到exit语句时,直接跳出当前的循环语句。请读者分析下面两段程序的代码。图2-8为相应代码的功能仿真波形。

在 lable next进程中,当执行第4次循环(i=3)时,因 next 语句的影响,程序直接跳至下一次循环,所在程序直接跳过了 din(3)的状态,只统计了除din(3)外其余 din 数据中为1的比特总数;在1ableexit中,当执行第4次循环时,因exit语句的影响,程序直接跳出整个循环,所以程序只统计了din(0)、din(1)、din(2)这3 位数据中为“1”的比特总数。

8.wait 语句

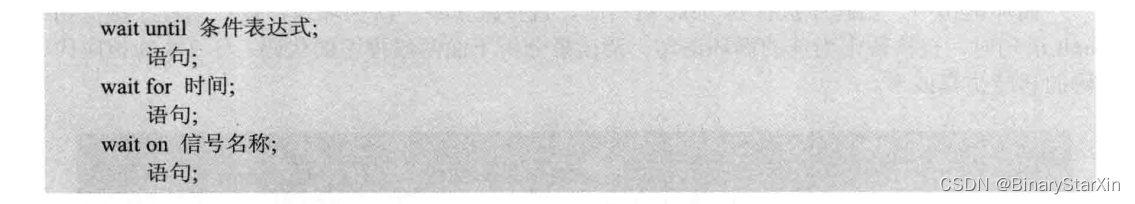

wait语句是顺序执行语句,只能写在process之内。wait语句有3种形式:wait until.wait for、wait on。其中只有 wait until 可以综合成电路,其他两种形式均无法综合成电路,只能在仿真测试文件中使用。它们的语法分别如下。

由于 wait语句的优先级很高,wait语句必须是紧跟process后的第一条语句。如果process中有 wait 语句,则不能有敏感信号。waiton及 wait for 语句不能综合成电路,只能用在仿真测试文件中。

wait until 语句表示当条件表达式成立时执行后面的语句;wait for 则表示程序在等待给定时间后再执行后面的语句:waiton表示当指定的信号状态发生变化时执行后面的语句。

2.3FPGA 开发工具及设计流程

2.3.1 ISE 开发套件

1.ISE 开发套件简介

XILINX作为世界上最大的FPGA/CPLD生产厂商之一,一直在不断地依靠技术革新推动着 FPGA/CPLD技术的发展,其推出的开发软件也不断升级换代,由早期的Fundation系列逐步发展到日趋成熟的ISE(Integrated Sofware Environment,集成软件环境)系列。ISE是XILINX FPGA/CPLD的综合性集成设计平台,该平台集成了从设计输入、仿真、逻辑综合、布局布线与实现、时序分析、程序下载与配置、功耗分析等几乎所有设计流程所需的工具,仅利用ISE即可完成整个FPGA/CPLD的开发过程。

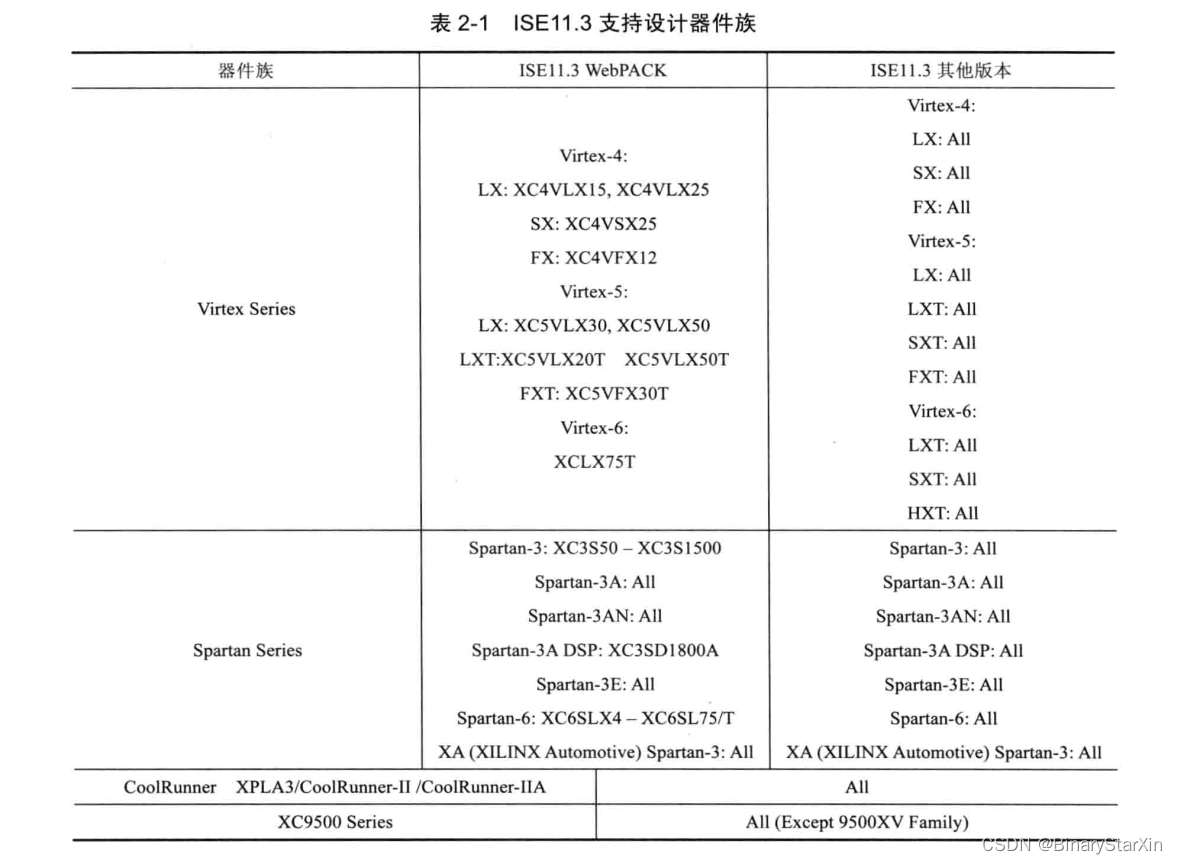

除ISE外,XILINX公司还推出了片内逻辑分析仪工具ChipScopePro、IP Core 系列工具(IP Capture、Core Generator、Updates Installer)、SOPC 集成开发套件 EDK(EmbeddedDevelopment Kit)、DSP 开发工具 System Generator等。ISE的更新速度很快,新版软件除在不断增强功能外,另外一个主要因素是适应公司不断推出的新产品系列的设计与实现,如[SE11.3与ISE11.1相比,增加了对Spartan6及 Virtex6系列器件的支持。表 2-1是ISE11.3支持的器件表。

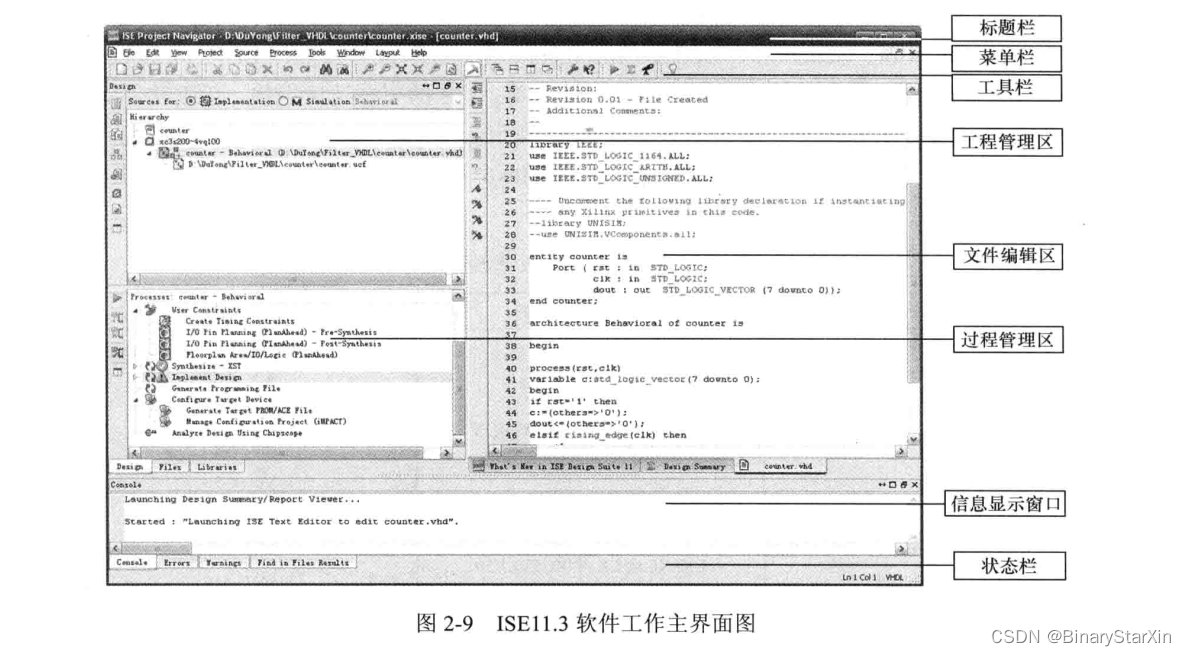

从表 2-1中也可以看出,ISE11.3 不支持 XILIXN 公司的 Virtex-4 以前的 Virtex系列器件,用户如需设计XILINX公司早期的器件,需要安装使用早期的ISE版本。随着软件版本不断更新,软件本身的“体积”也变得越来越庞大(ISE7.x为1.5GB,ISE11.x已超过5 GB),对微机的配置要求也越来越高。ISE版本虽然升级很快,但软件界面及设计流程变化不大,读者熟悉了一个版本后,再掌握其他软件版本是一件十分容易的事。ISE推荐的系统配置与设计所选的芯片型号有关,当设计的芯片规模较大、设计复杂且时序要求高时,系统配置低的计算机将无法完成完整的设计流程。XILINX公司推荐的配置较高,有的甚至需要配置工作站。为了提高综合、实现过程中的速度,除提高系统CPU工作性能、主板及硬盘工作速度外,最为主要的是要提高系统的内存配置。图2-9是ISE11.3软件工作的主界面图。

ISE 的主界面由标题栏、菜单栏、工具栏、工程管理区、文件编辑区、过程管理区、信息显示窗口,以及状态栏等组成。

(1)标题栏:主要显示当前工程的名称和当前打开的文件名称。

(2)菜单栏:主要包括文件(File)、编辑(Edit)、视图(View)、工程(Project)、源文件(Source)、操作(Process)、窗口(Window)和帮助(Help)8个下拉菜单。其使用方法和常用的 Windows 软件类似。

(3)工具栏:主要包含了常用命令的快捷按钮。灵活运用工具栏可以极大地方便用户

在ISE中的操作。在工程管理中,工具栏的应用十分频繁。

(4)工程管理区:提供了工程以及相关文件的显示和管理功能,主要包括源文件视(Source View)、快照视图(Snapshot View)和库视图(Library View)。其中源文件视图比较常用,显示了工程中用户产生的库文件内容。

(5)文件编辑区:这个窗口区域提供了源代码的编辑功能。

(6)过程管理区:本窗口显示的内容取决于工程管理区中所选定的文件类型。窗口显示的内容多是FPGA设计流程中需要进行的相关操作,包括设计输入、综合、仿真、实现和生成配置文件等。对某个文件进行了相应的处理后,在处理步骤的前面会出现一个图标来表示该步骤的状态。

(7)状态栏:显示相关命令和操作信息。

2.ISE11 的新特性

赛灵思公司于2009年4月28日宣布正式推出了ISE设计套件11.1版本(ISEDesign Suite11.1),同年9月16日又正式推出了11.3版本。这一FPGA 设计解决方案在为嵌入式、DSP和逻辑设计人员提供FPGA设计工具和IP产品方面确立了业界新标准。在业界率先为逻辑、数字信号处理、嵌入式处理,以及系统级设计提供了完全可互操作的专用设计流程和工具配置。

在过去的几年里,赛灵思的主要客户是逻辑设计人员,他们是精通硬件设计和硬件描述语言的电子工程师。不过,随着各代 Virtex和 SpartanFPGA产品的推出,逻辑单元、MPU和DSP等嵌入式软硬件处理器呈指数级增长。在此情况下,赛灵思的客户中迅速增加了大量嵌入式软硬件工程师、DSP算法开发人员和系统集成人员,他们都是使用赛灵思的器件

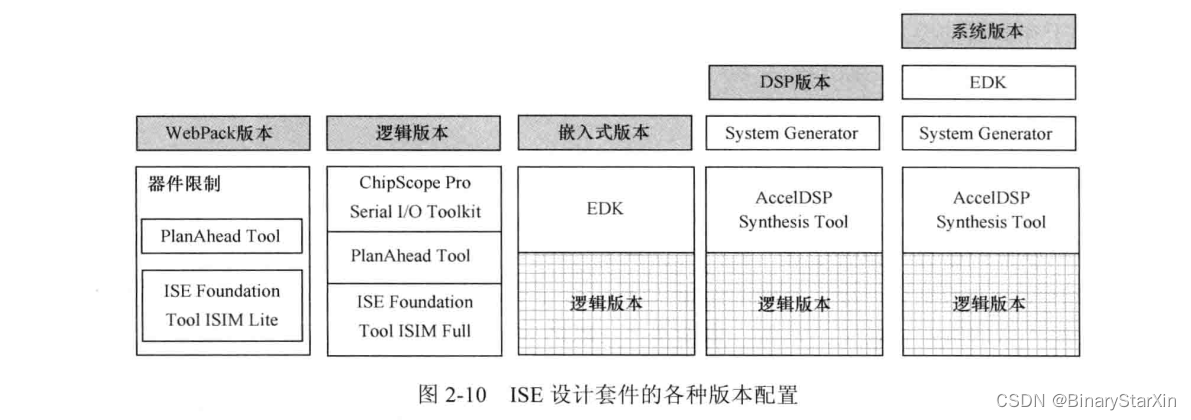

来构建高级片上系统。FPGA已从简单的粘接逻辑发展成为可编程系统的核心。随着高级FPGA架构的不断发展及其复杂程度的不断提高,因此需要更高级的设计技术和优化的算法来满足人们对更高工作效率、更高性能、更低功耗以及众多新标准的需求。为此,赛灵思公司推出的ISE设计套件创新性地提供了四个针对特定领域而优化的配置版本:逻辑版本(LogicEdition)、DSP版本(DSPEdition)、嵌入式版本(Embedded Edition)和系统版本(System Edition),如图 2-10所示。

ISE WebPack 版本是 XILINX公司推出的一款免费软件,与其他版本相比,这个版本的软件仅支持一些规模较小的器件。ISE的每一版本都提供了完整的FPGA设计流程,并且专门针对特定的用户群体和特定领域的设计方法及设计环境要求进行了优化,从而使设计人员能够将更多精力集中于创建增值的、具有竞争力的差异化产品和应用。同时,针对与目标设计平台一起提供的基础级FPGA专用工具、技术以及P组件等,ISE设计套件11版本还为其提供了新功能以及易于使用的增强特性。赛灵思公司随其Virtex-6和Spartan-6 FPGA系列器件而推出的目标设计平台为嵌入式、DSP和硬件设计人员提供了范围广泛的器件、通用设计流程、IP、开发工具和运行平台。

ISE11 设计套件拥有全新的工具许可管理方案。在本版产品发布之前,XILINX工具的许可管理主要采取基于用户的方式,即每名用户都需要一个许可证才能使用工具,任何工具都不提供流动许可证。从ISE11套件开始,XILINX将以两种配置方式提供工具:节点锁定式和流动式。节点锁定式即在单台计算机上锁定许可证,客户能够将任何XILINX工具的许可证下载到特定的工作站,多个用户能够共享使用运行在该工作站上的XILINX软件;流动式许可证可驻留于客户的网络服务器上,设计人员无论位于全球任何位置都能同时使用该许可证。

与以前的ISE版本相比,ISE11主要有以下特点。

(1)面向设计人员的改进。ISE11软件改进了布局和布线算法,运行速度平均提高2倍:支持多线程布局和布线工作方式,从而使用户进行大型设计时可同时进行多次的布局布线工作;XST工具的综合运行速度平均提高2倍;能更好地支持SecureIP,能更快地仿真PowerPC、MGT 和PCI硬IP模块,支持 Mentor、Cadence 和 Synopsys 仿真器。

(2)通过布局和布线优化降低动态功耗。ISE11通过对布局布线的优化,降低了10%的动态功耗。在软件方面,动态功耗是很重要的一环,怎样优化动态功耗分析,准确性很重要。如果准确性不高,那么再怎么进行优化都是在做无用功,因此ISE11在准确性方面也做了很大的提高。

(3)降低了对存储器的要求。多数设计采用32位工作站终端,32位工作站存在这样一个缺点:最多可以放4GB内存。对于Windows而言,只能识别其中的3GB,这样就浪费了很大一部分资源,而3GB内存想运行大点的程序是运行不起来的,只有用更大的64位工作站才可以,这样一来做设计的成本就增加了很多。因此产生了这样一个问题,是不是每个人都要有一台64位的工作站呢?新发布的ISE11版本中减缓了存储器方面的压力,使其对于存储器的要求方面平均降低了28%,从而解决了这一问题。

(4)大大缩短了主流FPGA器件的设计周期。ISE设计套件将基于 Virtex-5和 Spartan-3FPGA 的设计所需要的开发周期缩短了大约50%。ISE11.3版本支持 Virtex-6和 Spartan-6 器件的设计。

(5)加快了从设计的概念转化到生产的进程。不同的设计人员所关注的工具不同,例如,做软件开发的工程人员,他们一般没有FPGA架构方面的知识,而在这个环境中完全可以帮助他们做设计或者仿真,他们可以用C语言(或其他语言)把程序初步编好,然后下载到硬件上看结果,根据看到的结果再回到C语言编码进行修改。四种配置版本既能帮助经验丰富的客户优化工具选购,也能帮助FPGA设计新手轻松确定哪些工具是最适合他们设计需求的。每个配置版本都配套提供全面的设计创建、验证和实施工具,以及针对特定领域的IP。同时,四种新版本都可以定制,因此用户能根据设计流程的需要选择添加赛灵思或第三方合作伙伴提供的其他工具。赛灵思不会规定用户的设计流程,而是创建了可扩展、可定制的基础流程。此外,顶层设计人员还可根据设计团队的需求和每名设计团队成员的实际技能选择最适当的许可证数量和类型。举例来说,新推出的四种配置版本允许客户为设计团队添加诸如赛灵思软件开发套件(SDK)等额外的许可证选项,这样设计团队就能让数名软件开发人员为单个 FPGA 编写代码,而不必像过去那样购买整套嵌入式开发套件。

755

755

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?