前言

verilog实现任意位随机数产生

一、程序设计

module rondomeight(

input I_clk,

input I_rst_n,

input I_en,

output [2:0] eight

);

wire O_pn_lastmsb;

RANGING_sequence u1(

.I_rst_n(I_rst_n) , // Asynchronous reset

.I_clk (I_clk) , // the cycle clock for PN sequence generation, posedge valid

.I_en (I_en) ,

//.O_current_state =32'd0, // depends on the input value width

.O_pn_lastmsb (O_pn_lastmsb) // last msb means the msb of last state

);

reg [2:0] rondomega;

always@(posedge I_clk or negedge I_rst_n)begin

if(!I_rst_n)begin

rondomega <= 3'd0;

end

else if(I_en)begin

rondomega <= {rondomega[1:0],O_pn_lastmsb};

end

else begin

rondomega <= rondomega;

end

end

assign eight = rondomega;

endmodule

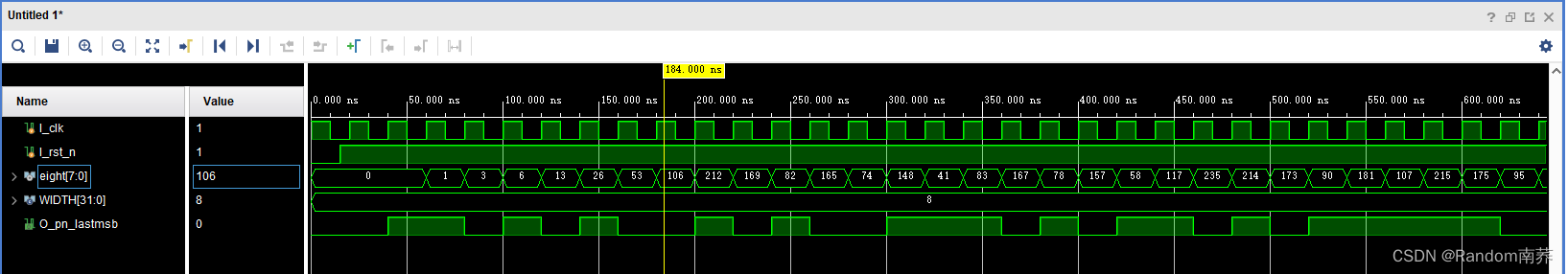

二、仿真图示

总结

可以生成任意位随机数,以上选择的是8位

3514

3514

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?