设计思路

根据功能表进行行为级建模,如下:

代码实现

设计模块

//filename:_74LVC161.v

module _74LVC161(

input CR,PE,CEP,CET,CP,

input [3:0] D,

output reg [3:0] Q,

output reg TC);

/*

参数说明:

输入:

CR位置零输入端,PE为预置,CEP,CET为控制信号,CP为时钟信号,D为预置信号

输出:

Q为输出端

TC进位信号

*/

always@(posedge CP,negedge CR)

begin

if(~CR) begin Q<=4'b0000;TC=0; end //异步清零信号的优先级最高

else if(~PE) Q<=D; //预置信号

else

casex({CEP,CET}) //使能信号

2'b0x: Q<=Q; //保持

2'bx0:begin Q<=Q; TC=0; end //保持

2'b11:begin Q=Q+1'b1; TC=(Q==4'b1111); end //计数

endcase

end

endmodule测试模块

filename:tb_74LVC161.v

`timescale 1ns/1ns

module tb_74LVC161();

reg CR,PE,CEP,CET,CP;

reg [3:0] D;

wire [3:0] Q;

wire TC;

/*

参数说明:

输入:

CR位置零输入端,PE为预置,CEP,CET为控制信号,CP为时钟信号,D为预置信号

输出:

Q为输出端

TC进位信号

*/

always

_74LVC161 U(CR,PE,CEP,CET,CP,D,Q,TC);

initial

$monitor($time,"\tCR=%b,PE=%b,CEP=%b,CET=%b,CP=%b,D=%b,Q=%b,TC=%b",CR,PE,CEP,CET,CP,D,Q,TC);

//时钟信号

initial

CP=1;

always

#5 CP=~CP;

//元件例化

initial

begin

//清零

CR=0;PE=1;D=4'b1100;CET=0;CEP=0;

#5;

//置数

CR=1;PE=0;D=4'b1100;CET=0;CEP=0;

#10;

//计数

CR=1;PE=1;D=4'b0000;CET=1;CEP=1;

#60;

//禁止计数

CR=1;PE=1;D=4'b0000;CET=1;CEP=0;

#20;

$stop;

end

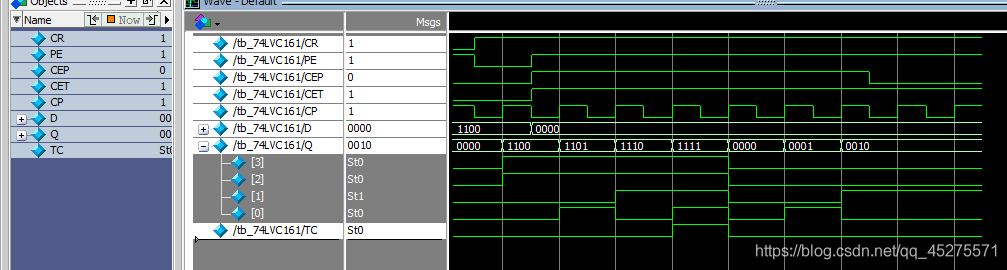

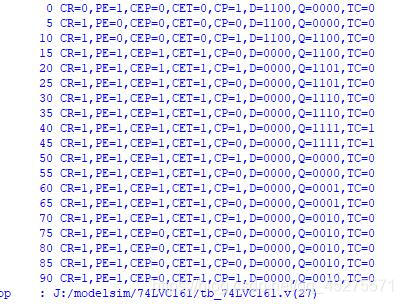

endmodule仿真结果

1302

1302

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?