PL 的"Hello World"LED 实验

参考文档《course_s1_ZYNQ那些事儿-FPGA实验篇V1.06》

Vivado版本 2018.3

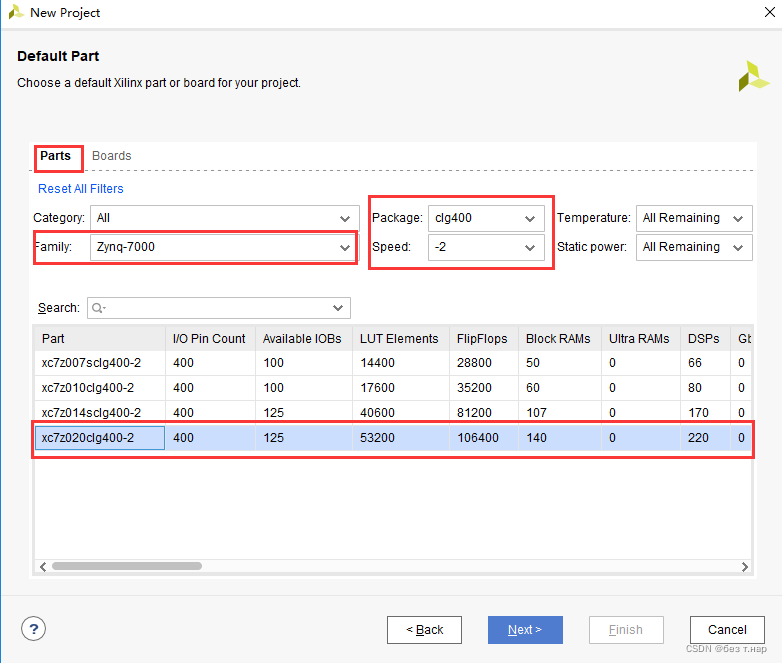

一、创建工程

创建RTL工程,Target language选择“Verilog”,虽然选择 Verilog,但 VHDL 也可以使用,支持多语言

混合编程;设计时根据自己的板子选择器件型号。

二、编写代码

工程界面(项目设计流程也基本按照软件的流程进行);添加源代码创建Verilog文件后即可开始设计。

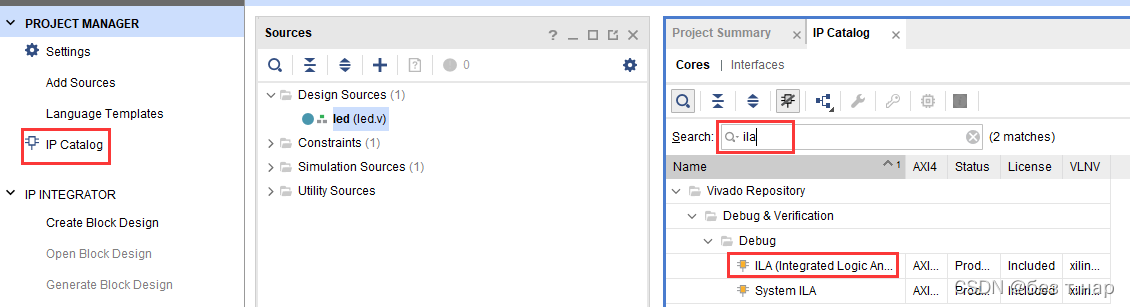

这里的IP catalog是Vivado提供的IP核,可以直接使用也可在BD中添加使用。

下面还有program and debug 用于生成bit文件下载程序调试等等

三、添加约束

3.1管脚约束(管脚位置和 I/O电平)

Vivado 使用的约束文件格式为 xdc 文件。xdc 文件里主要是完成管脚的约束,时钟的约束;可以通过

Window -> I/O Ports进行设置,也可以通过编写lxdc文件进行设置。这里我们需要对 led.v 程序中的

输入输出端口分配到 FPGA 的真实管脚上。

XDC 编写的语法,普通 IO 口只需约束引脚号和电压

管脚约束如下:

set_property PACKAGE_PIN "引脚编号" [get_ports “端口名称”]

电平信号的约束如下:

set_property IOSTANDARD "电平标准" [get_ports “端口名称”]

3.2时钟约束

一个 FPGA 设计除了管脚分配以外,还有一个重要的约束,那就是时序约束,这里通过向导方式演示

如合进行一个时序约束。 综合"Run Sythesis"点击“Constraints Wizard”按照指引修改时钟频率。成功

添加后 xdc 文件中时钟约束将会加入文件中。

create_clock -period 20.000 -name sys_clk -waveform {0.000 10.000} [get_ports sys_clk]

四、代码仿真

使用Vivado自带的软件进行仿真,编写好testbeach文件后,点击 Run Simulation 按钮,再选择

Run Behavioral Simulation。(在接下来的IP核学习中做进一步的展开说明)

五、下载验证

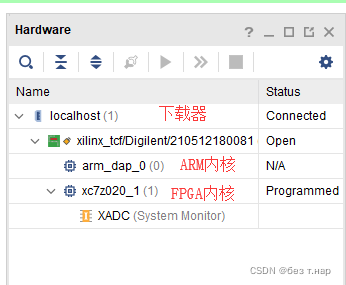

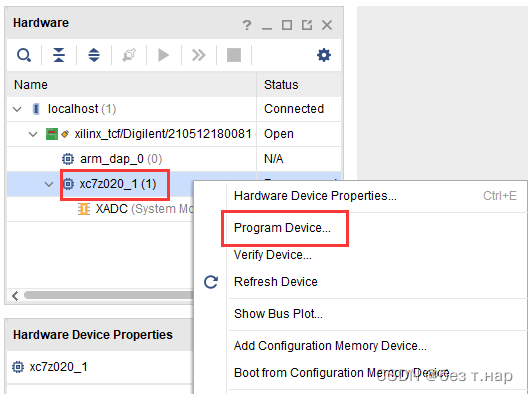

连接好开发板的 JTAG 接口,给开发板上电在“HARDWARE MANAGER”界面点击“Auto Connect”,自动连接设备可以看到 JTAG 扫描到 arm 和 FPGA 内核。

六、信号抓取ILA

Vivado 有内嵌的逻辑分析仪,叫做 ILA,可以用于在线观察内部信号的变化,对于调试有很大帮助。

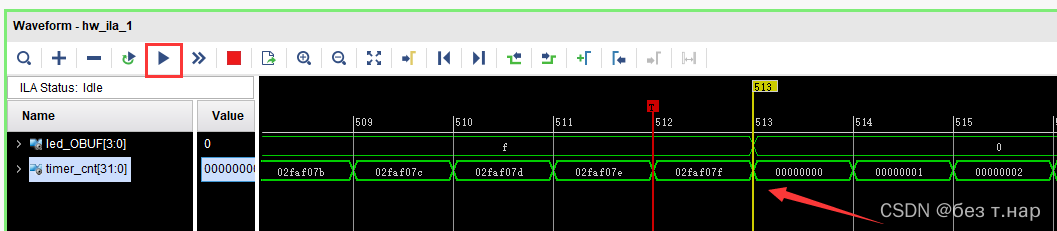

点击 IP Catalog,在搜索框中搜索 ila,双击 ILA 的 IP。在要观测的文件中实例化ila。下载时添加bit和ltx文件。弹出的在线调试窗口出现添加的信号,点击运行便可以看到信号的数据

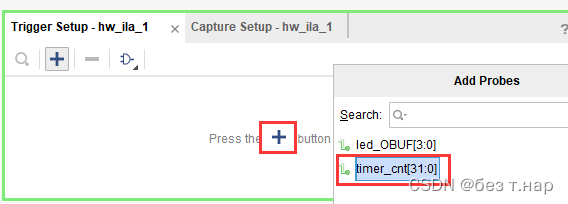

可以触发采集,在 Trigger Setup 窗口点击“+”,深度选择 timer_cnt 信号

可以触发采集,在 Trigger Setup 窗口点击“+”,深度选择 timer_cnt 信号

本实验中设置好触发后再次点击运行,即可以看到触发成功(红标T),此时 timer_cnt 显示为十六进制,而 led 也在此时翻转。

462

462

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?