功能:

实现3-8译码

Verilog代码:

//行为级设计

`timescale 1ns / 1ps

module decoder3_8_01(en, addr, y);

input [2:0] en, addr;

output [7:0] y;

reg [7:0] y;

always@(addr or en)

begin

if(!en[2]) y<=8'b0000_0000;

else if(en[1]) y<=8'b0000_0000;

else if(en[0]) y<=8'b0000_0000;

else

begin

case(addr)

3'b000: y <= 8'b00000001;

3'b001: y <= 8'b00000010;

3'b010: y <= 8'b00000100;

3'b011: y <= 8'b00001000;

3'b100: y <= 8'b00010000;

3'b101: y <= 8'b00100000;

3'b110: y <= 8'b01000000;

3'b111: y <= 8'b10000000;

endcase

end

end

endmodule

//数据流级设计

`timescale 1ns / 1ps

module decoder3_8_02(en, addr, y);

input[2:0] en, addr;

output[7:0] y;

wire[7:0] y;

wire w;

assign w = ~en[0] & ~en[1] & en[2];

assign y[0] = w & ~addr[0] & ~addr[1] & ~addr[2];

assign y[1] = w & addr[0] & ~addr[1] & ~addr[2];

assign y[2] = w & ~addr[0] & addr[1] & ~addr[2];

assign y[3] = w & addr[0] & addr[1] & ~addr[2];

assign y[4] = w & ~addr[0] & ~addr[1] & addr[2];

assign y[5] = w & addr[0] & ~addr[1] & addr[2];

assign y[6] = w & ~addr[0] & addr[1] & addr[2];

assign y[7] = w & addr[0] & addr[1] & addr[2];

endmodule

//门级设计

`timescale 1ns / 1ps

module decoder3_8_03(en, addr, y);

input[2:0] en, addr;

output[7:0] y;

wire[7:0] y;

wire n0, n1, n;

wire[2:0] abar;

not (n0, en[0]);

not (n1, en[1]);

and (n, n0, n1, en[2]);

not (abar[0], addr[0]);

not (abar[1], addr[1]);

not (abar[2], addr[2]);

and (y[0], n, abar[0], abar[1], abar[2]);

and (y[1], n, addr[0], abar[1], abar[2]);

and (y[2], n, abar[0], addr[1], abar[2]);

and (y[3], n, addr[0], addr[1], abar[2]);

and (y[4], n, abar[0], abar[1], addr[2]);

and (y[5], n, addr[0], abar[1], addr[2]);

and (y[6], n, abar[0], addr[1], addr[2]);

and (y[7], n, addr[0], addr[1], addr[2]);

endmodule

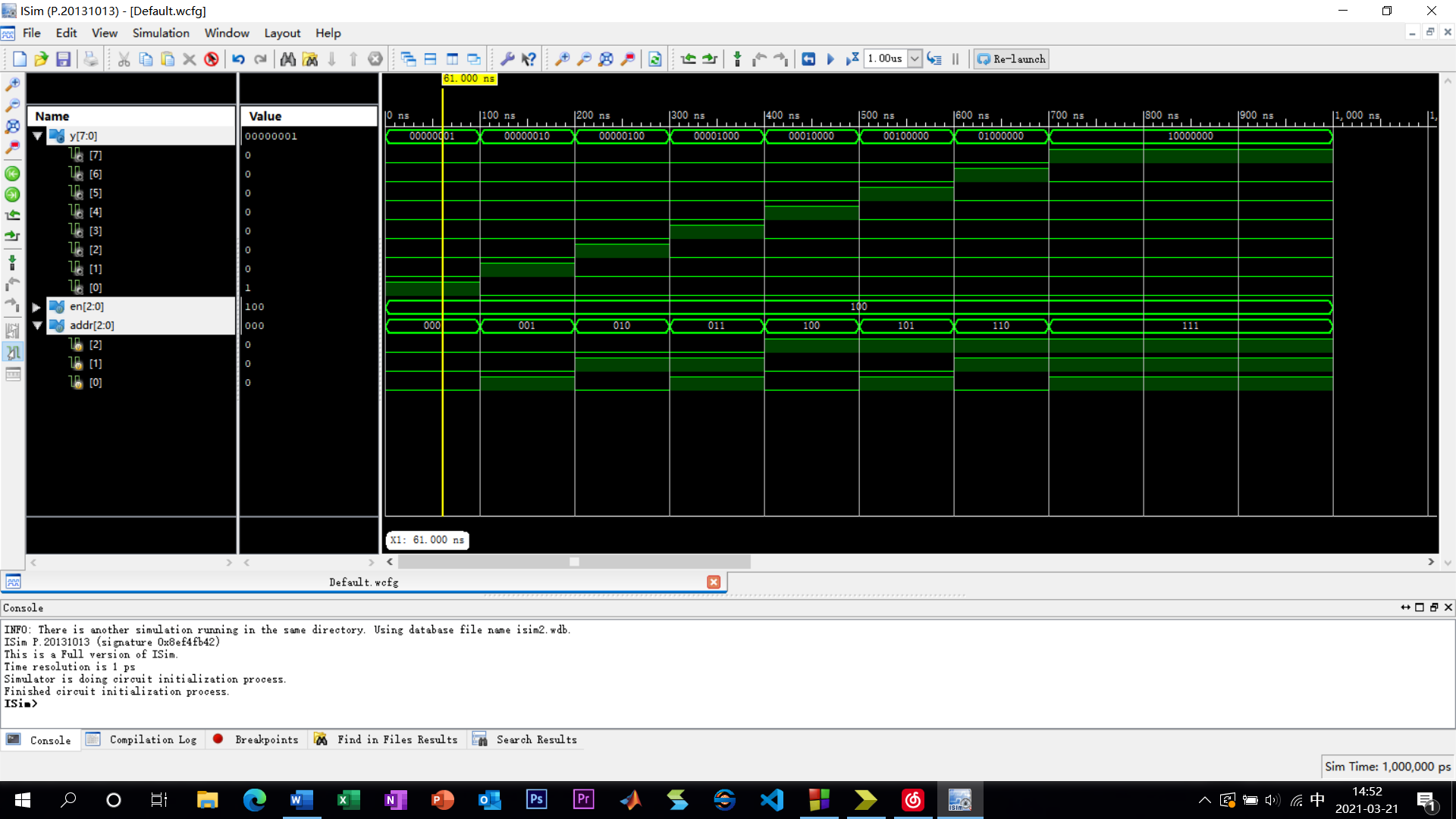

测试代码:

initial begin

en[0]=0; en[1]=0; en[2]=1;

addr = 3'b000;

// Wait 100 ns for global reset to finish

#100;

addr = 3'b001;

#100;

addr = 3'b010;

#100;

addr = 3'b011;

#100;

addr = 3'b100;

#100;

addr = 3'b101;

#100;

addr = 3'b110;

#100;

addr = 3'b111;

end

效果演示:

3532

3532

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?