前言:

本专栏旨在记录高频笔面试手撕代码题,以备数字前端秋招,本专栏所有文章提供原理分析、代码及波形,所有代码均经过本人验证。

目录如下:

10.数字IC手撕代码-数据位宽转换器(宽-窄,窄-宽转换)

13.数字IC手撕代码-流水握手(利用握手解决流水线断流、反压问题)

18.数字IC手撕代码-双端口RAM(dual-port-RAM)

...持续更新

为了方便可以收藏导览博客: 数字IC手撕代码-导览目录

目录

什么是分频

分频就是生成一个新时钟,该新时钟的频率是原有时钟频率的整数分之一倍,新周期是原有周期的整数倍。

再简单来说,让你手撕一个四分频电路,就是写代码生成一个周期是原来四倍的时钟,如果手撕一个三分频电路,就是写代码生成一个周期是原来三倍的时钟。

如上图所示,就是一个四分频电路的波形,四分频后,新的clk_out的频率是原来的1/4,也即周期是原来的4倍,从图中可以看到,clk每过4个周期,clk_out过1个周期。

小数分频

在之前的专栏中,讲完了任意占空比任意偶数分频器,以及任意占空比任意奇数分频器后,下面讨论更加夸张的小数分频。什么是小数分频?以及怎么实现 9/4,17/3 ,6.3 等任意小数分频??

编码小数分频,就不能看微观了,要用宏观的眼界去看,比如实现一个 17/3 分频,表达成:17 除以 3 得商为 5 余2。

那么我们就可以通过5(商)分频和7(商+余数)来实现 17/3 分频。

现在我们来确定5分频和7分频的次数,设:

5分频的次数为a , 7分频的次数为b;

那么应该有:

a+b=3(除数)

5a+7b = 17(被除数)

解得a=2,b=1,也就是说通过2次5分频和1次7分频可得到 17/3 分频。

这样编程完之后就实现了17/3分频,那么自然会有个疑问,为什么这样就实现了?详细看,仍然是五分频管五分频的,七分频管七分频的,大家各管各的,这算哪门子的小数分频啊??

所以就要提到我们前面说的宏观来看。宏观来看,总共是17个时钟周期,由三个分频器均分,那么平均每个分频器就是分到17/3了,这就是小数分频,这是一个宏观的平均概念。解释完概念,我们下面开始手撕代码。

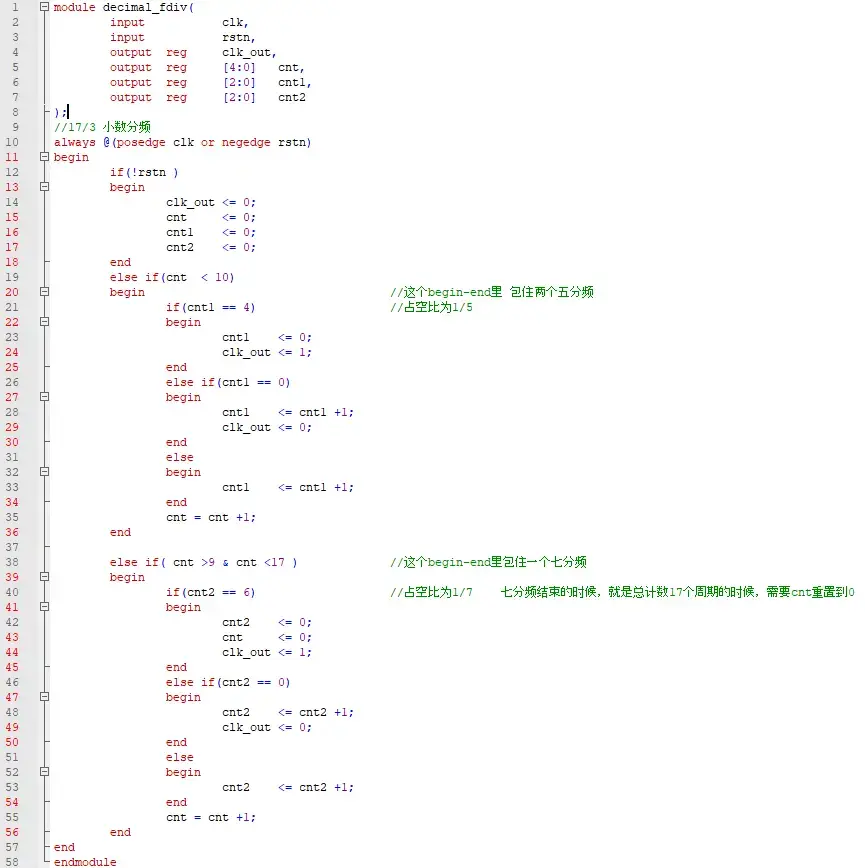

代码

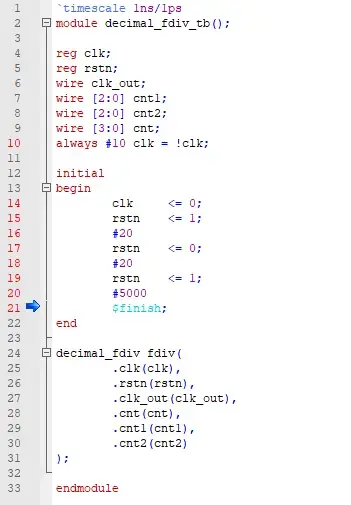

testbench

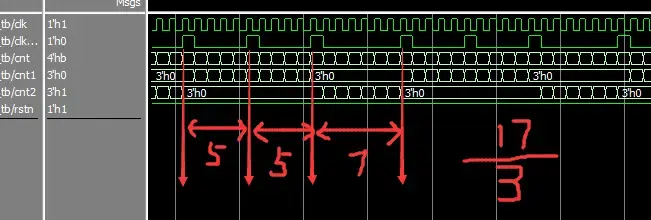

波形

如同我们分析的一样,两个五分频,一个七分频,每十七个周期循环一次。即每十七个周期有三个分频器,平摊下来就是 17/3 。

小数分频的缺点就是 占空比不为50%,要想实现50%占空比的小数分频,涉及很多算法,具体算法十分复杂,一般不会作为手撕代码题,本篇专栏到此结束。

1836

1836

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?