目前DDR3存储器仍旧广泛应用在各个领域,它是在DDR2基础上针对新型芯片而采用新型设计方法的新一代内存技术,其工作频率(即当存储器中正常运行中时钟信号的频率)达到800MHz以上。并且与第三个时期的DDR2相比具有长时间工作功耗更低、热量产生更小、工作频率进一步提高、显卡的整体经济成本得到明显降低、通用兼容性能好等优势。表面上DDR3与DDR2的基本结构相比并没有实质的不同,实际上DDR3的研发生产解决了DDR2所面临的各种技术问题包括:地址、命令与控制总线的拓扑结构更先进化;外部数据传输速率更高化;在功耗降低的同时仍具有良好的工作性能。

相比于DDR2存储芯片设计,DD3主要设计改进特点是:

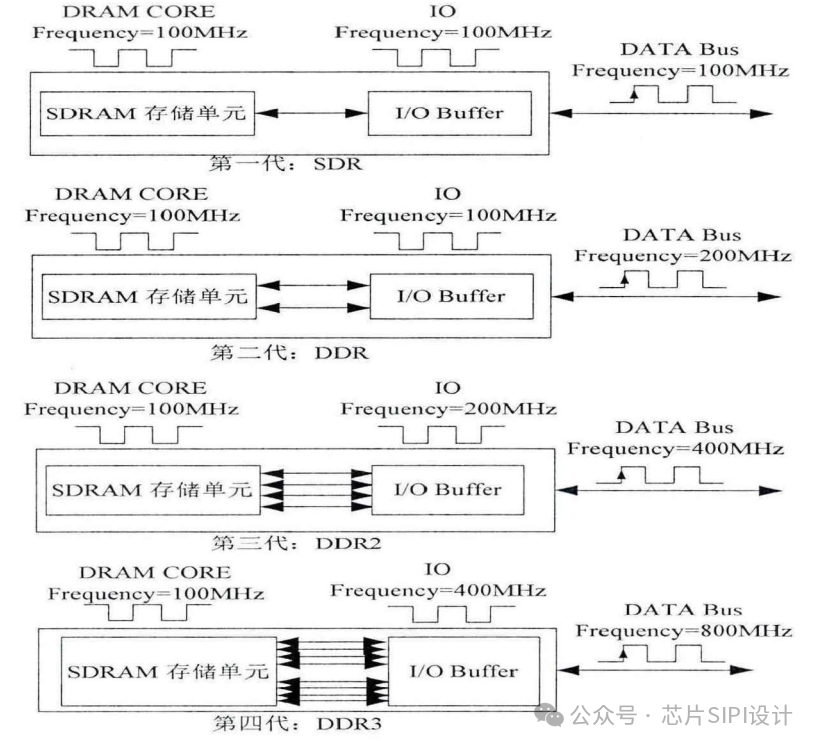

1)、采用8bit预取设计比DDR2的4bit预取设计位数提高了2倍。

2)、为了减小命令、地址和控制总线的工作负担,采用了点对点的拓扑结构。

3)、为了减小芯片的体积提高集成度,采用100nm以下的最新生产制造工艺标准。

4)、为了保证数据的读取准确率,还增加异步重置与ZQ校准的功能。

5)、为了减小芯片正常工作时功耗值,将DDR3的工作电压从1.8V降低到1.5V。

6)、因为运行功耗的进一步降低,DDR3的工作频率进一步提高,在一定的程度上弥补了延迟周期长的缺陷,从而提高数据的传输率。DDR3最高数据传输速度理论上可达到1866Mbps以上,大大提高了传输带宽和传输效率,但实际使用中很难的达到1866Mbps以上。这是因为DDR3在高速运行的条件下会出现很多信号完整性的问题如反射、串扰、轨道塌陷、辐射过大等问题。这些信号完整性问题会相互影响从而影响DDR3的正常运行功能,故不能达到理论上的运行速度。因此,解决DDR3信号完整性问题是高速电路系统中要解决的技术难题。

DDR常用模组介绍

DDR存储模组目前仍在广泛的使用在很多场景,DD3存储器模组是根据JEDEC的相关存储模组设计标准而采用多颗DDR3SDRAM组合进行制作而成。JEDEC标准根据存储模组上的SDRAM信号线与内存控制器的连接方式的差别进行分类如下:

(1)没有缓冲的存储模组

简称UDIMM(UnbufferDualInlineMemoryModule),特点是传输过程中没有缓冲器的连接,存储模组上的全部信号线路可以和内存控制器的封装引脚直接进行连接。

(2)带寄存器的存储模组

简称RDIMM(RegisterDualInlineMemoryModule),特点是因为存储模组带有寄存器使其控制线路和地址线路先连接寄存器后再接入到控制器的封装引脚,而数据信号线路与控制器的封装引脚采用直接连接的方式。这样的设计不仅可以保证接入到内存控制器的信号受到很小的外界干扰是比较完整的信号,而且控制器能够兼容高达4个内存区块的存储模组。

(3)负载较低型存储模组

简称LRDIMM(LoadReducedDualInlineMemoryModule),存储模组的设计特点和DDR2的FBDIMM差不多相接近,也是模组上的全部信号总线先连接内存缓存器再连接控制器的封装引脚。这种连接方式将控制器兼容存储模组的内存区块数量扩大到8个,使存储容量进一步扩大。

上述存储模组根据能否具有错误检查和自动更正功能又被分类为ECC(ErrorCheckingandCorrecting)内存和No-ECC内存两大类。对于带有寄存器的存储模组和负载较低型存储模组来说因为设计的内存容量值比较大,故具有自动更正和错误检查的内存比较多。例如,我们通常所见到PC机内的DDR3内存一般具有ECC功能的存储模组。

DDR3存储特点

2010年7月颁发的DDR3SDRAMJEDEC标准中明确规定了DDR3SDRAM内置能够包括若干个行、列的8个Bank,和内置4个Bank的DDR2相比其能够制作内存更大容量的SDRAM。另外,DDR3还具备更多特点:

(1)异步复位特点

为了让DDR3的初始化操作更简单、高效化,在DDR3的封装上新增Reset复位引脚。当DDR3接收到复位命令时,中止正在运行的所有功能并切换至待机状态达到减小功耗的目的。

(2)ZQ校准功能

为了达到自动调节驱动能力,采取在ZQ引脚上端接阻值为240的公差电阻完成ZQ校准功能。当系统发送出ZQ校准指令集时,在设计的时钟周期内通过片上校准机制对ODT终端的电阻值和导通的电阻值进行更新自动校准。

(3)突发长度不同

为了实现更高的读写速度,储存器的数据读和写都使用突发读写的模式来实现的。DDR3的突发模式不仅可以兼容先前的DDR和DDR2的架构设计系统,而且还可以通过FLYBY模式来自动调节突发长度的数值。

(4)自刷新功能

为了解决断电时存储数据易失,维持数据稳定和达到减小电能消耗的设计目标。DDR3通过灵敏度高的温度检测器根据实际运行温度进行自动刷新技术,同时为了提高自动刷新效率,还能够通过刷新指定内存区域组进行部分区域自动刷新功能。

(5)点对点连接

为了一方面减少数据、地址和控制信号的总线压力,另一方面改善信号完整性提高系统的运行性能。根据Rank的模组是单个还是双个,使存储器的控制器分别采用点对点和点对双点的方式与储存模组进行连接。

(6)两个参考电压

为了储存器能够稳定工作在所设计的参考电压范围内,减少因为电压的波动致使存储器进入自动重启或自动待机状态的次数。给DDR3的SDRAM作电压设计成两个参考电压,一个为地址总线和控制总线提供电能供给,另一个为数据总线提供电能供给。两个参考电压使DDR3在工作时对电压抗噪干扰能力增强,保证DDR3正常工作时的可靠性和稳定性。

(7)8bit预取架构

通常通过增加SDRAM的I/O时钟频率来达到提高DDR3的数据传输速度设计目的。但因受到工艺加工制造技术和高频率环境下衍生的信号完整性等问题的限制,采用增加内核工作频率的技术方案发展缓慢。故常采用拓宽数据预取位数的技术来实现,其预取架构位数的发展过程如下图,到目前的DDR3己扩大到8bit的预取架构。

从图中,我们很清楚的发现,当对应的SDRAM内核工作频率同是100MHz时,DDR3 SDRAM采用8位预取架构时可获得800MHz的总线传输频率。对比DDR2的4位预取架构,可以获得是其两倍的工作频率,从而大大提高了数据总线的传输带宽。

1865

1865

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?