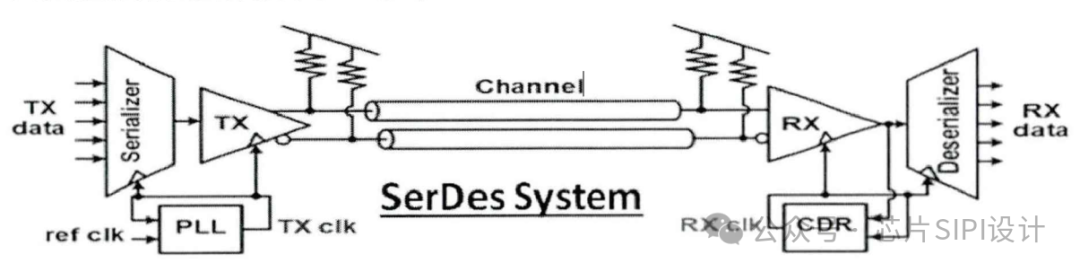

链路系统设计是个复杂的系统性工程,整条链路由发射器Tx、信道和接收器Rx三部分组成。在工作范围在10米内距离的Gbps级链路系统中,如电脑主板采用PCIE接口总线链路及能进行全反冲的双列内存都使用了公共时钟体系。发射器处通过PLL倍频将参考时钟转换到所需的时钟频率商,提供发射器的驱动数据的位定时,接收器处参考时钟先被发送到发送端的锁相环,由pll倍频转换成时钟频率,再通过数字时钟恢复单元来产生比特位时钟,然后将接收到的数据和转换后一定频率的时钟做输入,得到于输入数据相位对齐的位时钟,就能用恢复出来的位时钟对数据重定时或重采样,为了将这个设计工程化,需要利用信号完整性分析来将整个链路分解开来,对于每部分单独分析其电气要求以及可能存在的信号完整性问题。下面以PCIEGEN4规范为例来具体分析发送端、接受端和信道的设计要求。

PCIEGEN4信号为16Gbps或16GT/s,按信号的频域分析定义,该信号的基础频率为8GHz,因此在进行过孔和链路的频域分析时,主要关注点在8GHz及其附近的频点。

发送端

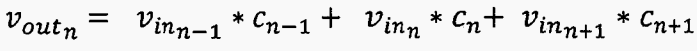

高速串行链路发送端一般采用预加重来提高信号质量。以PCIEGEN4议规范为例制定了PCIE接口发送端的输出规格,包括输出信号的电幅度,抖动,输出电阻,上升沿/下降沿等信息,以及用于调整输出信号的均衡参数。为了弥补链路衰减对PCIE信号的影响,PCIE协议在发送端定义了一个3阶的有限冲击响应滤波器,称为发送端前馈均衡器,用于调整发送端的波形。3阶有限冲击响应滤波器的定义如下所:

示:

根据上式,该3阶滤波器如下图所示:

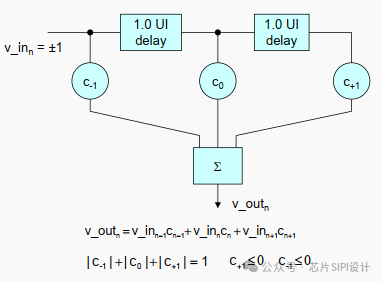

经过该滤波器的处理后,PCIE的输出信号会发生改变,如下图示为均衡对PCIE输出信号的改善。从图中可以看到,Va信号和Vd信号的幅度明显比较大,这是因为Va和Vd信号都和前一个UI的状态不同,属于信号变化的过程。从频域来看,变化的信号高频成分较高,而高频成分由于信道的衰减会损失一部分,所以提高信号的信号的幅度会有利于接收端正确识别到该信号。Vb信号的幅度明显比Va信号的幅度低,这是因为Vb信号和前一个UI的状态相同,属于信号不变的过程。从频域来看,状态不变的信号高频成分很少,信号的衰减对该信号的影响较低,因此使用较低的幅度会有利于接收端同时识别到高频信号和非高频信号。Vc信号的幅度比Vb信号幅度略大一点,是因为Vc信号后面的Vd信号状态会发生变化,此时增大Vc信号幅度,有利于增加Vd信号在接收端的辨识度。

接收端

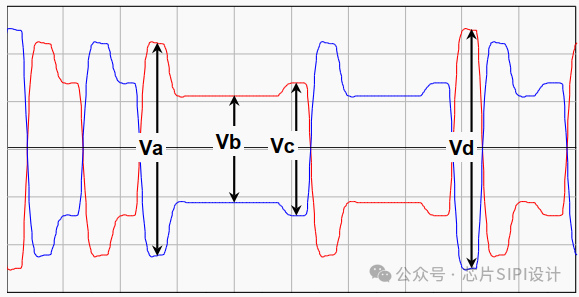

高速串行信号通过PCIEGEN4接口输出的信号要经过一段链路才能到达接收端,由于信号在链路中衰减接收端的信号相比发送端会有很大的失真。PCIEGEN4协议规范里也定义了在接收端的电气规格,包括到达接收端时的信号幅度,抖动,输入电阻等信息,以及用于调整接收端输入信号的均衡功能。接收端的均衡功能,称为连续时间线性均衡器,其传递函数如下式:

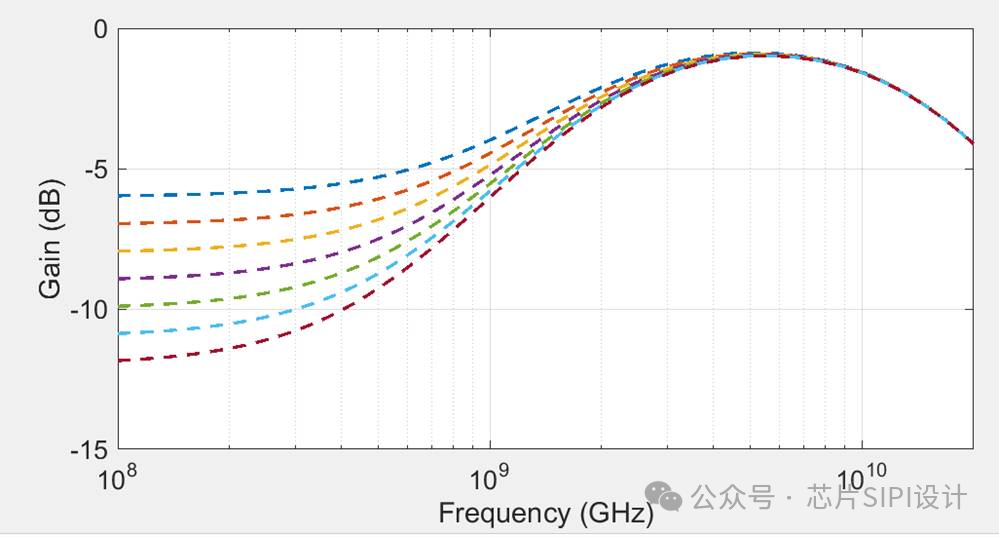

下图所示为接收端均衡器的频域响应曲线,可以看出该曲线高频部分的放大幅度明显大于低频部分的放大幅度,以用于补偿链路上对高频成分的衰减,使得真个频率范围内的频率响应更加趋于平坦。

信道

在高速串行链路里,信道对高速信号的影响至关重要。信道会对高速信号产生两种损耗,分别是由反射引起的回波损耗,以及由衰减引起的插入损耗。发射端和接收端的回波损耗和插入损耗测量基本相同,因此二者都包含在发射端部分。对信道的测试方法是利用网络分析仪,使用精密探针点测到信道的两端。高速串行链路的信道结构如下图所示。

常见的高速串行链路,信号传输的导体介质为铜,铜周边用树脂作为不同信号的绝缘材质。由于实际导体的导通率不可能无限大,绝缘介质的绝缘性也无法做到真空,因此实际的高速串行链路会对信号产生衰减,且信号频率越高时,衰减幅度越大。因此,前面两节在发送端和接收端都需要采用特殊的均衡电路来补偿这种高频衰减。

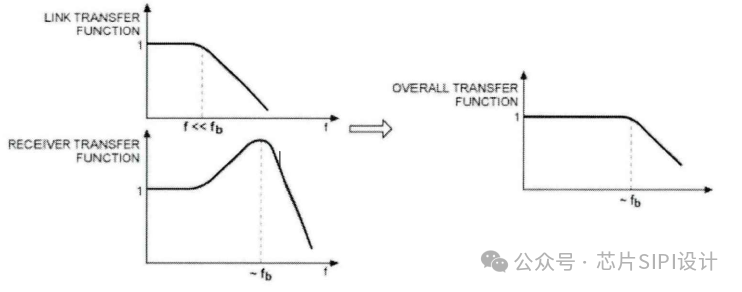

常见的尚速串行链路信道的频域响应如下图中的Link Transfer Function所示,发送端或接收端的均衡电路的频域响应如图中的Receiver Transfer function所示,均衡电路对信道的补偿后的总体特性如图中的Overall Transfer function所示。

998

998

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?