数字后端——物理单元介绍

物理单元(physical cell)指没有逻辑单元但具有物理实现功能的标准单元。

Tap cell

tap cell用于防止latch up。

早期的标准单元自带tap,这样会导致芯片面积比较大,后面标准单元就不带tap,需要我们添加tap cell。

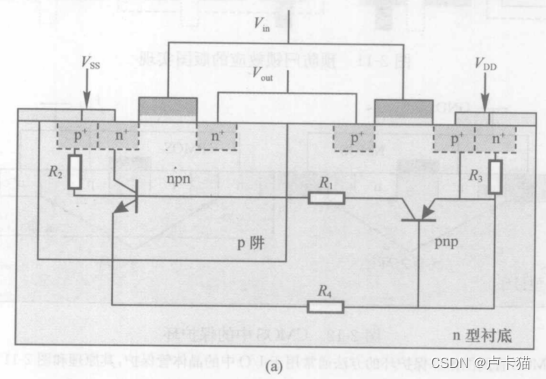

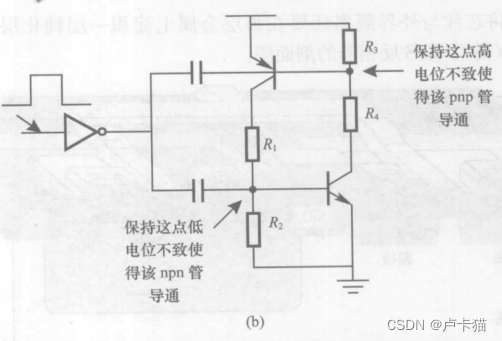

latch up(闩锁效应),在CMOS工艺中,由于npn和pnp型晶体管的存在,以及寄生电阻R2和R3的存在使两个晶体管相互耦合组成一个正反馈放大电路。一旦某个晶体管具有足够的基极偏置电压,使正反馈电路进入工作状态,将电流不断放大,将导致电源和地之间形成极大的导通电流,烧坏芯片。

Tap cell的作用就是通过固定间距对衬底施加偏置电压减小衬底的寄生电阻,使三极管无法达到导通要求从而切断闩锁效应的正反馈环路,消除闩锁效应。

Boundary cell

Boundary cell 也称 Endcap cell,在28nm以及更小的工艺中,为了保证栅以及氧化层的一致,需要在标准单元Row两端放置 Endcap cell。避免在光刻时,由于最两端标准单元左右环境不一致导致其性能有所差异。

Filler cell

为什么要加filler cell?

- 为确保所有VDD和VSS rail连接正常,我们需要使用fill cell填充标准单元row中的空白区域

- 在芯片刻蚀过程中,对周围std cell 起保护作用

Tie cell

Tie cell (电压钳位单元):某些信号端口或闲置信号端口需要钳位在固定的逻辑电平,tie high/low cell完成这样的功能。还起到隔离普通信号和VDD、VSS的作用,在做LVS或形式验证的时候不至于引起混乱。

8407

8407

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?