AXI 1G/2.5G Ethernet Subsystem 是一个为FPGA设计的以太网子系统,它支持1Gbps和2.5Gbps的数据传输速率,使得FPGA能够直接进行高速以太网通信。这个子系统通常包含以太网MAC控制器、GMII(千兆媒体独立接口)或RGMII(简化GMII)接口、以及可选的PHY(物理层)接口支持。

要自定义AXI 1G/2.5G Ethernet Subsystem IP核,可以按照以下步骤为与该IP核相关的各种参数指定值:

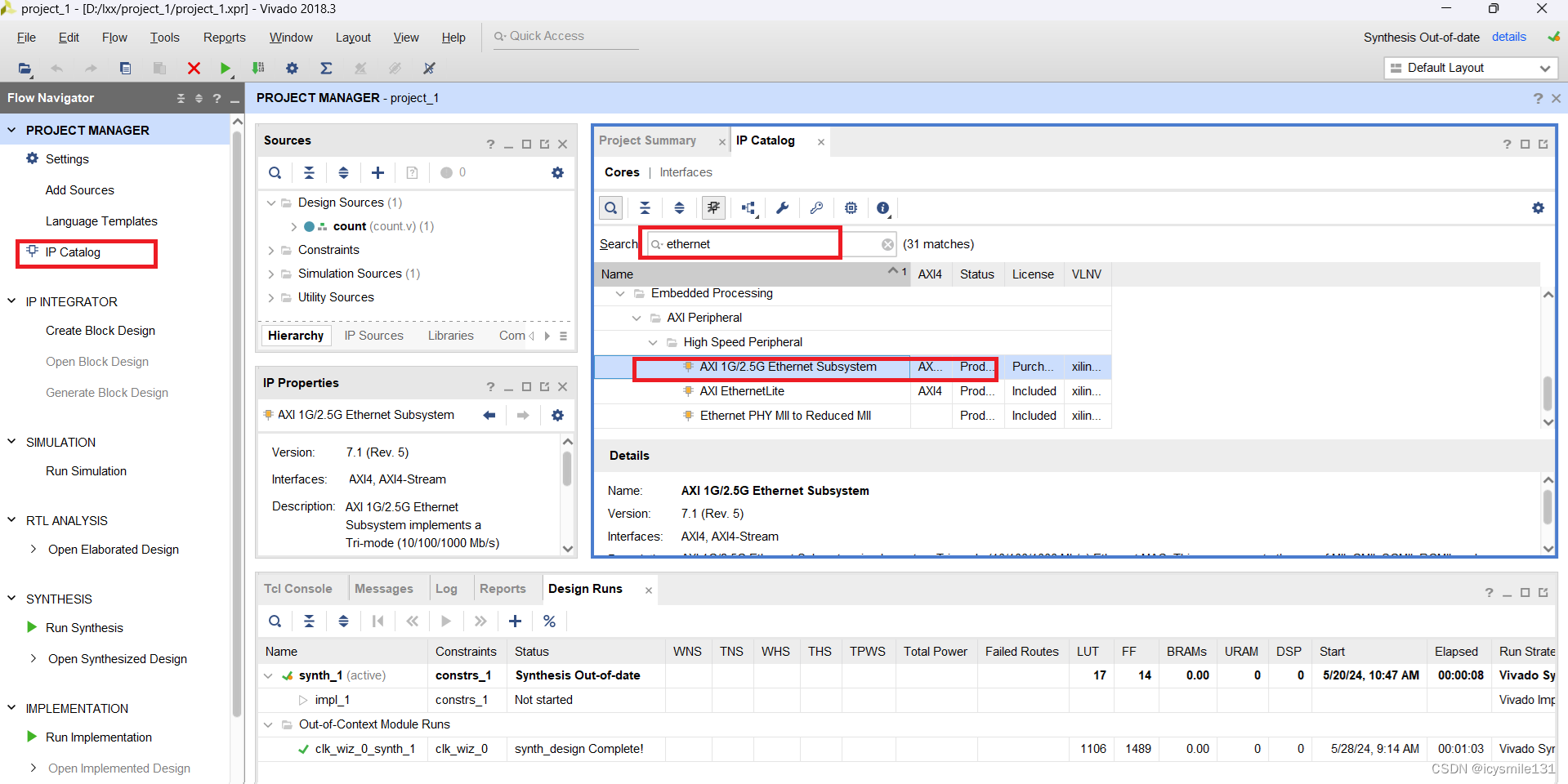

1 从Vivado IP目录中选择IP

打开Vivado软件,并加载项目。在左侧的IP浏览器中,找到并定位到AXI 1G/2.5G Ethernet Subsystem IP核。从IP目录中选择AXI 1G/2.5G Ethernet Subsystem IP核。

2 自定义IP

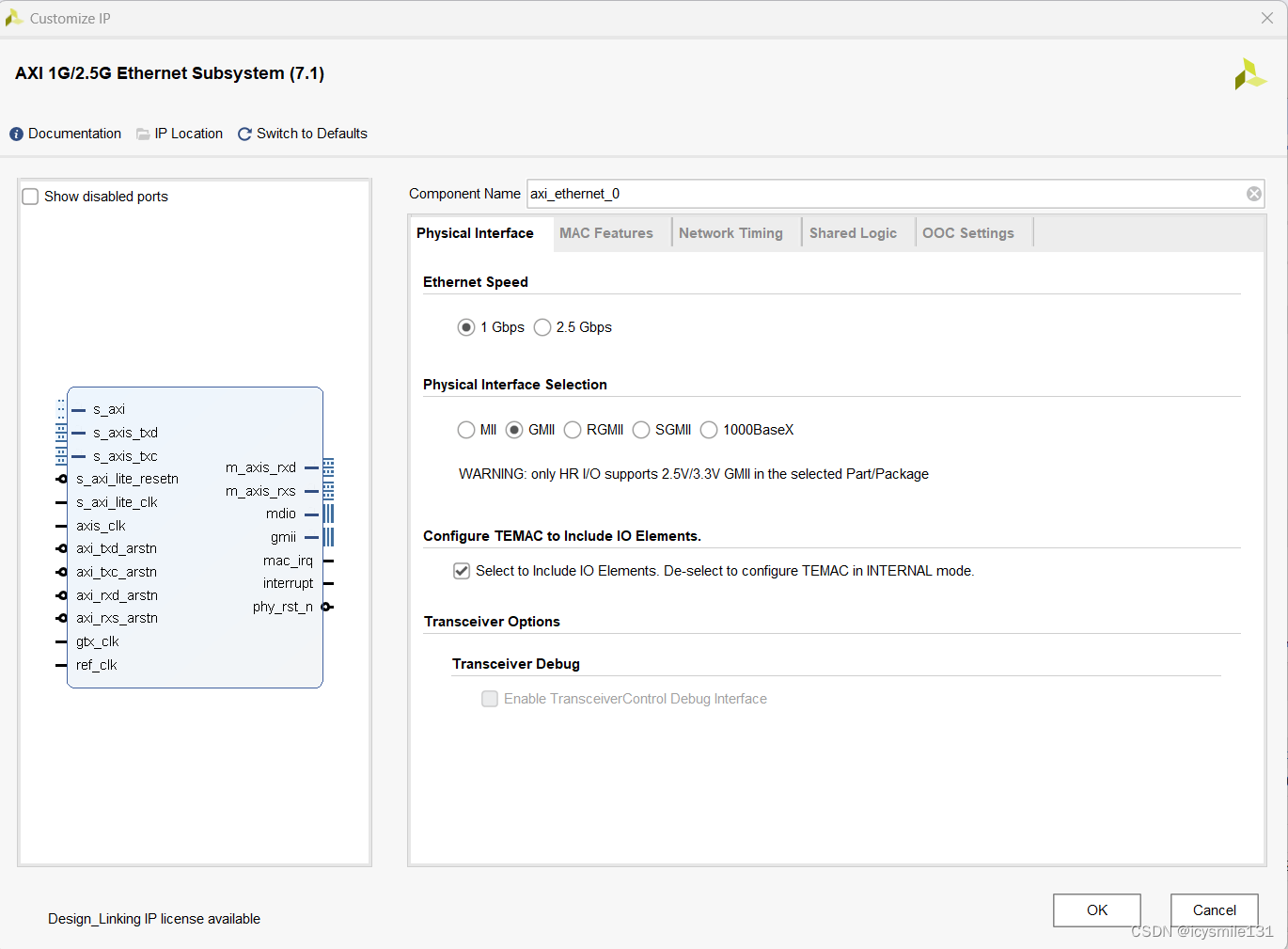

选中AXI 1G/2.5G Ethernet Subsystem IP核后,可以通过以下方式之一来打开其自定义界面:

- 直接双击选中的IP核。

- 在工具栏中找到并点击“Customize IP”命令。

- 右键点击选中的IP核,从弹出的菜单中选择“Customize IP”命令。

3 配置参数

在打开的自定义界面中,将看到与AXI 1G/2.5G Ethernet Subsystem IP核相关的多个参数和选项。

(1)Physical Interface

此选项页提供与物理层相关的选项。

- Ethernet Speed: 以太网支持的速度类型有1 Gb/s(千兆位每秒)和2.5 Gb/s(2.5千兆位每秒)。这

- Physical Interface Selection(物理接口选择): :这个选项用于选择物理接口类型。支持的PHY类型包括MII(媒体独立接口)、GMII(千兆媒体独立接口)、RGMII(简化GMII)、SGMII(串行GMII)和1000BASE-X。每种类型都有其特定的电气特性和用途,选择哪种类型取决于您的具体需求和连接的PHY设备。

- Configure TEMAC to include IO Elements :

Select to Include IO Elements. De-select to configure TEMAC in INTERNAL mode

该选项是用来选择是否包含I/O元素。这个选择决定了TEMAC如何与外部物理层(PHY)接 口。当选择了该选项,即选择了包含I/O元素,这通常意味着您希望TEMAC使用外部PHY,并 且您正在为连接外部PHY所需的信号(如MDIO、MDC、TX/RX数据对等)创建硬件接口。在 这种情况下,您可能需要在FPGA设计中添加适当的I/O块,并将它们连接到TEMAC的相应端 口。

当不选择该选项时,即选择不包含I/O元素(即配置为内部模式),则TEMAC可能使用FPGA 内部集成的PHY(如果可用),或者它可能预期与外部PHY通过某种内部总线(如AXI Stream)进行通信,而不是直接通过I/O引脚。在这种模式下,您可能不需要为PHY信号添加 额外的I/O块,但您可能需要配置其他与内部PHY或内部总线通信相关的参数。

- Enable Transceiver Control Debug Interface: 如果选择此选项,将启用额外的收发器控制端口,用于TX驱动器、RX均衡和其他功能(如PRBS,伪随机二进制序列)。这个选项仅在SGMII或1000BASE-X模式的非LVDS模式下可用。这些额外的控制端口允许更细粒度的调试和控制,以帮助优化系统性能或进行故障排查。

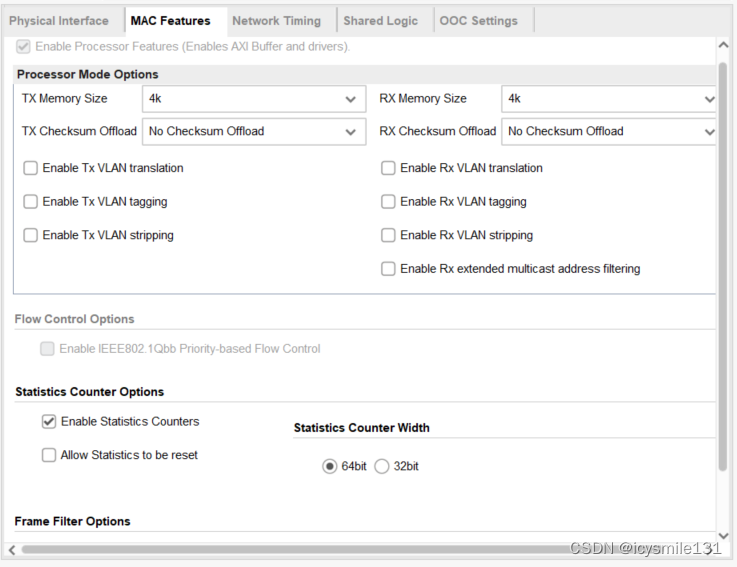

(2)MAC Features

在该选项页中将找到与以太网MAC功能相关的各种选项。

-

Enable Processor Features

当启用处理器模式时,axi_ethernet_buffer可用,并且提供驱动程序支持。这意味着处理器可以直接与硬件缓冲区交互,以加速网络数据处理。只有在PHY(物理层接口)类型为1000BASE-X或SGMII时,才可以禁用处理器模式。此外,在2.5G的数据速率下不支持处理器模式。

-

Processor Mode Options

①TX和RX 内存大小通过TX Memory Size和RX Memory Size选项来设置:可以选择发送 (TX)和接收(RX)内存的大小,以优化性能和内存使用。

②TX和RX校验和卸载通过RX Checksum Offload 和TX Checksum Offload选项来设置: 通过选择这些选项,处理器可以将校验和计算的任务卸载给硬件,从而减轻处理器的负担。

③ VLAN选项详解

对于TX和RX数据流,VLAN选项提供了VLAN标签(VLAN tagging)、VLAN剥离(VLAN stripping)和VLAN转换(VLAN translation)的功能。

VLAN标签(VLAN Tagging):在网络帧上添加VLAN标签,以标识该帧属于哪个VLAN。 当需要将数据发送到特定的VLAN时,可以在发送前为其添加VLAN标签。通过相应的选项选 择是否启用VLAN标签功能,并配置相关的VLAN ID。

VLAN剥离(VLAN Stripping):在接收网络帧时,移除其上的VLAN标签。当接收到带有 VLAN标签的帧,但需要在不带有标签的环境中处理该帧时,可以使用VLAN剥离功能。通过相应的选项选择是否启用VLAN剥离功能。

VLAN转换(VLAN Translation):在接收网络帧时,将其从一个VLAN的标签转换为另一个 VLAN的标签。当需要跨VLAN路由数据时,可以将一个VLAN的数据帧的标签转换为另一个VLAN的标签,以便在目标VLAN中处理。通过相应的选项选择是否启用VLAN转换功能,并配置源VLAN ID和目标VLAN ID。

-

Flow Control Options

基于优先级的流控制,此选项允许根据数据包的优先级来启用流控制,以优化网络拥塞和流 量管理。但请注意,这个选项只能在处理器模式被禁用时启用。

Statistics Counter Options

选择此选项以启用统计计数器,这些计数器可以跟踪网络流量、错误等统计信息。

-

Enable Statistics Counters( 允许重置统计信息 ):通过选择此选项,可以启用重置统计计数器的功能。

-

Allow Statistics to be reset:启用统计复位功能。这个功能允许系统管理员或用户清除或复位设备、应用程序或系统上的统计数据,以便重新开始收集或恢复到初始状态。

-

Statistics Counter Width( 统计计数器宽度 ):选择统计计数器的位宽,以决定其可以计数的最大值。

-

Frame Filter Options(帧过滤选项) :启用TEMAC过滤器,这允许用户配置硬件来过滤网络帧,基于特定的规则(如源/目的MAC地址、协议类型等)来减少不必要的网络流量。

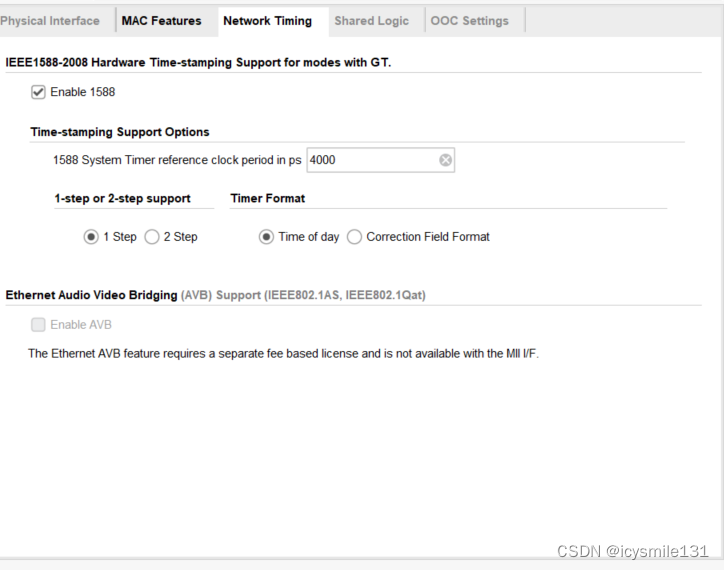

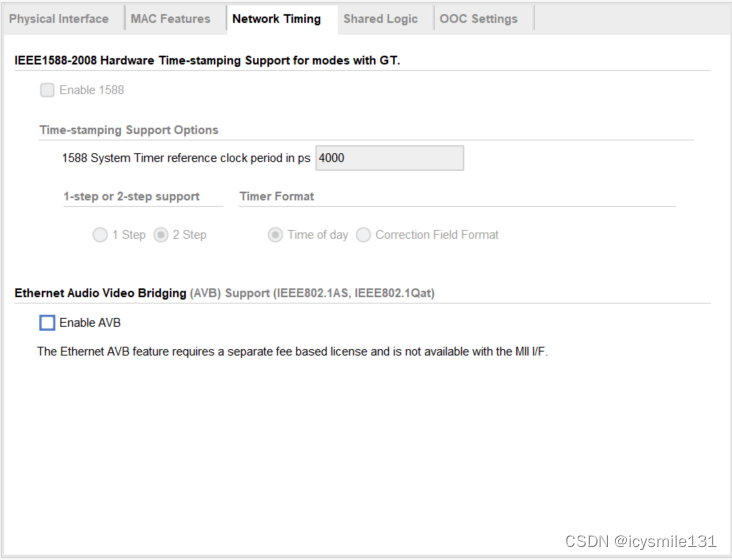

(3)Network Timing

仅当PHY_TYPE在1G和2.5G操作模式下为1000BASE-X或SGMII时,才启用1588选项。此选项卡用于配置1588和AVB模式。此选项卡中提供以下选项:

-

Enable 1588

用于启用设备的1588模式。当选中这个选项时,以下的子选项也将被启用:

① 1-step 或 2-step Support

通过1-step或2-step Support选择1588的1步或2步操作方法。在1步方法中,设备直接与其他支持1588的设备进行时间同步。在2步方法中,设备首先与中间时钟(如一个主时钟或服务器)同步,然后再与其他设备同步。这个选项只有在启用了1588模式后才能被选择。

② 1588 System Timer reference clock period in ps

设置1588系统参考时钟的周期,单位为皮秒(ps)。这个值定义了系统时钟的精度和分辨率。

③Timer Format

Time of Day(ToD)选择时间戳的格式。在1588中,时间戳用于记录事件(如数据包到达或离开设备)的精确时间。ToD时间戳通常用于记录绝对时间,而Correction Field Format时间戳可能包含额外的校正信息。

-

Enable AVB

用于启用Audio Video Bridging (AVB)功能。AVB是一个在以太网上传输音频/视频数据的标 准,它提供了低延迟和高质量的传输。然而,注意这个选项只能在1588模式被禁用时启用。这是因为AVB和1588在某些情况下可能会争夺相同的硬件资源或网络带宽,因此它们通常不会同时启用。

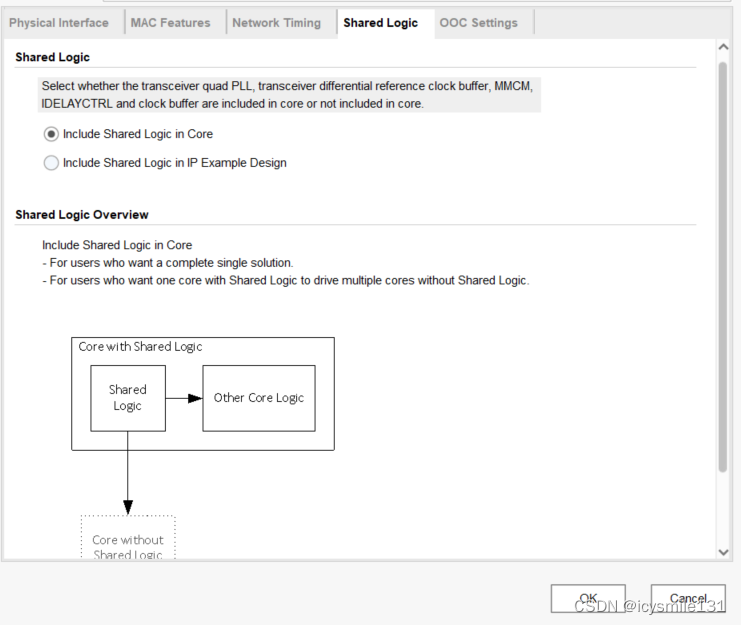

(4) Shared Logic

在以太网接口子系统中,某些组件或逻辑可以被多个接口或通道共享,以减少硬件资源的使用并提高性能。这些可共享的组件通常被称为“共享逻辑”。

-

不同模式下的共享逻辑

GMII模式:IDELAYCTRL 是共享的元素。IDELAYCTRL 通常用于控制延迟,以确保数据在传输过程中的精确对齐。

RGMII模式:IDELAYCTRL 和与 Artix®-7 或 Kintex®-7 设备相关的TX MMCM及其时钟缓冲区是共享的。MMCM 通常用于生成和调整时钟信号。

MII模式:没有可共享的逻辑。

SGMII模式:根据具体的配置(如使用收发器模式或1000BASE-X模式),可共享的元素可能包括收发器差分参考时钟缓冲区、MMCM和时钟缓冲区。

配置以太网接口子系统时,用户可以选择Include Shared Logic in Core来决定是否包含这些共享逻辑。这取决于系统的具体需求、硬件资源和性能要求。

-

GT in IP Example Design

该选项只有在选择“Include Shared Logic in IP Example Design”时有效。这个选项主要用于UltraScale™和UltraScale+™架构的设计,并涉及到以太网收发器(transceiver)的放置和控制,即原本位于IP核级别的收发器会被移动到支持级别实例。这意味着收发器的逻辑和控制不再直接集成在以太网IP核的主要逻辑中,而是被放置在了一个更低级别或辅助级别的组件中。

由于收发器逻辑被移动到了支持级别,原本可能需要用于直接控制或监视收发器状态的一些额外端口将不再生成。这有助于简化IP核的接口,但也可能意味着用户需要通过其他方式(如间接访问或全局控制信号)来管理和监视收发器的状态。

(5)OOC Settings

在硬件设计和FPGA编程中,OOC模式通常指的是一种设计流程,其中某个模块或组件被单独地综合和测试,而不是在整个系统上下文中。

在这种模式下,为时钟信号指定频率值对于确保设计的正确性和性能至关重要。综合工具使用这些时钟频率值来:

-

确定时序要求:时钟频率决定了信号在电路中的传播时间(即时序)。综合工具使用这些频率值来计算信号路径的延迟,以确保满足时序要求。

-

优化电路:根据指定的时钟频率,综合工具可以尝试不同的实现方式(如门级电路结构、资源分配等),以找到在满足时序约束的同时,也尽可能减少资源使用和功耗的优化解。

-

生成报告:综合工具还可以生成关于设计性能、资源使用、时序等方面的报告,这些报告对于设计者了解设计状态和优化方向非常有用。

-

指导后续步骤:OOC模式下的综合结果通常用于指导后续的步骤,如布局(Placement)、布线(Routing)和仿真(Simulation)等。

需要注意的是,OOC模式下综合的结果可能并不完全反映实际系统中的性能,因为在实际系统中,模块之间的交互和相互影响可能会对性能产生影响。因此,在将OOC模式下的设计集成到整个系统中之前,通常还需要进行进一步的验证和测试。

1658

1658

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?