在vivado设计中,为了方便的使用Block Desgin进行设计,可以使用vivado软件把自己编写的代码封装成IP核,封装后的IP核和原来的代码具有相同的功能。本文以实现24位DA转换(含并串转换,使用的数模转换器为CL4660)为例,介绍VIVADO封装IP核的方法及调用方法,以及DAC转换的详细FPGA设计过程,并提供其已验证过的详细代码(使用Verilog语言)。

1 创建IP核

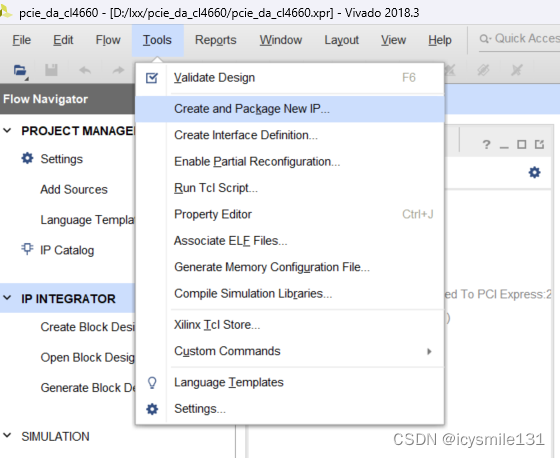

创建一个新的工程,或者打开一个已经存在的工程,点击Tools——Creat and Package New IP...

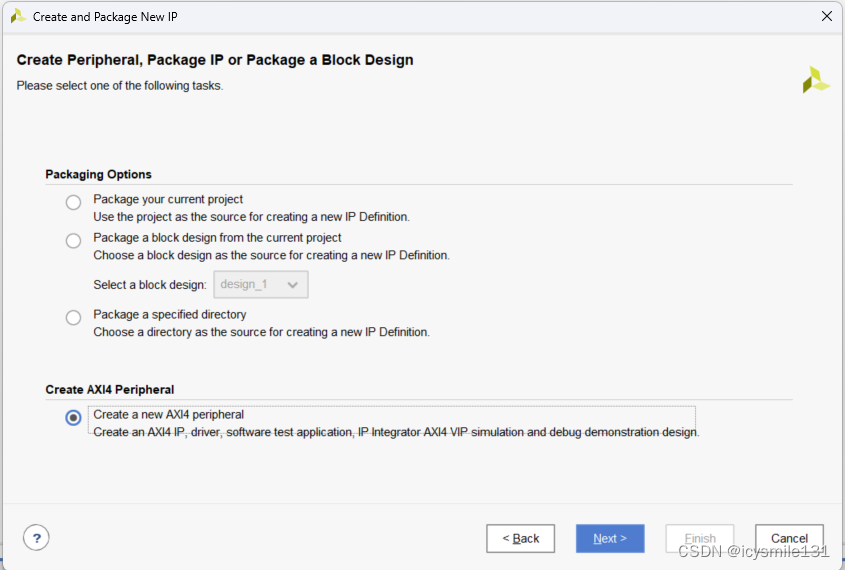

弹出以下对话框,

点击Next,选择Create a new AXI4 peripheral,点击Next,

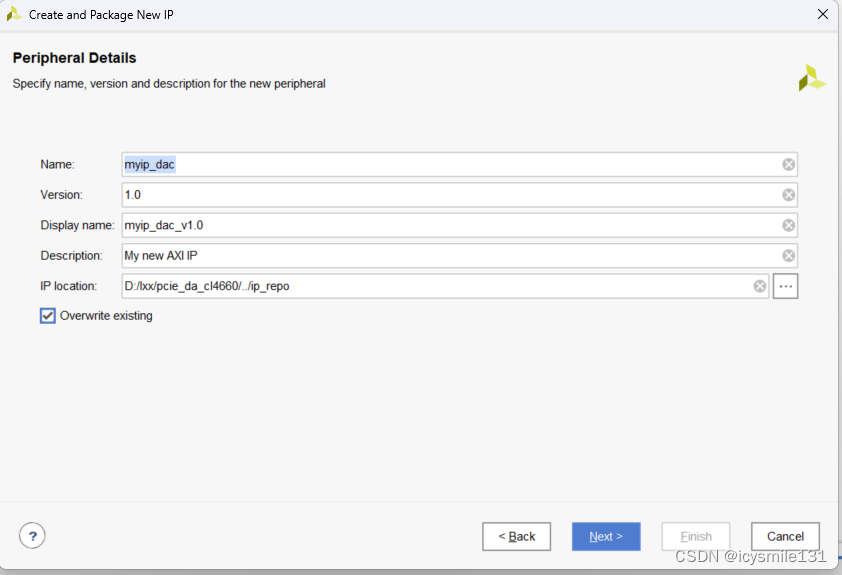

在Name中输入准备生成的IP核的名称,选择Overwrite existing,需要重新生成该IP时,自动覆盖掉原来的设计,

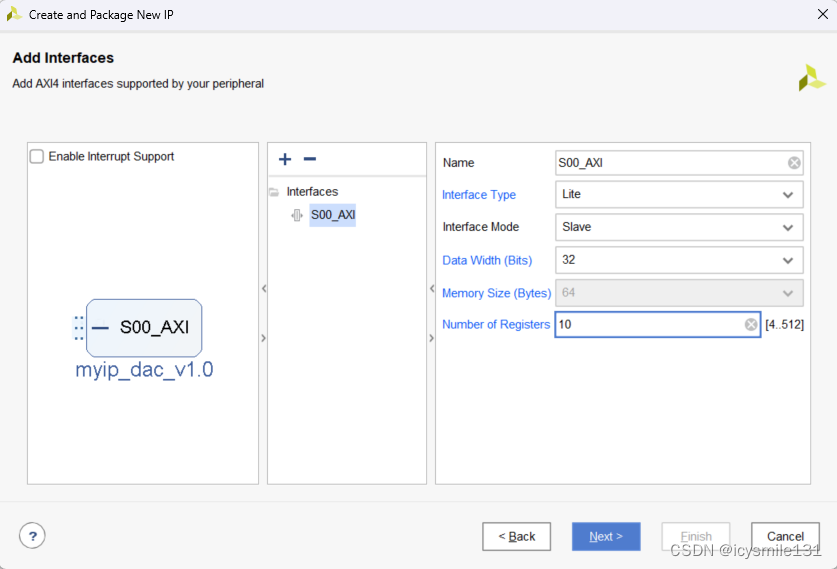

点击Next,Data Width(Bits)为数据宽度,Number of Registers为寄存器的个数,在此需要输入满足设计要求的参数,点击Next,

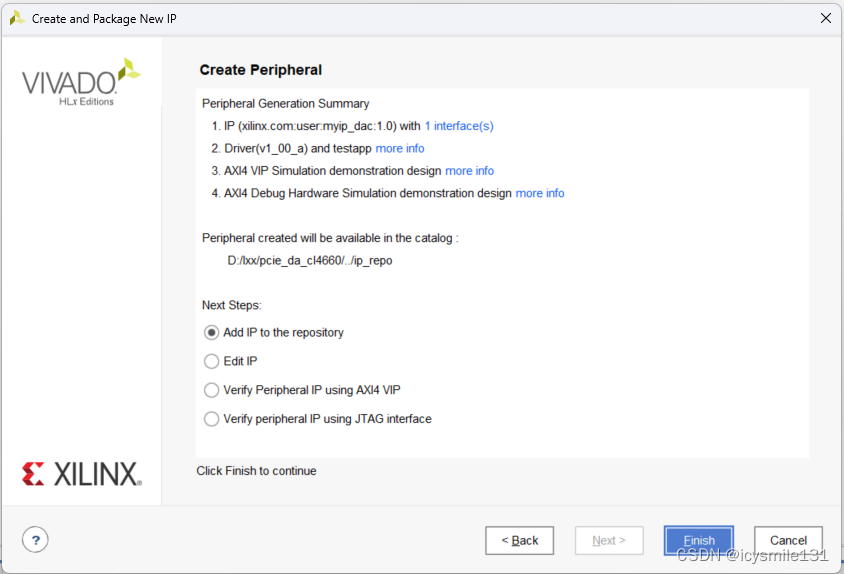

点击Finish,

双击PROJECT MANAGER中的IP Catalog,在右侧的IP Catalog中双击新生成的IP核myip_dac_v1.0,

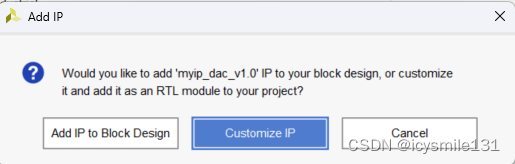

在新弹出的菜单中点击Add IP to Block Design,

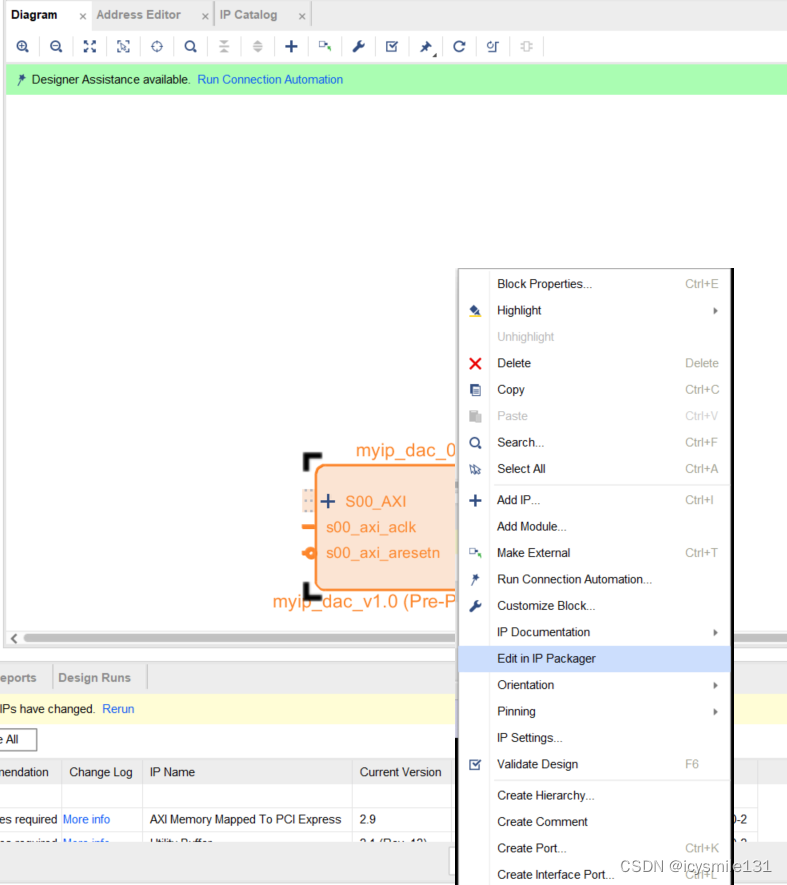

选中myip_dac_v1.0 IP 核,点击右键,在弹出菜单中选择Edit in IP packager,

在弹出菜单中选择OK,即可开始编辑新生成的自定义IP核,

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

553

553

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?