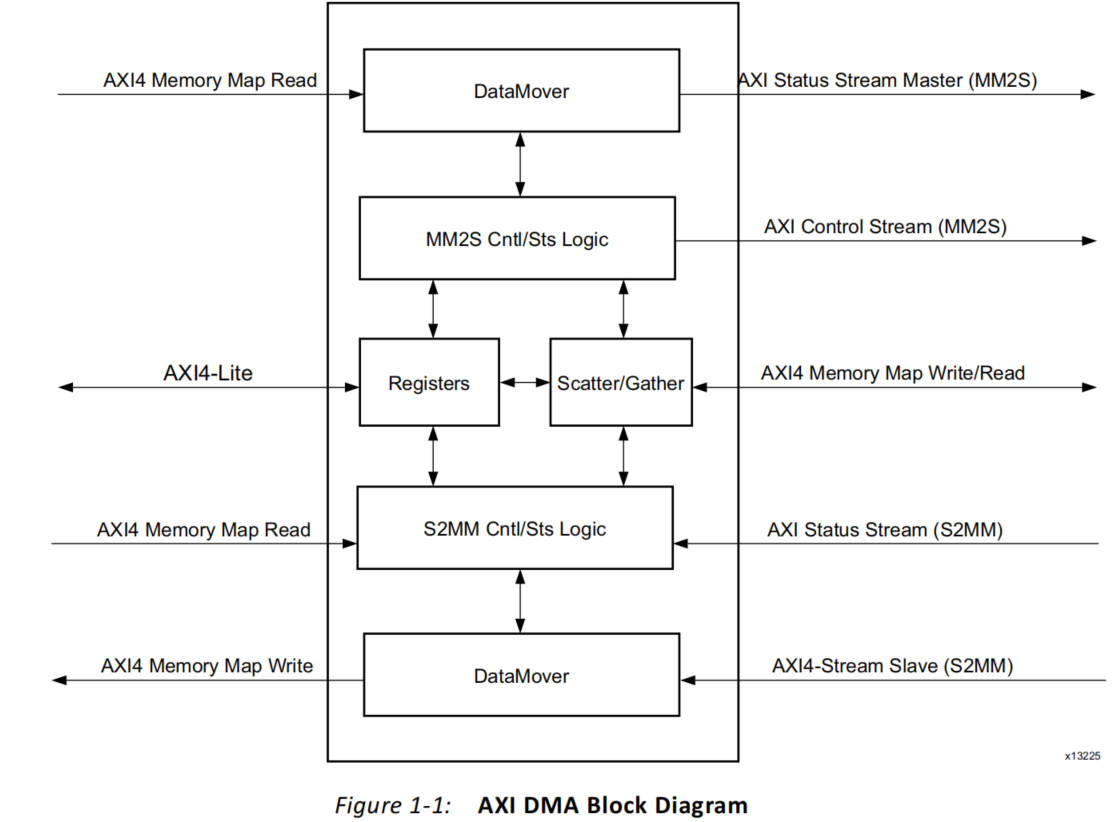

AXI DMA IP核可在AXI4存储器映射接口与AXI4-Stream IP接口之间提供高带宽的直接内存访问。其可选的分散/聚集(scatter gather)功能还能将基于处理器的系统中的数据移动任务从中央处理器(CPU)中卸载下来。初始化、状态和管理寄存器通过AXI4-Lite从接口进行访问。图1-1展示了该IP核的功能组成。

系统存储器与流目标之间的高速DMA数据移动主要通过AXI4读主接口(AXI4 Read Master)到AXI存储器到流(MM2S)流主接口(AXI MM2S Stream Master),以及AXI流到存储器(S2MM)流从接口(AXI S2MM Stream Slave)到AXI4写主接口(AXI4 Write Master)实现。AXI DMA还在Scatter/Gather模式下支持MM2S和S2MM路径上最多16个数据移动通道。

MM2S通道和S2MM通道独立运行。AXI DMA提供4KB地址边界保护、自动突发(burst)划分,以及能够使用几乎全部AXI4-Stream总线带宽能力来排队多个传输请求。此外,AXI DMA还提供字节级数据重新对齐功能,允许内存读写从字节偏移位置开始。

MM2S通道支持AXI控制流,用于向目标IP发送用户应用程序数据。对于S2MM通道,提供了一个AXI状态流,用于从目标IP接收用户应用程序数据。

功能概述

- 符合AXI4规范

- 可选的独立Scatter/Gather直接内存访问(DMA)支持

° 提供从CPU卸载DMA管理工作的功能

° 提供独立于主要数据总线的传输描述符获取和更新功能

° 允许描述符放置在与数据缓冲区分开的任何存储器映射位置。例如,描述符可以放置在块RAM中。

° 提供可选的Scatter/Gather模式下MM2S和S2MM路径上最多16个数据移动通道

° 提供可选的二维(2-D)传输功能

° 提供可选的小孔(keyhole)操作功能 - 可选的寄存器直接模式(无Scatter Gather支持)

通过排除Scatter/Gather引擎,可以启用性能较低但FPGA资源消耗较少的模式。在此模式下,通过设置源地址(对于MM2S)或目标地址(对于S2MM),然后在长度寄存器中指定字节数来命令传输。 - 主要AXI4数据宽度支持32、64、128、256、512和1024位

- 主要AXI4-Stream数据宽度支持8、16、32、64、128、256、512和1024位

- 可选的数据重新对齐引擎

允许在主存储器映射和流数据路径上将数据重新对齐到字节(8位)级别 - 可选的AXI控制和状态流,用于与AXI以太网IP接口

为MM2S通道提供可选的控制流,为S2MM通道提供状态流,以从高带宽数据路径中卸载低带宽控制和状态信息。

Scatter Gather描述符

当AXI DMA控制器配置为Scatter/Gather模式时,S2MM(接收)和MM2S(发送)的分散聚集描述符(Scatter Gather Descriptors)由八个32位基础字(base words)以及0个或5个用户应用字(User Application words)组成。该描述符未来将支持64位地址以及用户应用数据。通过帧起始(Start of Frame)标志和帧结束(End of Frame)标志,可支持每个数据包包含多个描述符。此外,描述符还包含完成状态(Completed status)和传输完成中断(Interrupt on Complete)功能。每个描述符中的缓冲区长度(Buffer Length)可描述的数据缓冲区最大为8 MB。对于两种数据传输方向(MM2S和S2MM),需要分别使用两条描述符链。

描述符管理

在开始DMA操作之前,软件应用程序必须设置一个描述符链。当AXI DMA开始处理描述符时,它会获取、处理并更新这些描述符。通过分析描述符,软件应用程序可以读取相关DMA传输的状态,获取接收(S2MM)通道上的用户信息,并确定传输的完成情况。有了这些信息,软件应用程序就可以管理描述符和数据缓冲区。

软件应用程序处理与已完成描述符相关的每个缓冲区,并重新分配描述符以供AXI DMA使用。为了防止软件和硬件相互干扰,创建了尾指针模式。尾指针由软件初始化为指向描述符链的末尾。这成为硬件的暂停点。当硬件开始运行时,它会获取并处理链中的每个描述符,直到到达尾指针。然后,AXI DMA会暂停描述符处理。软件可以处理并重新分配任何将完成位(Complete bit)设置为1的描述符。AXI DMA会暂停描述符处理。软件可以处理并重新分配任何将完成位(Complete bit)设置为1的描述符。

向TAILDESC寄存器写入的操作会导致AXI DMA硬件(如果它在尾指针处暂停)再次开始处理描述符。如果AXI DMA硬件没有在TAILDESC指针处暂停,那么向TAILDESC寄存器写入数据对硬件没有影响。在这种情况下,AXI DMA会继续处理描述符,直到到达新的尾描述符指针位置。描述符管理必须由软件完成。AXI DMA不管理描述符。

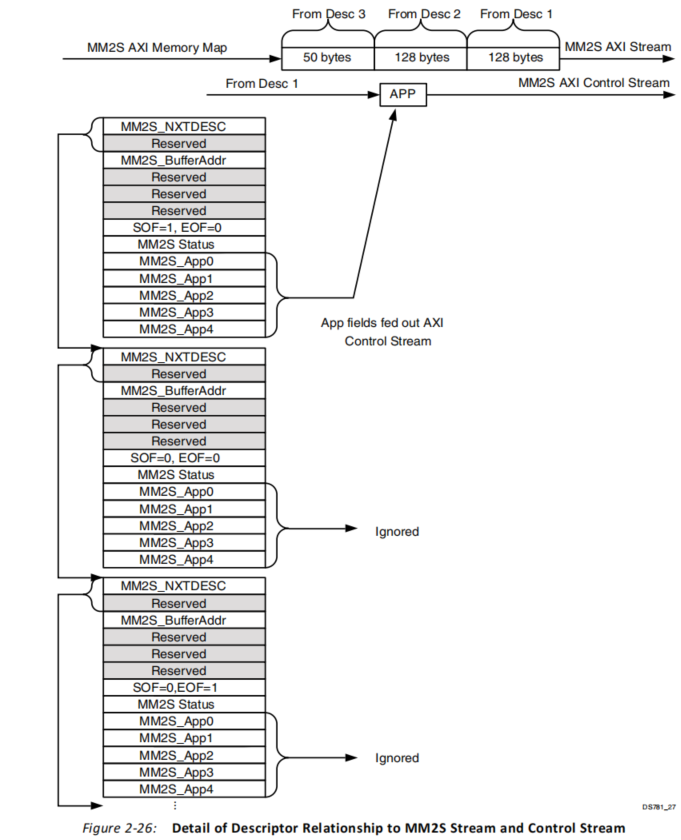

MM2S 描述符设置与 AXI 控制流

描述符 SOF(起始帧)/EOF(结束帧)设置与 AXI 控制流之间的关系如图 2-26 所示。SOF=1 的描述符是数据包的起始,并且会为 MM2S(存储器到流)方向重置 DRE(数据重排引擎,若相关机制中涉及此功能,此处按语境理解补充)。如果启用了状态/控制流,该描述符的用户应用字段也会在 AXI 控制流上呈现。AXI DMA 引擎会忽略 SOF=1 的描述符之后、直到并包括 EOF=1 的描述符之前的用户应用字段。如果禁用了状态/控制流,则 SG(散射收集)获取引擎不会获取用户应用字段。

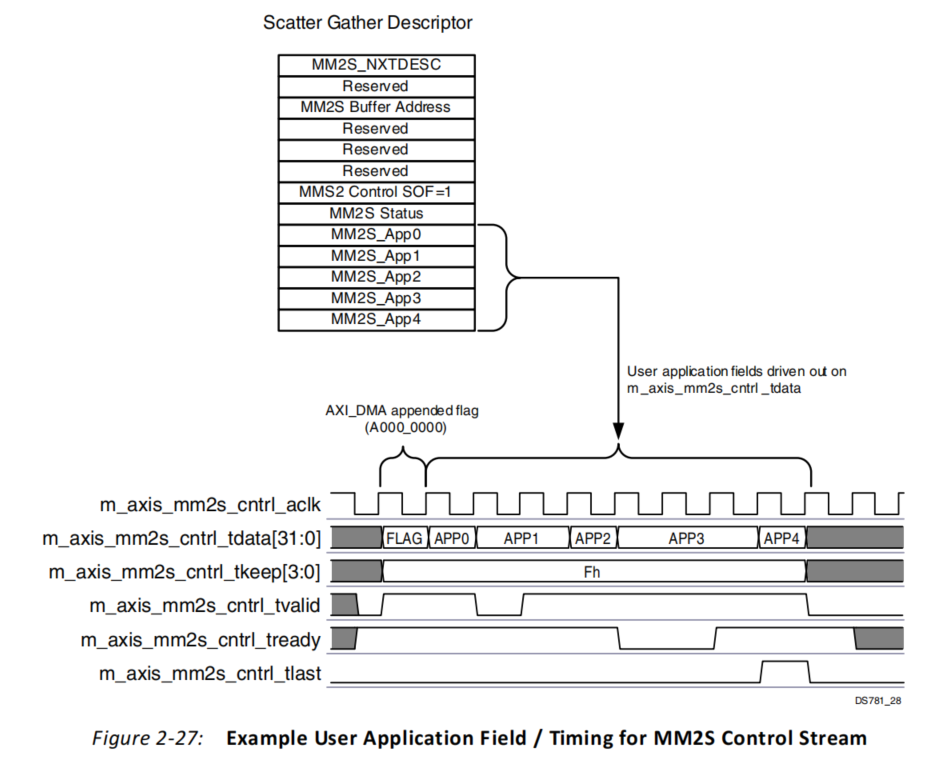

AXI 控制流

AXI 控制流从散射收集描述符提供给目标设备,用于传输用户应用数据。控制数据与 MM2S(存储器到流)主数据流相关联,并且可以在主数据包之前、期间或之后从 AXI DMA 发出。允许目标设备进行流量控制(节流),AXI DMA 也可以进行流量控制。图 2-27 展示了如何在 AXI 控制流上呈现描述符用户应用字段的一个示例。AXI DMA 会向目标设备插入一个指示数据类型的标志。该标志作为第一个字发送。对于以太网,控制标签在第一个字的最高 4 位(MSBs)中为 0xA。

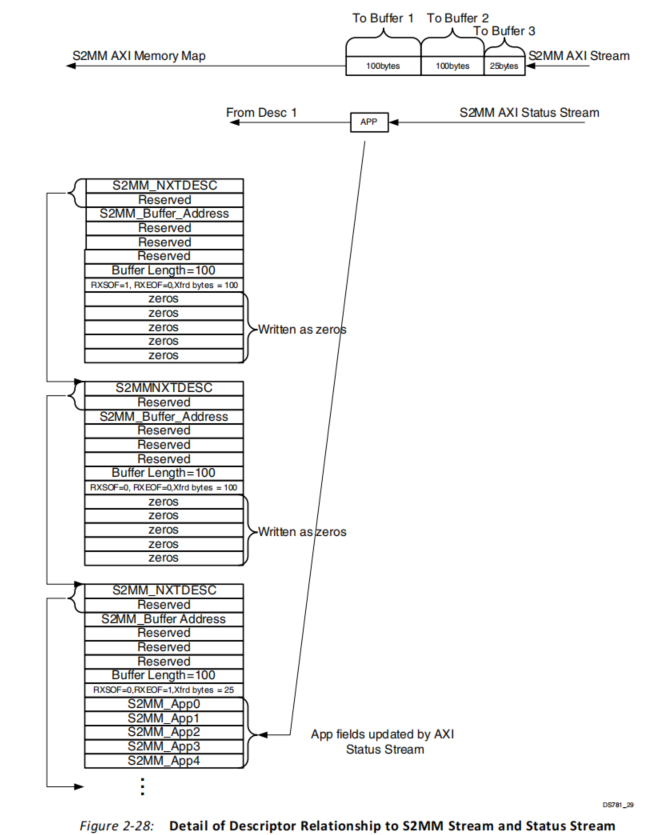

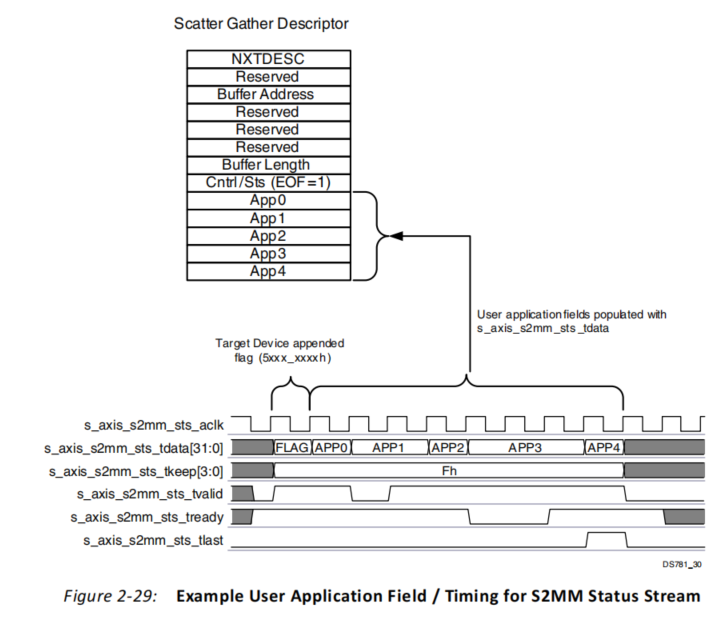

S2MM 描述符设置与 AXI 状态流

描述符 RXSOF(接收起始帧)/RXEOF(接收结束帧)设置与 AXI 状态流之间的关系如图 2-28 所示。RXSOF=1 的描述符描述了包含接收数据包首部分的缓冲区。RXEOF=1 的描述符描述了包含接收数据包尾部分的缓冲区。

为确保正常操作,软件必须指定足够的缓冲区空间(即,描述符链中每个描述符的缓冲区总长度之和)大于或等于所接收的最大数据包大小。

如果包含了Status/Control Stream,则接收到的状态会存储在设置了 RXEOF 的描述符的用户应用字段(APP0 至 APP4)中。

特定缓冲区中已接收并存储的数据的实际字节数会更新到相关描述符的“已传输字节数”(Transferred Bytes)字段中。软件可以通过从 RXSOF 到 RXEOF 遍历描述符,并将“字节已传输”(Bytes Transferred)字段相加来获取总字节数,从而确定接收了多少字节。对于在状态流中提供总长度的应用,该值会存储在 RXEOF=1 的描述符中用户定义的应用位置。

AXI 状态流

AXI 状态流用于将目标设备的状态传输到分散聚集描述符中用户应用程序数据字段。状态数据与 S2MM(流到内存)主数据流相关联。如图 2-29 所示,状态包会更新到检测到的描述该数据包的最后一个描述符(RXEOF = 1)的应用程序字段中。通常,状态流应在 S2MM 数据流的开始出现。如果“在状态流中使用接收长度”(Use RxLength In Status Stream)被禁用,那么状态流可以在 S2MM 帧期间的任何时间出现。

只有在接收到整个状态流时,才会进行 EOF(帧结束)BD(缓冲描述符)更新。

多通道 DMA 支持

多通道模式使 DMA 能够连接到流式传输侧的多个主设备和从设备。添加了一组与源和目标信号相关的新信号。它们是:

• TID - 5 位信号。提供流标识符,可用于区分在同一接口上传输的多个数据流。

• TDEST - 5 位信号。为数据流提供粗略的路由信息。

• TUSER – 4 位信号。用户定义的边带信号。

Scatter Gather模式(C_INCLUDE_SG = 1)

新增了描述符字段以支持多通道和二维传输。如AXI DMA多通道操作中所述,AXI DMA支持高效的二维内存访问模式,可通过AXI4-Stream通道传输二维数据块。内存访问模式由三个参数控制:HSIZE(水平大小)、VSIZE(垂直大小)和STRIDE(步长)。通过数据包起始(Start of Packet)和数据包结束(End of Packet)标志,支持每个数据包包含多个描述符。

在此模式下,IP定制图形用户界面(GUI)会禁用状态/控制流,并且发送(TX)/接收(RX)描述符不提供单独的应用字(AppWord)字段。

可通过启用多通道模式并在存储器到流(MM2S)和流到存储器(S2MM)路径上选择所需通道数,将AXI DMA设置为多通道模式。

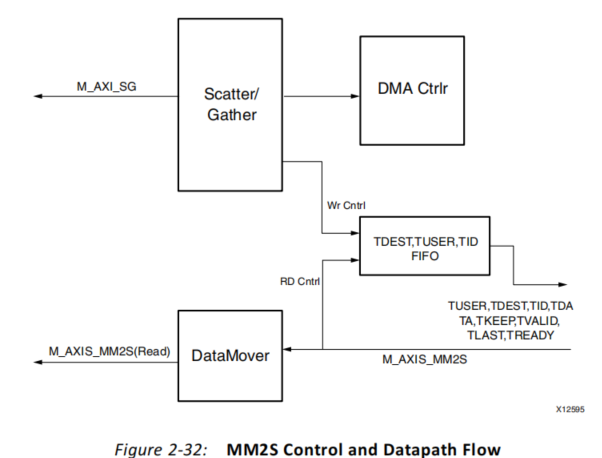

MM2S

MM2S 类似于正常的 AXI DMA 操作。当软件对 MM2S_CURDESC(当前描述符寄存器)和 MM2S_TAILDESC(尾描述符寄存器)进行编程后,AXI DMA 会获取一系列描述符并进行处理,直到到达尾描述符。在 AXI DMA 中,TDEST(目标标识)、TID(事务标识)和 TUSER(用户自定义标识)字段在由描述符定义的整个数据包中假定保持不变。也就是说,每个通过 (TDEST, TID, TUSER) 定义的逻辑通道传输的数据包都会在 DMA 传输另一个数据包之前完成传输。尽管多个通道的数据包传输可以交错进行,但在启动后,每个数据包传输都必须完成之后才能进行下一次传输。在这种假设下,避免死锁场景是你的责任。如果描述符中的 (TDEST, TID, TUSER) 字段不符合这些假设,AXI DMA 不会发出错误信号。保持一致性取决于软件。

在多通道模式下,Tx(传输)描述符包含控制和状态字段。在事务结束时,该描述符上没有关于已传输字节数的状态更新。错误信息会与失败的描述符的当前描述符指针一起记录在寄存器中。可以通过轮询 MM2S_DMASR(DMA 状态寄存器)中的 IDLE 位,或者通过在 MM2S_DMACR(DMA 控制寄存器)中启用中断来得知描述符链传输的完成情况。

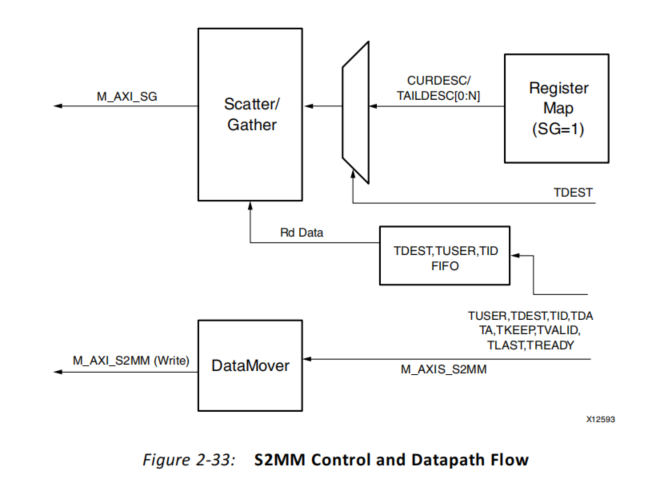

S2MM

TDEST 信号从输入流中采样。DMA 控制器使用该值读取对应的 S2MM_CURDESC(当前描述符寄存器)和 S2MM_TAILDESC(尾描述符寄存器),并将其提供给散射收集(Scatter Gather)模块。该模块进而为该 TDEST 获取一系列描述符。AXI DMA 通过取消断言 TREADY(就绪信号)来保持流数据,直到获取到对应的描述符。然后,AXI DMA 会从缓冲区地址开始写入数据,并持续进行,直到从流端接收到 TLAST(传输结束信号)。

TDEST、TID、TUSER 值从输入流中捕获并存储在内部。这些值在数据包中间不应发生变化。在将该描述符的数据写入到 MM(存储器)侧完成后,这些值以及其他状态位会在链中的每个描述符中进行更新。

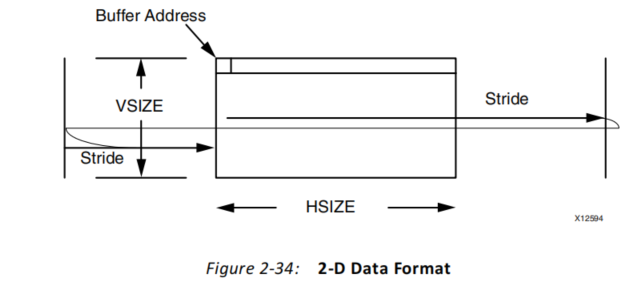

二维传输

在多通道模式下,AXI DMA 支持使用 AXI4-Stream 通道高效传输二维(2-D)内存访问模式。内存访问模式以“行优先”顺序索引到一维地址空间,其中位置 L[行][列] = ADDRESS[行 * NUM_COLUMNS + 列]’。

访问模式通过描述符字段 HSIZE、VSIZE 和 STRIDE 进行控制,这些字段能够启用(隐式)二维数组内子块的传输。HSIZE 指定连续“行”子块的起始地址之间的间距。对于二维传输,HSIZE、VSIZE 和 STRIDE 应按字节对齐。如果 HSIZE、VSIZE 或 STRIDE 的值未对齐,会导致意外行为。

每次读取(MM2S)或写入(S2MM)传输由 VSIZE 次传输组成,每次传输的大小为 HSIZE。每次连续传输的起始地址是前一次传输起始地址(初始时为数据包传输的 BaseAddr)加上 STRIDE 地址。

图 2-34 展示了二维数据格式的示例。

MM2S

读取操作从缓冲区地址开始,由 VSIZE 次读取突发(burst)组成,每次突发读取 HSIZE 字节。每次读取突发的起始地址比前一次突发读取的起始地址大 STRIDE 个地址。

示例:Buffer Address = 08, VSIZE = 06, HSIZE = 256 bytes and Stride = 512 bytes

在此情况下,读取操作从缓冲区地址 08 开始,并继续读取 HSIZE(256)字节。第二行从缓冲区地址 + 步长 = 512 + 8 = 520 开始。它继续读取 HSIZE(256)字节。第三行从 520 + 512 = 1032 开始,第四行从 1032 + 512 = 1544 开始。以此类推,读取 VSIZE 行。

在 AXI4-Stream 上,此数据作为连续的数据包在 m_axis_mm2s_interface 上传输,并在传输的最后一个数据节拍上断言 TLAST 来终止。

S2MM

写入操作从缓冲区地址开始,由 VSIZE 次写入突发组成,每次突发写入 HSIZE 字节。每次写入突发的起始地址比前一次突发写入的起始地址大 STRIDE 个地址。在 AXI4-Stream 上,此数据作为连续的数据包在 s_axis_s2mm_interface 上接收,并在传输的最后一个数据节拍上通过一次 TLAST 断言来终止。

多通道模式的限制

不支持 S2MM 路径上的描述符排队:在多通道模式下,S2MM 路径不支持描述符排队。

不支持 S2MM 路径上的小数据包大小:不支持连续的 4 个或更少数据节拍的小数据包。

仅支持对齐地址和 Hsize 的二维访问:二维访问仅支持对齐的地址和 Hsize。

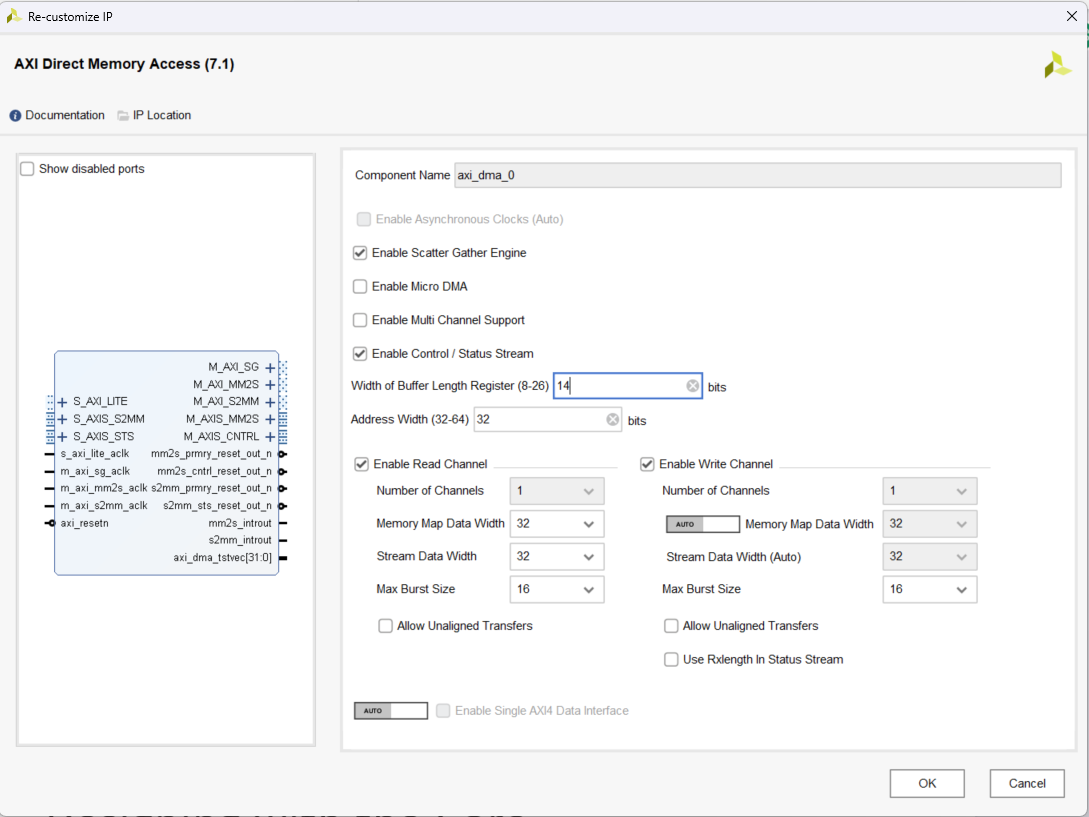

例化IP核

Component Name

为IP核生成的输出文件的基本名称。名称必须以字母开头,并且可以由以下任意字符组成:a 到 z、0 到 9 以及“_”。

Enable Asynchronous Clocks

此设置提供了使 MM2S 接口 m_axi_mm2s_aclk、S2MM 接口 m_axi_s2mm_aclk、AXI4-Lite 控制接口 s_axi_lite_aclk 以及Scatter Gather接口 m_axi_sg_aclk 彼此异步运行的能力。当启用异步时钟时,s_axi_lite_aclk 的频率必须小于或等于 m_axi_sg_aclk。同样,m_axi_sg_aclk 必须小于或等于 m_axi_mm2s_aclk 和 m_axi_s2mm_aclk 中较慢的那个。在同步模式下,所有时钟输入都应连接到同一个时钟信号。

Enable Scatter Gather Engine

选中此选项可启用Scatter Gather模式操作,取消选中此选项可启用简单 DMA 模式操作。

Enable Multi Channel Support

选中此选项可启用 DMA 的多通道功能,并允许您为 MM2S 和 S2MM 通道选择通道数量。

Enable Control / Status Stream

选中此选项可启用 AXI4 控制流和状态流。AXI4 控制流允许将与 MM2S 通道关联的用户应用程序元数据传输到目标 IP。AXI4 状态流允许从目标 IP 接收与 S2MM 通道关联的用户应用程序元数据。

Width of Buffer Length Register(8_26)

此整数值指定用于Scatter/Gather描述符中控制字段的缓冲区长度和状态字段的已传输字节数的有效位数。当启用“Use Rxlength In Status Stream”时,它还指定状态流 App4 字段中 RX Length 的有效位数。对于简单 DMA 模式,它指定 MM2S_LENGTH 和 S2MM_LENGTH 寄存器中的有效位数。长度宽度与Scatter Gather描述符中指定的字节数或 App4.RxLength、MM2S_LENGTH 或 S2MM_LENGTH 中指定的字节数直接相关。

一般设置为14(寄存器设置最大为26,即2的26次方64M大小,一般设置为14bit就够用。长度越大,意味着所需要的资源就越多)。

对于MM2S 或者 S2MM 通道,这个值不能小于一次Stream的数据量。

Address Width(32-64)

对于Zynq系统,设置32bit即可。

Enable Read Channel Options

启用AXI DMA读通道。

Number of Channels

默认值为1,不可修改。

Memory Map Data Width

AXI MM2S读数据总线的数据宽度(以bit为单位)。有效值为32、64、128、256、512和1024。数据值越大效率越高。

Stream Data Width

AXI MM2S AXI4-Stream 数据总线的数据宽度(以bit为单位)。此值必须小于或等于存储器映射数据宽度。有效值为 8、16、32、64、128、512 和 1024。

Max Burst Size

指定 MM2S 的 AXI4-Memory Map侧的最大突发周期大小。换句话说,此设置指定AXI4总线最大支持的Burst数据量。有效值为 2、4、8、16、32、64、128 和 256。这个值越大效率越高,但占用的AXI4总线带宽也越多。

Enable Write Channel Options

启用AXI DMA读通道。

Allow Unaligned Transfers

启用或禁用 MM2S 数据重新对齐引擎(DRE)。选中时,DRE 被启用,并允许在 MM2S 存储器映射数据路径上按字节(8 位)级别重新对齐数据。对于 MM2S 通道,数据从存储器中读取。如果启用了 DRE,数据读取可以从任何缓冲区地址字节偏移量开始,并且读取的数据会对齐,以便在 AXI4-Stream 上输出的第一个字节是第一个有效字节。

注意:如果为相应通道禁用了 DRE,则不支持未对齐的缓冲区、源或目标地址。在 DRE 禁用的情况下具有未对齐地址会产生未定义的结果。DRE 支持仅适用于 64 位及以下的 AXI4-Stream 数据宽度设置。

Use RxLength In Status Stream

如果启用了Control / Status Stream,选中此项允许 AXI DMA 使用由 S2MM 目标 IP 在状态数据包的 App4 中提供的接收长度字段。这为 AXI DMA 提供了预定的接收字节计数,允许 AXI DMA 命令要传输的确切字节数。

704

704

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?