第二篇来聊聊FPGA的硬件调试。

理论上来说,ISE中自带的chipscope也是可以用的,只是很多时候第三方开发板用10pin的JTAG连不上这个,所以还是老老实实用自带的ila(Integrated Logic Analyzer)工具吧。

关于ila的使用相关操作直接百度应该都能找到,只是普遍讲的比较乱,其实就两种常用的操作。

一、直接调用IP核

第一种方式是最常用的,也是我最推荐的,优点是直观形象、移植方便、不容易出错,缺点是只能添加同一个verilog文件内的信号(说不定也可以跨文件?关键是我不会)

在IP里表中搜索ila可以找到这个ip核:

至于这个system ila也不用担心选错了,反正是用不了的。

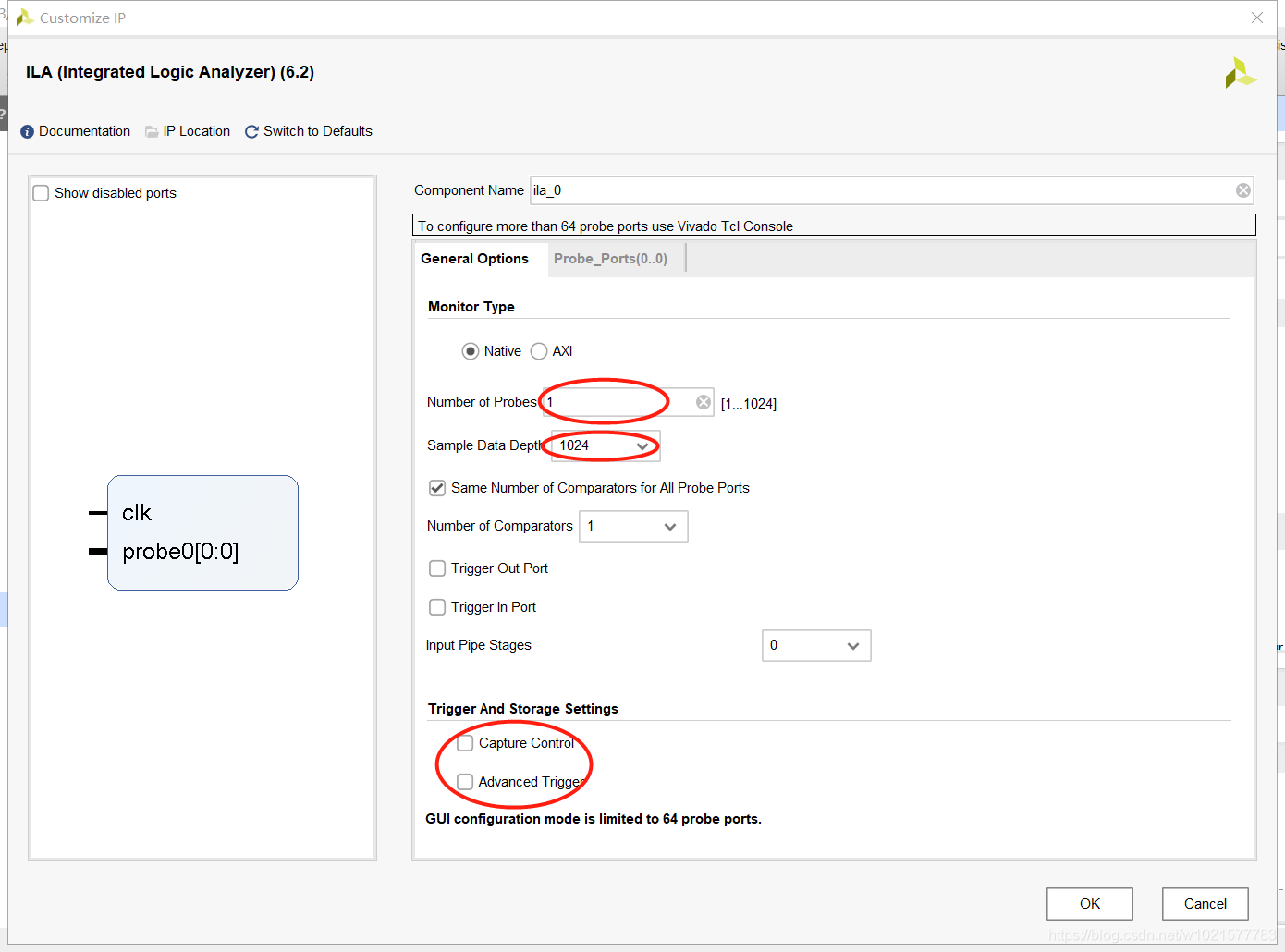

接下来是对ila进行配置,大部分保持默认。

按照项目需求,选好probe数量、采样数、高级触发功能就行了。

关于comparator的数量有什么用我也不懂,默认设置下用了这么久好像也没什么不对。

接下来就是生成ip核,在veo文件里找到例化代码复制过去用就完事了,给个例子吧:

ila_0 ila_inst (

.clk(clk), /

本文介绍了在Vivado中使用ILA(Integrated Logic Analyzer)进行硬件调试的方法,包括直接调用IP核和使用set up debug功能在xdc文件中添加。ILA能直观地观察FPGA内部信号,但其局限性和注意事项也需了解,例如信号选择限制和综合时的信号丢失问题。建议在调试过程中结合使用ILA和mark debug功能,确保调试的可控性和准确性。

本文介绍了在Vivado中使用ILA(Integrated Logic Analyzer)进行硬件调试的方法,包括直接调用IP核和使用set up debug功能在xdc文件中添加。ILA能直观地观察FPGA内部信号,但其局限性和注意事项也需了解,例如信号选择限制和综合时的信号丢失问题。建议在调试过程中结合使用ILA和mark debug功能,确保调试的可控性和准确性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1878

1878

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?