视频:ILA in a Zynq: View signals in hardware!

How to put an ILA into a Zynq device example. An ILA is really useful when you want to see what the signals are doing inside the FPGA so maybe your simulation works but your synthesis doesn't and when you put it in hardware it doesn't work.(本节讲述如何将ILA放入Zynq设备的示例中。当你想看看信号在FPGA内部的作用时,ILA真的很有用,也许你的simulation有效,但你的synthesis无效,当你把程序放在硬件中时,也是无效的。)

ILA(Integrated Logic Analyzer):内置逻辑分析仪。

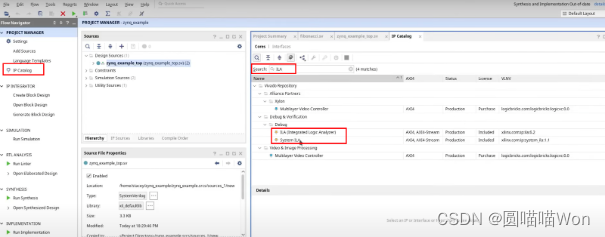

system ILA:is for the block diagram for an AXI bus. 如果想在AXI总线上添加ILA,使用这个。

ILA:放在代码里的ILA。

这个例子里选择ILA。

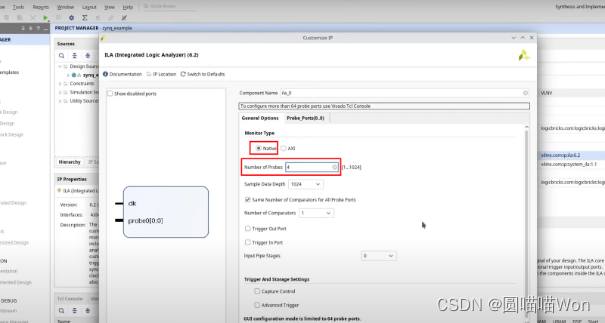

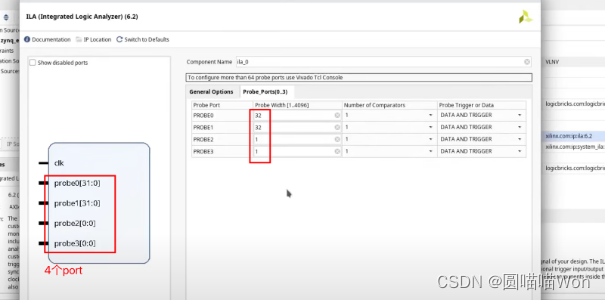

类型选择native,因为不是要探测AXI接口;probe数量选择4,因为要探测4个信号。

ILA的作用是使我们能够在硬件运行过程中看到fpga内部的这些信号,这些信号被build到bitstream中。

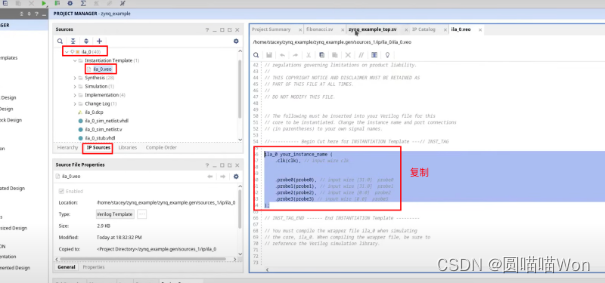

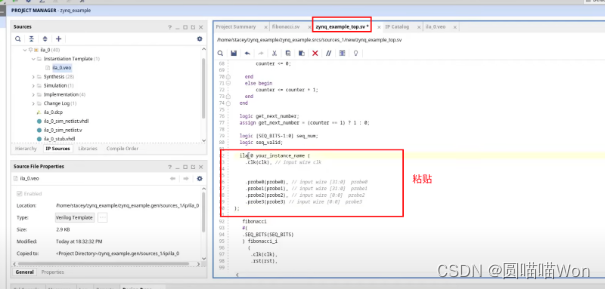

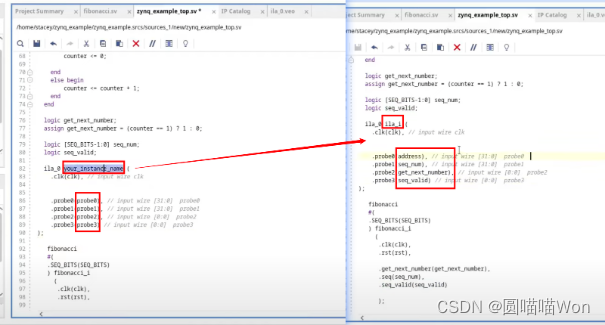

修改实例名,并填入参数:

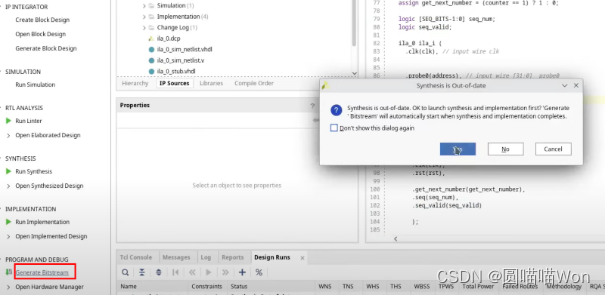

生成bitstream,在运行时debug FPGA:

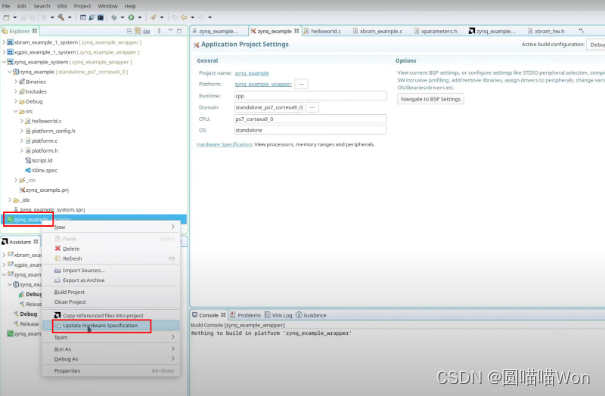

导出xsa文件,launch Vitis,右键更新硬件规范,导入刚刚导出的xsa文件:

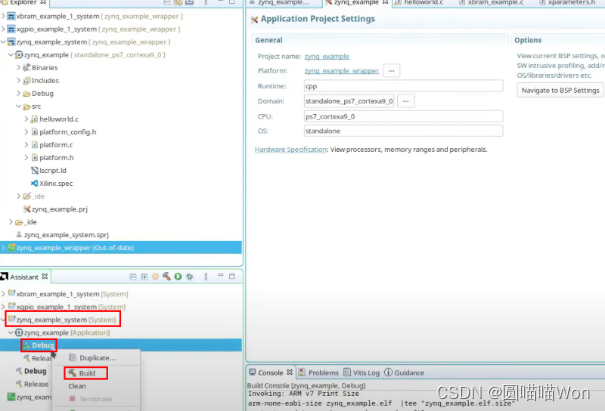

右键编译:执行这一步时,整个stack都会被编译,包括zynq_example_wrapper。

连接FPGA,将zynq_example烧录到FPGA中。

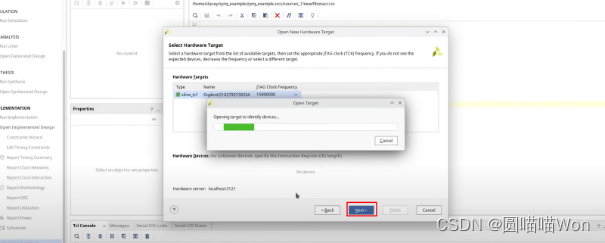

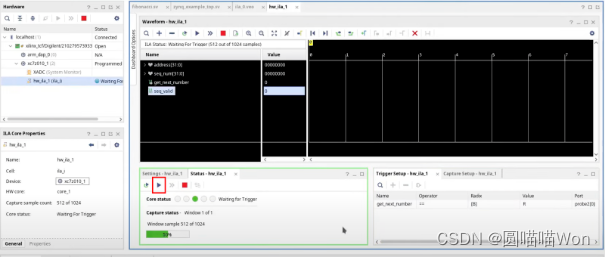

返回Vivado,右下角program and debug菜单选择open target。

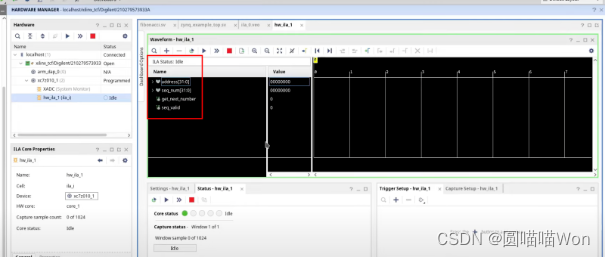

可以看到Vivado发现了ILA以及我们之前设置使用ILA探测的信号:

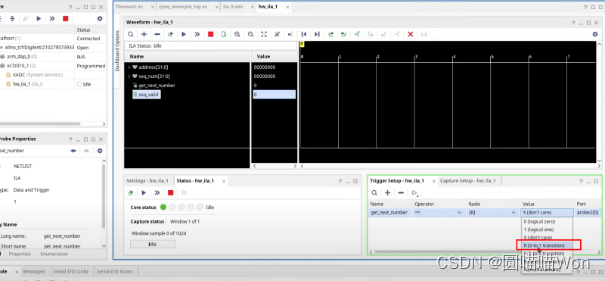

下一步是要选择要被触发的信号:

设置信号的值(想要一个上升沿):

运行:

这样做是因为在FPGA中有一个RAM缓存,当设置好触发信号并且触发该信号时,那些时钟周期信号被存入硬件的RAM缓存中,然后它们通过JTAG被offload到PC中。因此以这种方式可以看到FPGA中信号的值,这也是ILA的工作原理。

此外,如果板子不是Zynq,是其他没有PS(CPU)的板子,步骤也是相同的,只是省略VItis那一步,只需要在Vivado中program设备即可。

6876

6876

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?