什么是代码覆盖率(code coverage)?

代码覆盖率是验证激励是否完备,检验代码质量的一个重要手段。测试激励的代码覆盖率至少要达到95%以上,才能基本认为代码在逻辑上是通过质量控制的。如果代码覆盖率较低,则说明仿真没有执行到所有的代码或者测试文件有缺陷。

ModelSim代码覆盖率功能Code coverage,能报告出statement(语句) 、branch(分支)、condition(条件)、 expression(表达式)、toggle(信号反转)、fsm(有限状态机)等多种覆盖率情况,进一步提高了测试的完整性。

步骤:

1、编译选项(compile options):

在ModelSim的Workspace里选中需要查看代码覆盖率的文件,使用Ctrl键选择多个文件,然后点击右键选择compile->compile prperties->coverage,选择前四项(statement,brances,condition,expression)。

2、编译(compile):

对所选择的文件进行编译,可在命令行窗口敲compile -all,也可在编译菜单里选择compile all。

3、仿真(simulate ):

在命令行窗口输入vsim -coverage work.top,然后run -all

为方便仿真测试和调试程序,在代码覆盖率仿真时应该使用脚本文件,可以使用modelsim直接建立一个do文件,将每一步的指令复制下来粘贴到do文件中就变成了脚本文件,do文件如下(使用脚本编译后图形化界面还是显示?为正常现象不影响后续仿真):

#建库

#vlib work

#映射

#vmap work work

#编译,vcom for VHDL

#vlog -cover bcest *.v

#仿真,不优化

vsim -coverage -novopt work.calendar_tb work.calendar

#执行仿真

run 5500ns

#以txt形式导出覆盖率检测报告

#coverage report -recursive -select bces -file coverage.txt参考自:

Modelsim的脚本仿真流程_modelsim仿真流程-CSDN博客

ModelSim之命令行仿真入门 - hfyfpga - 博客园

modelsim仿真中 do文件的写法技巧_modsim 指令do-CSDN博客

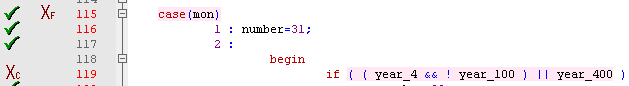

为了提高代码覆盖率,主要从语句、分支、条件表达式来产生有针对性的激励信号,测试信号在功能仿真测试代码的基础上有针对性的进行优化,加入了12个月份的覆盖,将1900.1.1星期1作为了rst后的日期,像下图中这种情况, 表示未执行语句中的false,

表示未执行语句中的false, 表示条件覆盖未完成,可以在X上鼠标点击右键查询详情进行调试。本例中条件互相矛盾无法覆盖所有情况,此情况在设计RTL级代码时应该尽量避免,以免影响总体覆盖率。

表示条件覆盖未完成,可以在X上鼠标点击右键查询详情进行调试。本例中条件互相矛盾无法覆盖所有情况,此情况在设计RTL级代码时应该尽量避免,以免影响总体覆盖率。

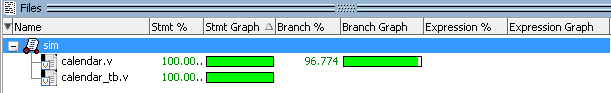

下面是覆盖率检测报告:

Coverage Report Summary Data by file

=================================================================================

=== File: C:/Users/Administrator/Documents/verilog exp/calendar/calendar.v

=================================================================================

Enabled Coverage Active Hits Misses % Covered

---------------- ------ ---- ------ ---------

Stmts 43 43 0 100.0

Branches 31 30 1 96.7

FEC Condition Terms 3 1 2 33.3

FEC Expression Terms 3 3 0 100.0

=================================================================================

=== File: C:/Users/Administrator/Documents/verilog exp/calendar/calendar_tb.v

=================================================================================

Enabled Coverage Active Hits Misses % Covered

---------------- ------ ---- ------ ---------

Stmts 165 165 0 100.0

Total Coverage By File (code coverage only, filtered view): 82.5%

-

Stmts 是语句覆盖,表示测试程序运行后,程序中运行可执行语句的比率

-

Branches 是分支覆盖,表示测试程序运行后,所有判断语句的取真分支和取假分支被执行的比率

-

Conditions 是条件覆盖,表示所有判断语句中的每个条件的可能取值出现过的比率

-

Expressions 是表达式覆盖,表示所有表达式被执行的比率

-

FEC 是 focused expressions/condition 的缩写,FEC Conditions 表示条件表达式中条件分支被执行的比率,FEC Expressions 表示条件表达式中表达式被执行的比率

相关文章:

本文介绍了在ModelSim中实现代码覆盖率仿真的重要性,详细阐述了如何设置覆盖率选项、编译、仿真以及如何解读覆盖率报告,特别强调了在万年历设计中的应用,以提高测试完整性。

本文介绍了在ModelSim中实现代码覆盖率仿真的重要性,详细阐述了如何设置覆盖率选项、编译、仿真以及如何解读覆盖率报告,特别强调了在万年历设计中的应用,以提高测试完整性。

5530

5530

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?