一、后仿介绍

1.概述

后仿是在前仿的基础上加入了延时信息的功能仿真,同时验证了设计的时序以及功能都正确,并且确保后仿功能和前仿一致。前仿与后仿所使用的仿真器是相同的,所加激励也是相同的,不同点主要有:仿真所需文件不完全相同;作用不同;波形不同。

后仿可以分为综合后仿真和布局布线后仿真。综合后仿真是对DC综合后的网表进行仿真,连线延时来自于通过线负载模型的估计;布局布线后仿真是对布局布线后的网表进行仿真,连线延时来自于版图的提取。

为什么有了静态时序分析(STA)还要进行后仿?

后仿也称为动态时序仿真,是对加入了延时信息的网表文件进行的仿真,目的是验证时序以及功能都正确。同步电路的分析采用静态时序分析实现,异步电路的分析则需要运行特殊仿真激励确认。静态时序分析的功能是根据设计规范的要求检查所有可能路径的时序,不需要通过仿真或者测试向量就可以有效的覆盖门级网表中的每一条路径,在同步电路设计中快速找出时序上的异常。动态时序分析主要是指门级的仿真,它主要应用在异步逻辑、多周期路径、错误路径的验证中。随着设计向65nm以下的工艺发展,只用静态分析工具将无法精确验证串扰等动态效应。通过动态时序分析与静态时序分析相结合可以验证时序逻辑的建立/保持时间,并利用动态技术来解决串扰效应、动态模拟时钟网络等问题。

二、仿真所需文件

DC综合或布局布线后生成的网表文件.v和SDF文件.sdf,与综合时所用工艺库db对应的标准单元工艺库.v文件(不区分工艺角),以及前仿所用的测试激励文件testbench.v。

首先

我们应该先集齐上述4个文件:网表文件和sdf文件在综合时生成,标准单元库.v文件在下载的库文件可以找到,前仿真时的tb文件。

标准单元库文件一般有两种,例如分别为smic13_neg和smic13,前者支持neg_tchk负延迟检查,后者不支持。因为hold time check的值是负的, 所以要进行negative timingcheck ,否则默认将会使负值的holdtime check改为0,对hold time负值的检查,在vcs时加上+neg_tchk这个option。

随后

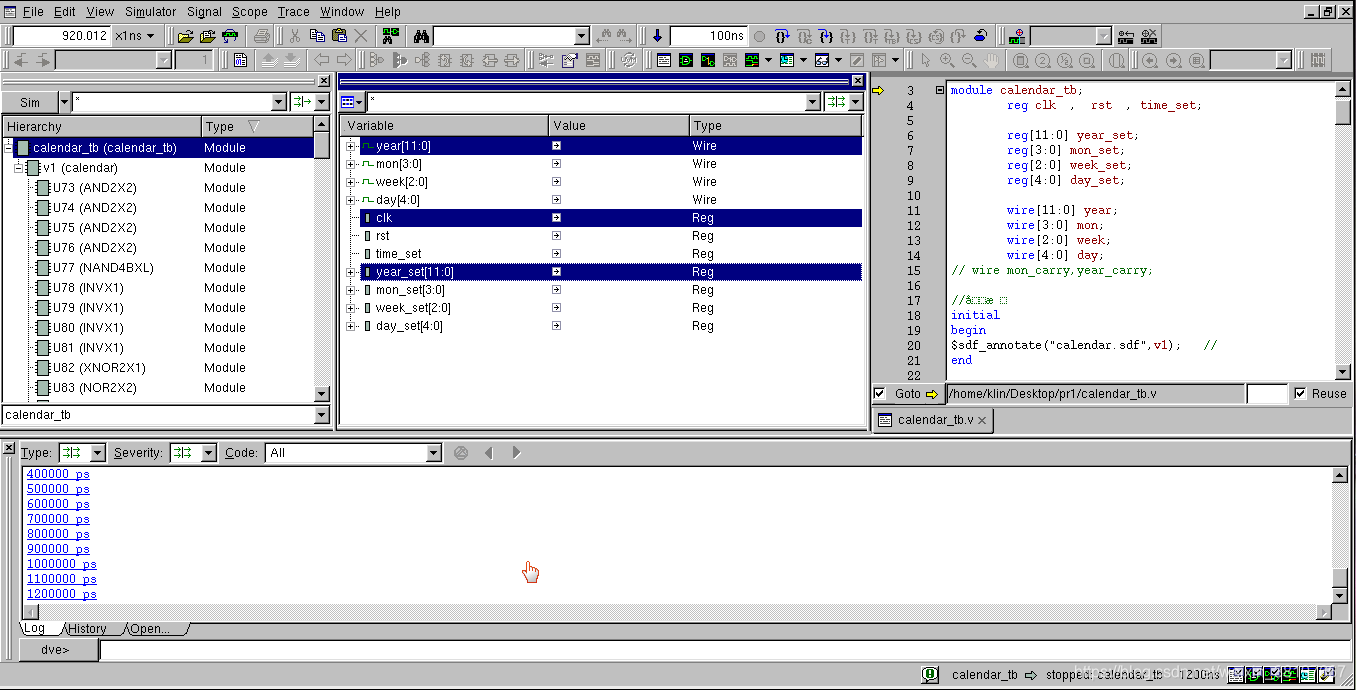

我们在tb文件中加入一段initial反标sdf文件:

//反标

initial

begin

$sdf_annotate("calendar.sdf",v1);

end

calendar.sdf是延时文件的文件名,后面v1是tb文件中实例源文件时起的名字。

最后

我们将三个.v文件使用vcs编译,在这里使用makefile脚本文件执行。

vcs *.v -top calendar_tb -debug_all -R -gui -timescale=1ns/1ps -negdelay +neg_tchk -l run.log

-top设置成tb文件的顶层模块,不知何原因会报错“`timescale是非法的”,在编译设置中加上-timescale=1ns/1ps即可编译成功。

我们选取三个信号观测波形:

输入时间运行后我们可以看到在设置年份命令发出后过了1.64ns年份的值才被改变为7d0,也就是2000年。

真·最后

至此,从设计代码到功能仿真、覆盖率仿真、综合、一致性检查最后进行后仿。历时一学期的时间终于初步掌握了整个流程。

相关文章:

本文介绍了后仿真在电路设计中的重要性,包括综合后仿真和布局布线后仿真。后仿真是为了验证设计的时序和功能,并与前仿结果对比。文章详细阐述了仿真所需的文件,如网表、SDF文件、标准单元库和测试激励文件,并提供了反标SDF文件及使用VCS编译的步骤。通过示例展示了后仿真的波形分析。

本文介绍了后仿真在电路设计中的重要性,包括综合后仿真和布局布线后仿真。后仿真是为了验证设计的时序和功能,并与前仿结果对比。文章详细阐述了仿真所需的文件,如网表、SDF文件、标准单元库和测试激励文件,并提供了反标SDF文件及使用VCS编译的步骤。通过示例展示了后仿真的波形分析。

6158

6158

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?