1.点击file-new project wizard新建工程,工程名字为“cc”,然后next-next,选择cyclone旗下的EP1C2Q24C8芯片,点击next,在simulation一栏,工具名选用“ModelSim-Altera”,类型选择“Verilog-HDL”,再点击finish完成工程的创建。

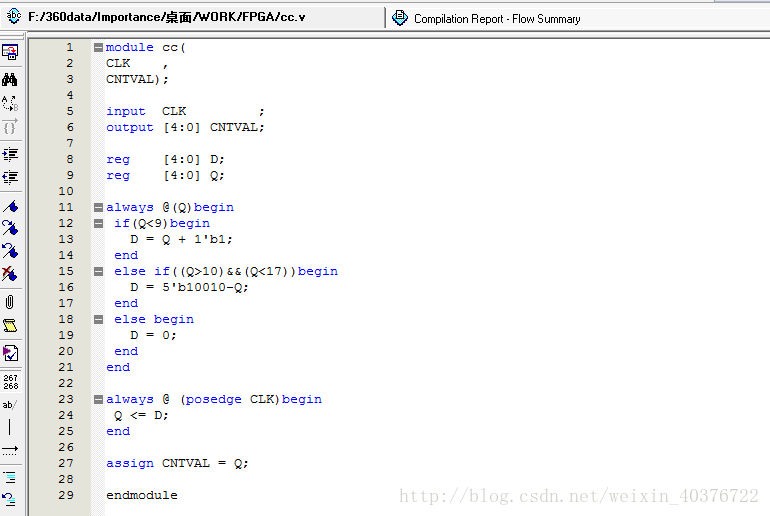

2.点击file-new新建verilog HDL file,输入程序代码,已“cc”的名字保存,如图所示:

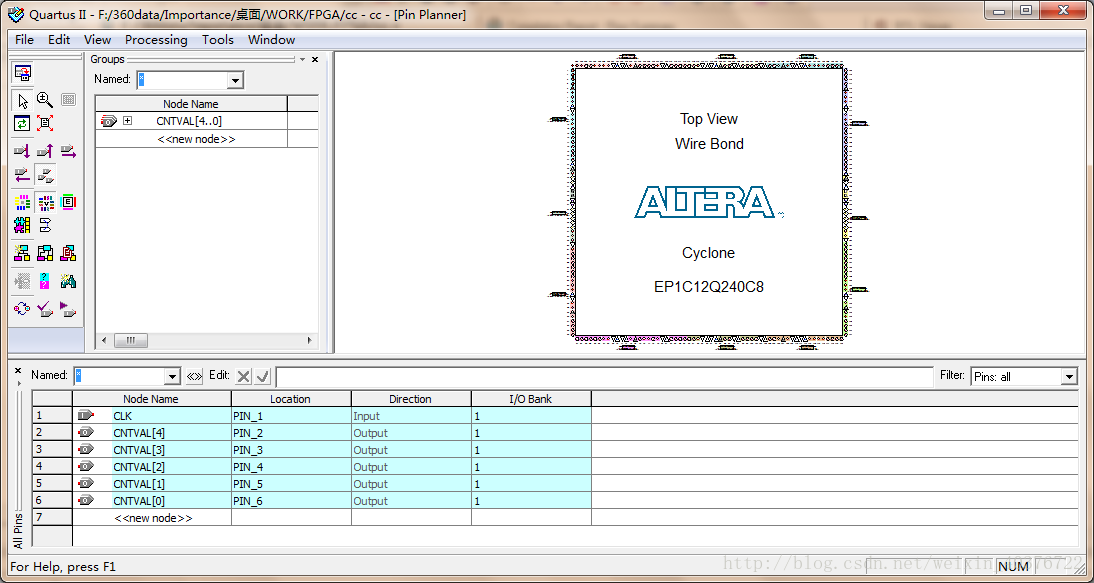

3.将已准备好的文本文档(pin引脚文件)通过assignments-import assignments导入到工程中,并点击assignments-pins查看引脚分布,如图所示:

此时可以查看RTL如图:

FPGA作业2:利用veilog设计循环进制计数器

最新推荐文章于 2023-11-27 21:48:43 发布

这篇博客详细介绍了如何在FPGA项目中设计一个循环进制计数器。首先,通过File-New Project Wizard创建了一个名为'cc'的工程,选择了EP1C2Q24C8芯片并配置了ModelSim-Altera仿真工具。接着,编写Verilog HDL代码并导入引脚文件。在查看RTL视图并设置顶层文件后,进行了编译。然后,创建了一个Vector Waveform File进行仿真,设置输入信号的周期,并进行了仿真操作。

这篇博客详细介绍了如何在FPGA项目中设计一个循环进制计数器。首先,通过File-New Project Wizard创建了一个名为'cc'的工程,选择了EP1C2Q24C8芯片并配置了ModelSim-Altera仿真工具。接着,编写Verilog HDL代码并导入引脚文件。在查看RTL视图并设置顶层文件后,进行了编译。然后,创建了一个Vector Waveform File进行仿真,设置输入信号的周期,并进行了仿真操作。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

9284

9284

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?