学习内容

本文把程序存储在非易失性存储器中, 在上电或者复位时让程序自动运行,这个过程需要启动引导程序( Boot Loader) 的参与。 Boot Loader 会加载 FPGA 配置文件, 以及运行在 ARM 中的软件应用。

开发环境

vivado 18.3&SDK

PYNQ-Z2开发板

Boot和配置简介

在 ZYNQ的启动和配置时, 既需要 PS 的配置信息,又需要 PL 的配置信息。ZYNQ无法纯FPGA像xilinx那样只进行FPGA端口的配置。在 ZYNQ 中, 我们可以理解为PS作为主器件, PL 端口可以看作是 PS 的一个外设,因此需要由 PS 来配置 PL。这个配置顺序的优势是它允许对 PS 单独上电的时候, 此时 PL 不上电,以减小功耗。

在配置文件内FPGA BIT 文件用来定义 PL 的配置信息和操作;而 ELF 文件用于配置运行在 PS 中的程序。

启动流程图

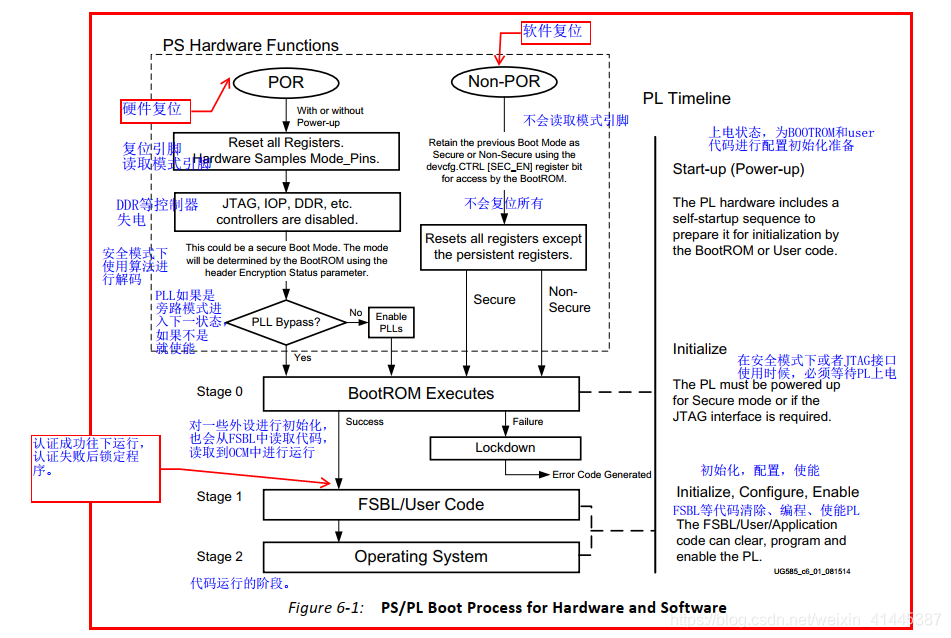

在进行配置时的主要流程,如下图所示。

上图中的Mode_Pins是boot模式的设置引脚,是几个MIO引脚,通过给这几个引脚配置不同的高低电平,进而选择不同的启动模式。完成启动后,这几个IO可以作为ARM的GPIO进行使用。

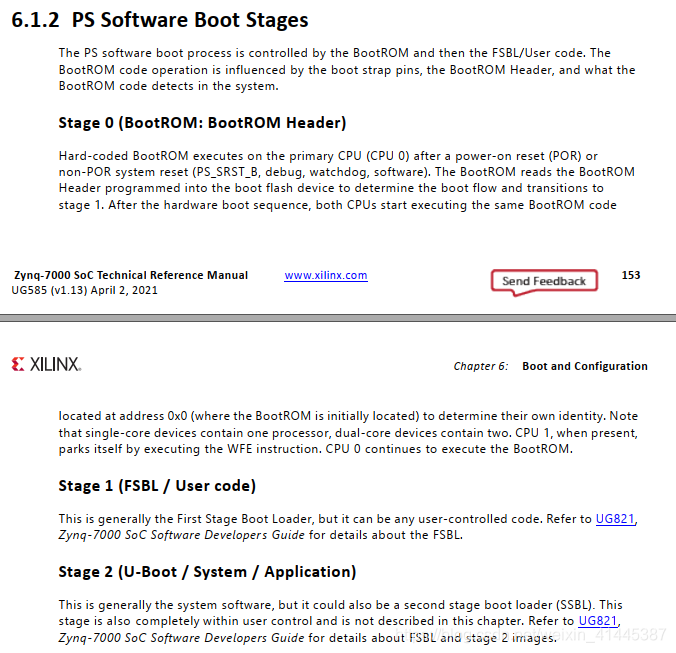

STAGE0阶段是BootROM执行阶段,就是将一些的外设和寄存器进行初始化,从FSBL中读取代码,读取到OCM中进行运行,比如我们从Flash读取后续代码那就需要将flash进行初始化。

STAGE1中,FSBL(用户也可修改,由SDK自动生成模板)执行阶段,FSBL、用户代码执行,就是对更多外设的初始化,比如DDR等。初始化完毕后会从启动镜像中读取bit流来配置PL,加载裸机应用程序到DDR中去运行。

STAGE2为裸机运行阶段。然后运行用户编写好的程序。

BootROM and Header Parameters

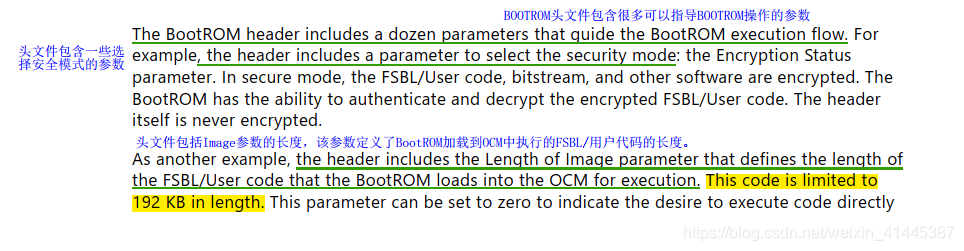

ZYNQ SoC 的启动由片上的 BootROM 开始。片上 BootROM 是 ZYNQ 芯片上的一块非易失性存储器,它包含了 ZYNQ 所支持的配置器件的驱动, 而且里面的代码是不可修改的。 BootROM 中的代码首先会在片外的非易失性存储器中寻找一个头文件, 头文件里定义了一些启动信息, 用于配置 BootROM 的运行。 这些启动信息包括是程序是否就地执行( excute in place) , FSBL 的偏移地址以及是否为安全模式等。头文件的存在确保 BootROM 能够按照配置器件被格式化后的方式操作。

FSBL阶段

BootROM 执行之后,下一个配置阶段被称为 First-Stage Boot Loader( FSBL), 它是由设计者所创建的。FSBL 可以配置 DDR 存储器和硬件设计过程中所定义的一些外设。这些器件需要在加载软件应用及配置 PL之前就初始化完毕。

FSBL 的工作内容:

1、 初始化 PS;

2、 如果提供了 BIT 文件,则配置 PL;

3、 加载裸机应用程序到 DDR 中,或者加载 Second-Stage Boot Loader( SSBL);

4、 开始执行裸机应用程序,或者 SSBL。PL 的配置是通过处理器配置访问接口( Processor Configuration Access Port, PCAP) 进行的,它允许对PL 进行部分配置或者完全配置。有关 PL 的部分配置我们会在其他章节予以介绍。 一旦 PS 启动运行之后,PL 可以在任意时刻被配置, FSBL 和应用程序可以清除、 配置以及使能 PL。

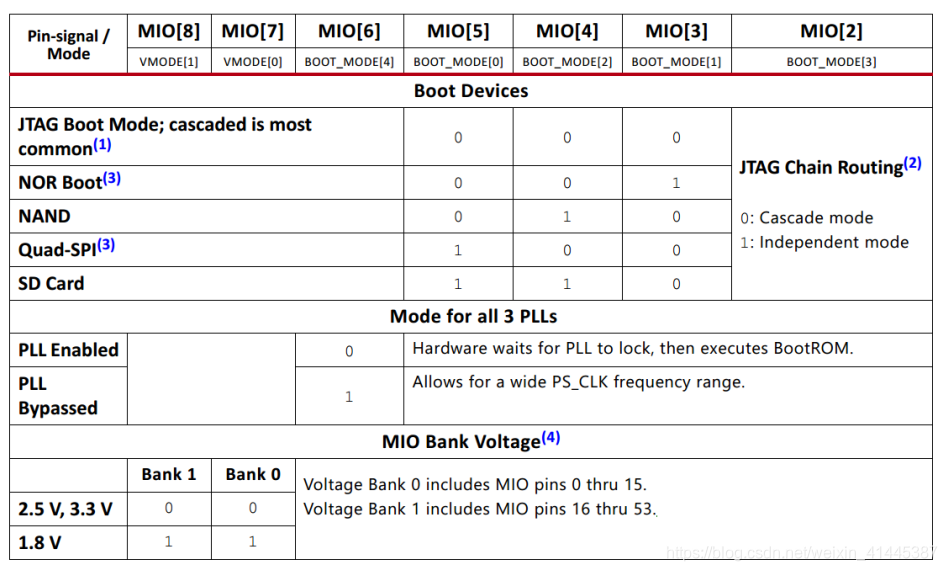

BOOT模式引脚

ZYNQ SoC 使用多个模式引脚来决定配置器件的类型, 软件的存储位置以及其他的系统设置, 这些引脚共享 PS 端的 MIO 引脚。 总共有 7 个模式引脚, 分别为 MIO[8:2]。

其中,前四个引脚定义启动模式,第五个引脚定义是否使用 PLL, 第六个和第七个引脚定义上电过程中 MIO bank0 和 bank1 的 bank 电压。

构建一个 ZYNQ 的启动镜像我们需要以下的文件:

- Boot ROM 头文件:控制 Boot ROM 设置,比如就地执行、 加密、 FSBL 偏移量、镜像文件大小等;

- First-Stage Boot Loader;

- PL 配置文件, 即 BIT 文件;

- 运行在 PS 上的软件应用程序ELF;

PS软件复位阶段

PS软件复位阶段有三个,stage0:BootRom,stage1:FSBL,stage2:运行系统或者裸机代码。

PL硬件复位阶段

PL硬件复位阶段,首先通过PS的端口进行启动模式的设置,设置完成后进行PLL的配置初始化。

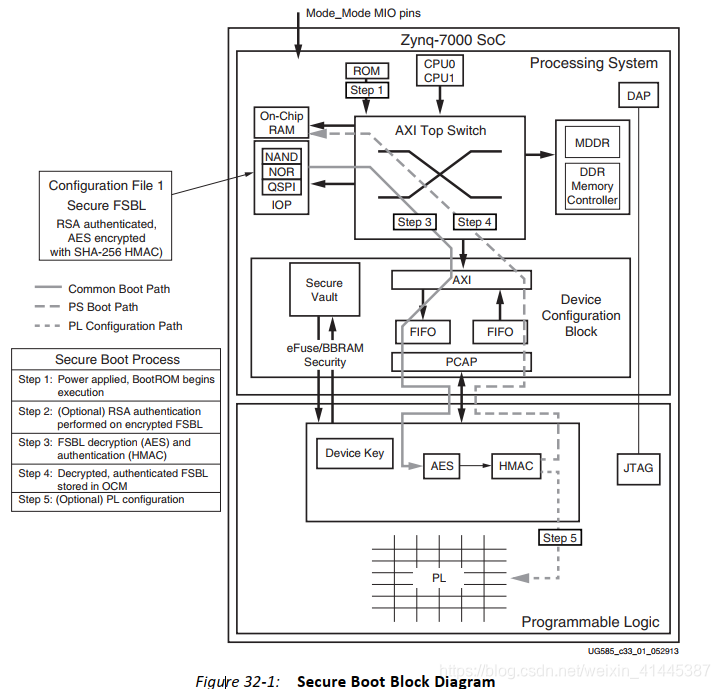

安全启动模式流程图

在安全模式下,启动镜像总是由CPU写入OCM内存。 从那里,它被送 (使用DMA)进、送出AES(Advanced Encryption Standard)/HMAC(密钥相关的哈希运算消息认证码)单元进行解密和身份验证。 解密的引导映像被写入OCM内存,并在引导完成后执行。 也就是每个ZYNQ都有一条解密算法专门这对自己的FLASH进行解密,flash中的代码就只能被本zynq使用。

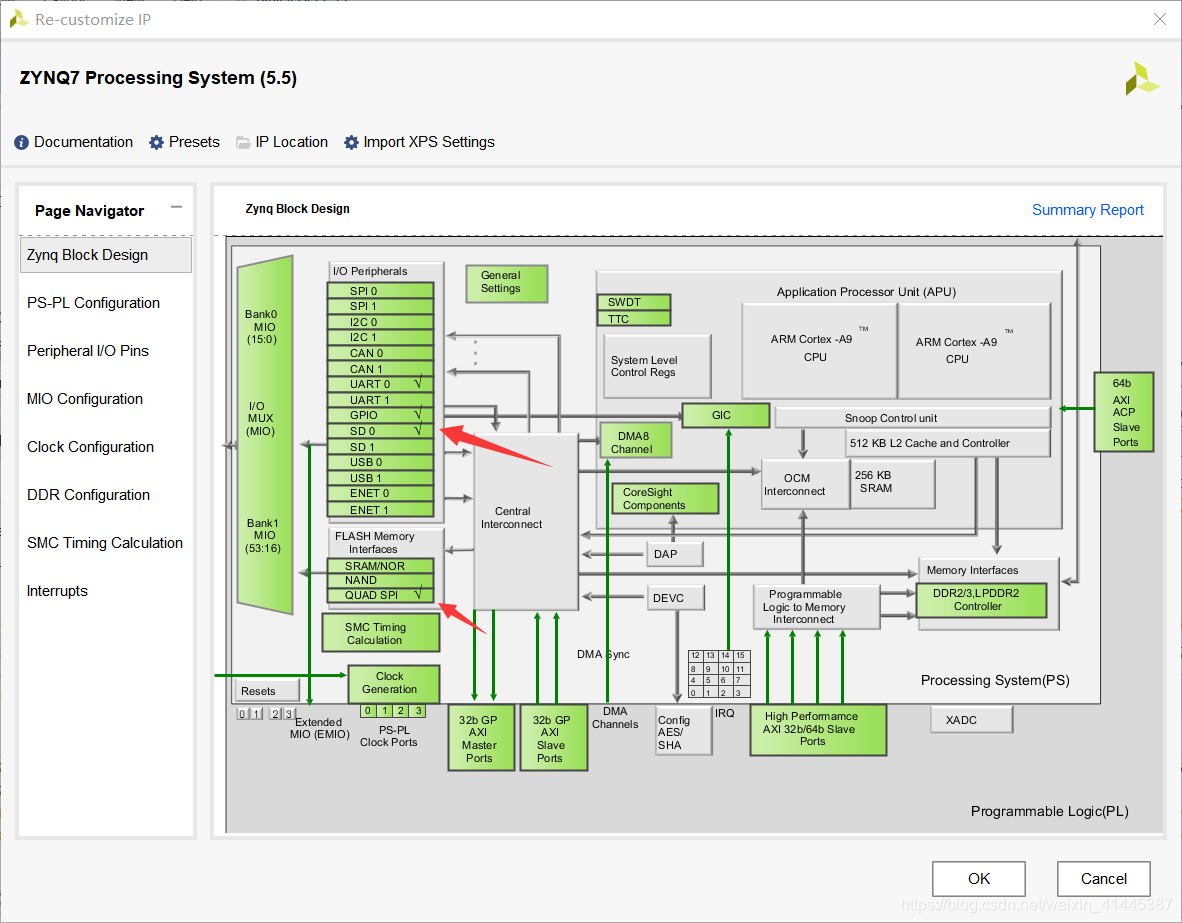

硬件平台搭建

我们随便打开一个工程,因为我们这里要通过使用SD卡和JTAG模式进行下载,所以我们在硬件平台的构建下要进行,勾选SD和 SPI FLASH

然后我们进行generate output product 然后生成HDL封装,完成约束后进行综合布局布线,等待生成bit流文件。bit文件生成后在FILE处,点击导出硬件资源(包含bit流文件),接着launch SDK。

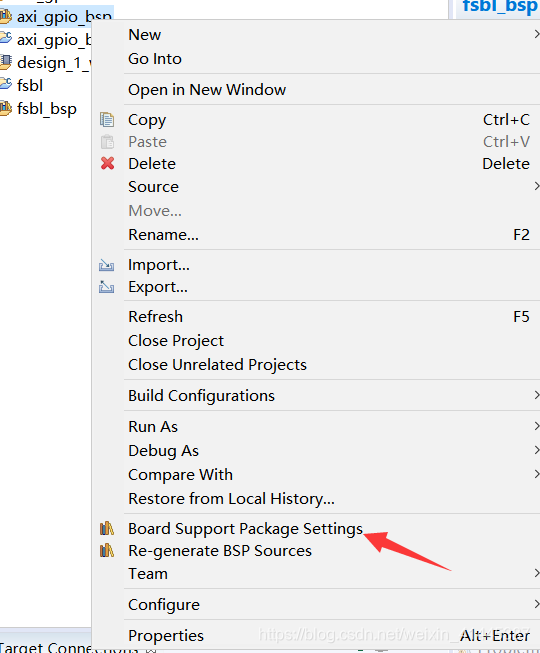

SDK软件部分

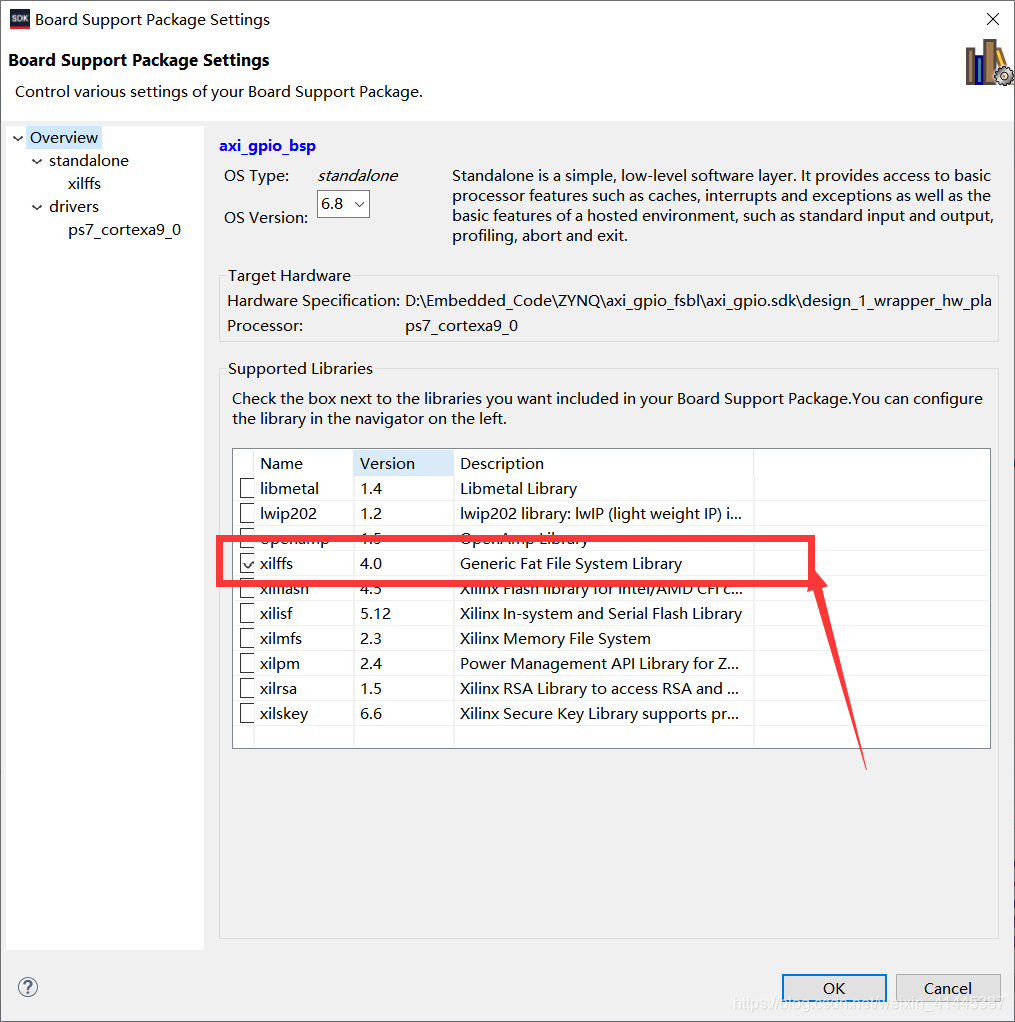

本次使用的是AXI_GPIO的IP的工程进行固化,在打开SDK后,我们需要构建我们的镜像文件用于SD卡启动。选中工程右击选中设置板载支持文件模式。

这里选择xilffs模式,选中后点击OK。

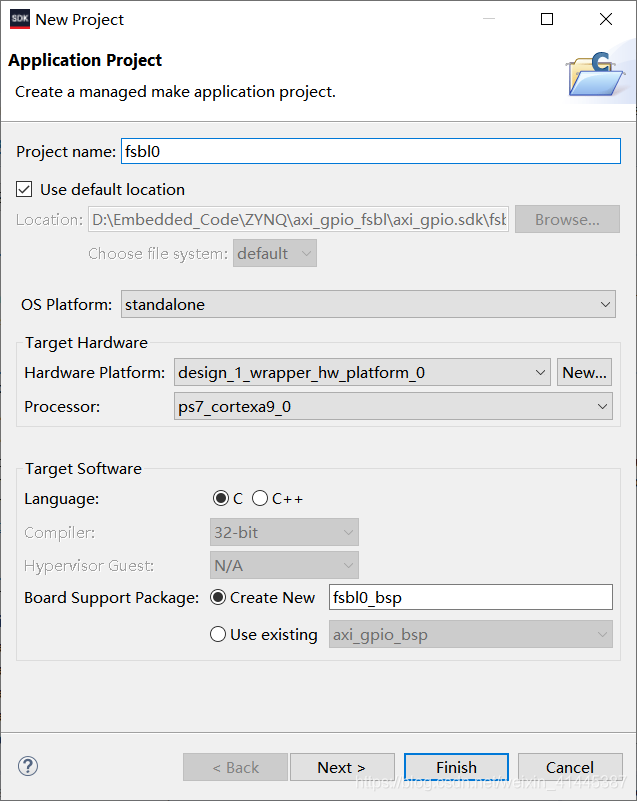

然后新建应用程序

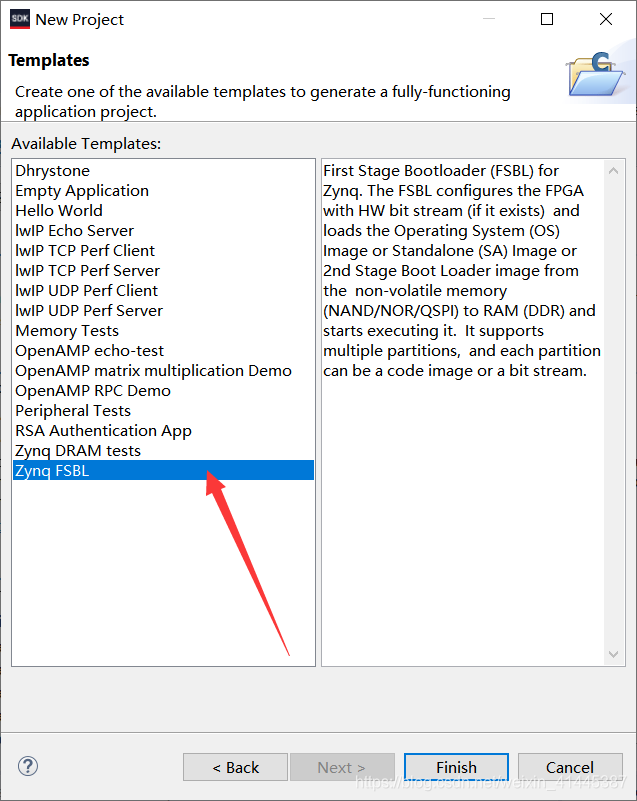

点击next,选中构建FSBL文件

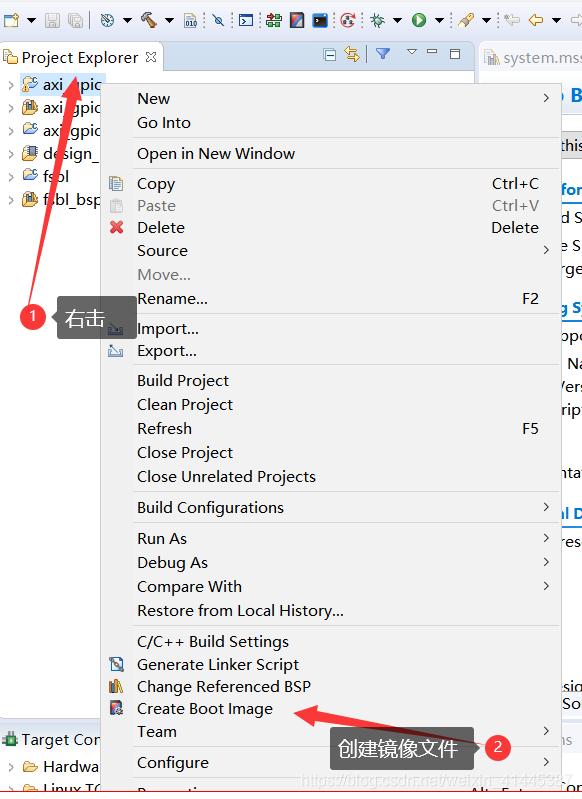

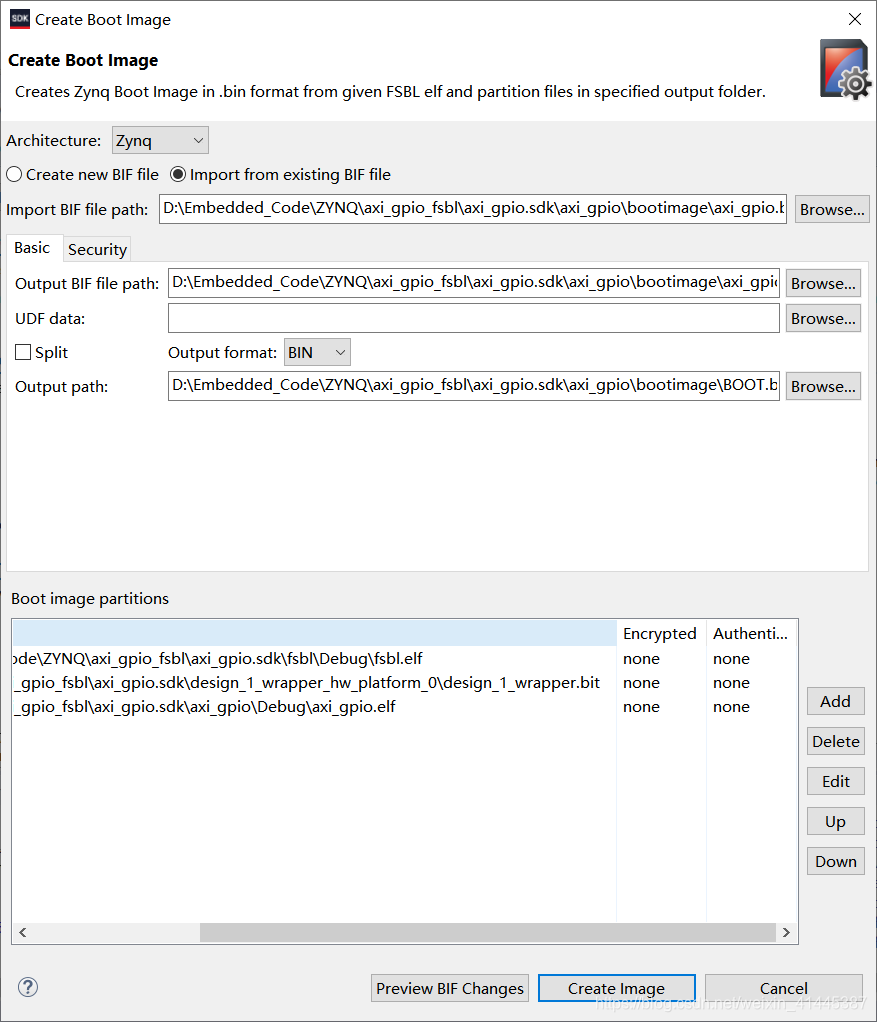

完成创建后等待编译,编译完成后准备创建镜像文件。这里选中axi_gpio的位置,然后点击创建镜像的选项,镜像文件会自动添加进去需要的工程文件,

镜像工程包含fsbl的elf文件,bit流文件,用户编写的应用程序elf文件,如果要自行添加,注意三个文件的顺序。

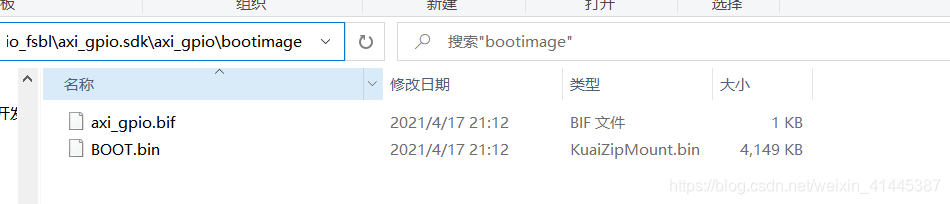

完成后,等待运行,运行结束后即可完成镜像构建。

SD卡运行

把BOOT.bin文件复制到SD卡中,板子的模式配置条线选择SD卡模式,上电运行即可实现我们编写好的程序。

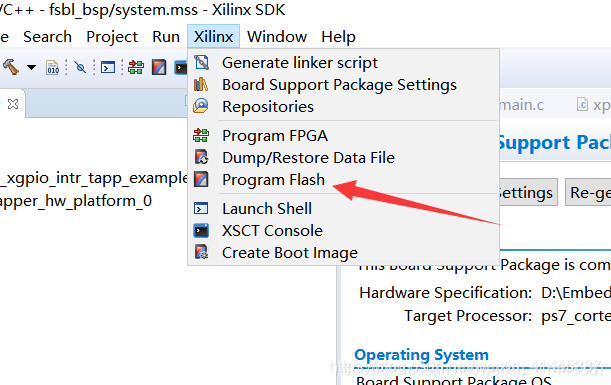

FLASH运行

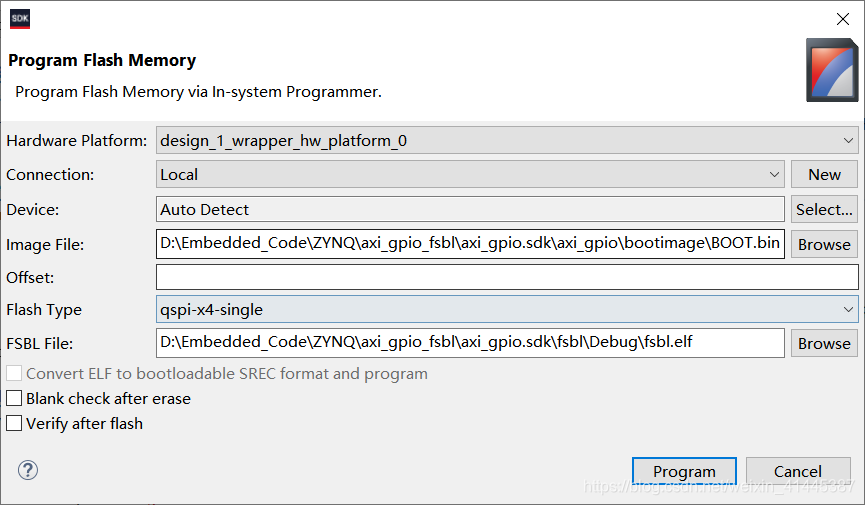

选择编程配置flash,

添加镜像工程和FSBL文件,点击下载编程即可完成下载。这里下载时要跳线接入JTAG模式,下载完成后跳线QSPI,即可从flash中读取我们编写好的程序。

Reference

- 正点原子ZYNQ嵌入式开发指南.

- XILINX文档UG585.ZYNQ-7000-TRM

Vuko公众号同步更新~

欢迎大家关注我的公众号。如果需要工程后台留言即可~

3631

3631

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?