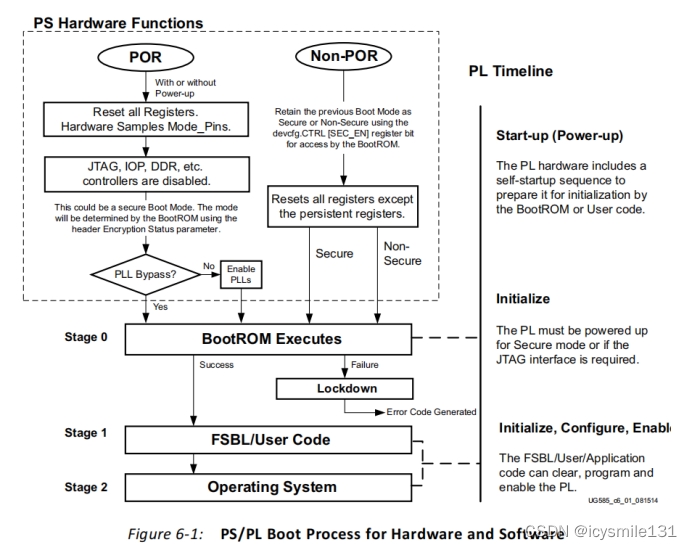

PS_POR_B复位引脚取消置位后,硬件会对引导引脚进行采样,并可选择启用PS时钟PLL。然后,PS开始执行存储在芯片内ROM中的BootROM代码以引导系统。POR(上电复位)会将整个设备重置,不保存先前的状态。非POR类型的复位也会导致BootROM执行,但此时硬件不会采样引导引脚。非POR复位后,一些寄存器值会保留,设备会意识到其先前的安全模式。非POR复位包括PS_SRST_B引脚和几个内部复位源。

PS主引导设备保存一个或多个引导映像。引导映像由BootROM Header(也称为Boot Image Header)和第一阶段引导加载程序(FSBL)组成。引导设备还可以保存用于配置PL的比特流和嵌入式操作系统,但BootROM代码不会访问它们。用于启动的闪存设备可以是Quad-SPI、NAND、NOR或SD卡。

在开发过程中,系统可以在JTAG模式下启动。或者,通过非安全闪存设备启动后,也可以启用JTAG。JTAG始终意味着非安全环境,但它允许访问CPU复合体(APU)中的Arm调试访问端口(DAP)控制器和PL中的AMD测试访问端口(TAP)控制器。这使得开发者能够方便地进行调试和测试,从而加快开发过程并确保系统的稳定性和性能。

1 PS主引导模式(PS Master Boot Mode)

主引导模式就是处理器子系统通过BootROM从闪存设备中读取启动信息,并进行验证,然后把必要的代码加载到处理器的片上存储器中,以便系统能够继续启动和运行。这个过程中,系统的安全性可以根据需要进行配置,既可以是安全模式的,也可以是非安全模式的。

在安全模式下,引导映像始终由CPU写入OCM存储器。之后,它使用DMA在AES/HMAC单元中进行解密和身份验证。解密后的引导映像被写回OCM存储器,并在BootROM完成后执行。

在非安全模式下,BootROM Header可以指示PS直接从支持execute-in-place选项的Quad-SPI或NOR引导设备中执行引导映像。在其他情况下,FSBL/User代码会被复制到OCM存储器以供执行。

如果闪存设备中的BootROM Header无效,BootROM代码会搜索其他的header。header搜索会一直进行,直到找到有效的header或搜索完整个范围。BootROM header搜索支持Quad-SPI、NAND和NOR引导模式。对于SD卡引导模式,只读取一个header。

总的来说,PS主引导模式为系统提供了从闪存存储设备启动的灵活性和安全性,确保系统能够正确、安全地启动和运行。

2 JTAG从属引导模式(JTAG Slave Boot)

是一种特殊的引导模式,其中BootROM代码执行最少的系统配置并启用JTAG接口。然后,系统进入空闲状态,等待DAP(Debug Access Port,调试访问端口)控制器重新启动CPU 0。

在JTAG引导模式中,有两种常见的模式:级联JTAG引导模式和独立JTAG引导模式。在级联JTAG引导模式下,DAP和TAP(Test Access Port,测试访问端口)控制器相互连接,形成循环,这是最常见的JTAG引导模式。而在独立JTAG引导模式下,TAP控制器连接到PL的JTAG引脚,为用户提供了使用TAP控制器配置PL的时间,并将DAP控制器连接到EMIO JTAG接口。

在非安全主引导模式下,当PL上电时,JTAG接口被启用以进行调试。此时,JTAG接口可用于访问TAP和DAP控制器。

JTAG从属引导模式为开发者提供了强大的调试功能,允许他们在开发过程中深入了解和控制系统的内部操作。通过JTAG接口,开发者可以访问和修改PL和PS的内部寄存器,检查系统的状态,甚至实时调试和修改代码。这对于调试复杂的硬件系统和软件应用程序至关重要,特别是在硬件和软件高度集成的现代系统中。

3 启动和配置

上电复位(POR reset)会促使硬件进行一系列操作,包括采样引脚绑带(pin straps)、禁用设备中的模块,以及可选地启用处理器子系统(PS)的时钟PLLs(相位锁环)。这些硬件操作在非POR复位后不会执行。

接下来运行的首个软件是BootROM代码,随后是FSBL/用户代码和系统代码。所有这些步骤都展示在图6-1中。该图是一个详细的流程图,它描绘了设备从启动到运行软件代码的整个过程。在这个流程中,BootROM代码扮演着关键角色,它负责初始化硬件并加载必要的软件代码。FSBL/用户代码随后运行,执行进一步的初始化工作,并最终加载系统代码,使设备能够正常运行。

3.1 BootROM与Header参数

BootROM是APU中首先运行的软件,它在CPU 0上执行,而CPU 1执行等待事件(WFE)指令。BootROM的主要任务是配置系统,将启动映像FSBL/User代码从启动设备复制到OCM,然后将代码执行分支到OCM。FSBL/User代码也可以在非安全环境下直接从Quad-SPI或NOR设备执行。

BootROM Header包含了一系列参数,这些参数指导着BootROM的执行流程。例如,Header中包含一个用于选择安全模式的参数:加密状态参数。在安全模式下,FSBL/用户代码、比特流以及其他软件都会被加密。BootROM具有认证和解密加密的FSBL/用户代码的能力。而Header本身则不会被加密。

BootROM的最后两个功能是禁用对其ROM代码的访问,并将CPU代码执行权转交给FSBL/用户代码。BootROM的执行流程在BootROM流程图部分有详细说明。

简而言之,BootROM头部参数在设备启动过程中起到了关键作用,它们确保了BootROM能够正确地加载和执行所需的代码,并在适当的时候将控制权交给FSBL/用户代码,从而完成整个启动流程。这些参数的设置不仅影响了启动过程的安全性,还决定了代码的执行方式和位置。因此,在配置和使用BootROM时,对这些参数的理解和正确设置至关重要。

3.2 PL初始化和配置

在对PL进行初始化和配置比特流之前,必须首先为其供电。PL的供电和上电启动阶段独立于PS运行,但PL的上电需要与PS的POR复位信号保持一定的时序关系。

PL可以通过GPIOs或串行接口与外部设备连接,从而受到FSBL/用户代码的控制。在内部,BootROM和FSBL/用户代码可以确定PL的电源状态。当PL的电源状态发生变化时,FSBL/用户代码可以接收中断。

PL启动过程包括四个阶段:启动、初始化、配置和启用。启动阶段是在电源上升到稳定状态后自动计时的。初始化阶段会清除PL中的SRAM单元,为比特流的编程(配置阶段)做好准备。然后,在PS软件的控制下启用功能性的PS-PL接口。BootROM代码不配置PL,但可以读取其状态以确定何时启用PL JTAG链,以及何时需要使用HMAC/AES解密硬件。

3.3 安全PS镜像和PL比特流

安全环境从加密的启动过程开始,在这个过程中,PS软件作为系统主控制器,BootROM从选定的闪存设备中读取加密的FSBL/用户代码镜像,并使用基于PL的硬化哈希消息认证码(HMAC)和带有密码块链接模式(CBC)的高级加密标准(AES)模块进行处理。这些模块通过DevC接口和位于PL中的下游处理器配置访问端口(PCAP)从PS访问。

在尝试解密FSBL/用户代码之前,BootROM会验证PL是否已供电。PS执行完BootROM后,FSBL/用户软件可以使用加密的比特流配置PL,也可以在稍后配置或重新配置PL。

低级安全环境从I/O引脚活动和所有可能访问PS操作环境的潜在访问点开始。安全操作环境通过BootROM的执行得到维护,并传递给安全的软件操作环境。

本文详细描述了PS的BootROM引导过程,涉及上电复位、引导引脚操作、BootROMHeader的作用、不同引导模式(主引导和JTAG从属),以及启动时的安全措施,包括PL初始化、加密和PL比特流配置。文章强调了BootROM在启动流程中的关键作用以及JTAG接口在调试中的便利性。

本文详细描述了PS的BootROM引导过程,涉及上电复位、引导引脚操作、BootROMHeader的作用、不同引导模式(主引导和JTAG从属),以及启动时的安全措施,包括PL初始化、加密和PL比特流配置。文章强调了BootROM在启动流程中的关键作用以及JTAG接口在调试中的便利性。

1399

1399

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?