电路语句(四):always_ff

前言

视频语法学习:B站链接

笔记原地址:https://github.com/Tan-YiFan/DigitalLogic-Autumn2020/tree/syntax/syntax网络不好,可能打不开。

一、always_ff

always_ff用于描述触发器。

//下面代码是D触发器

always_ff @(posedge clk,negedge resetn) begin

if (~resetn) begin

q <= '0;//非阻塞赋值,也可以称为并行赋值

end else if (en) begin

q <= d;

end

end

always_ff里可以描述很复杂的逻辑,但那样写不直观。写代码时,也应该参考理论课上讲的状态方程。

//将时序逻辑触发器和组合逻辑分开写

//用always_ff仅仅描述触发器的部分

logic [3:0] a, a_nxt;

always_ff @(posedge clk) begin

if (~resetn) begin

a <= '0;

end else if (en) begin

a <= a_nxt;

// {a, b} <= {a_nxt, b_nxt};

end

end

//always_comb描述的是行为,用阻塞赋值

always_comb begin

a_nxt = a;

// ...

unique case(a)

4'd3: begin

a_nxt = 4'd2;

end

default: begin

end

endcase

end

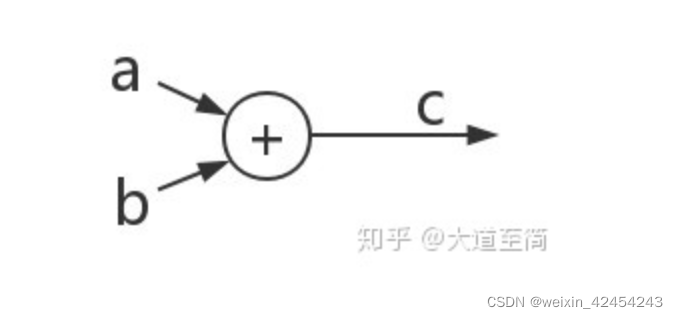

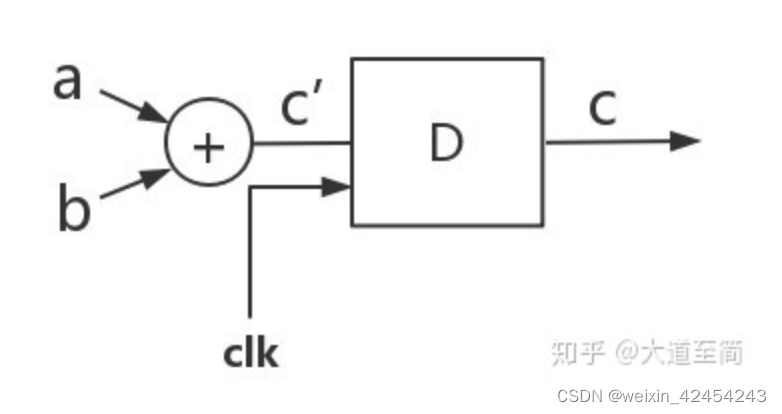

二、组合逻辑 & 时序逻辑

时序逻辑的区别在于,结果不会立即存到相应电路中,而是有一个 d 触发器。

时序逻辑的区别在于,结果不会立即存到相应电路中,而是有一个 d 触发器。

时序逻辑描述并列触发器,always_comb 描述电路行为。因此阻塞赋值放在 always_comb,而非阻塞赋值放在 always_ff。

本文详细解读了电路设计中的always_ff触发器概念,区分了always_ff与always_comb的使用,以及如何结合状态方程描述时序逻辑。通过实例展示了如何将触发器逻辑与组合逻辑行为分离,便于理解和编程实践。

本文详细解读了电路设计中的always_ff触发器概念,区分了always_ff与always_comb的使用,以及如何结合状态方程描述时序逻辑。通过实例展示了如何将触发器逻辑与组合逻辑行为分离,便于理解和编程实践。

1183

1183

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?