Latch up 闩锁效应原理介绍

Latch up 概念

Latch-up是指在集成电路中的一个异常现象,其中两个相反极性的晶体管(PNP和NPN)形成了一个正反馈回路,导致电路失去控制,出现异常电流流过。

Latch up 形成原理

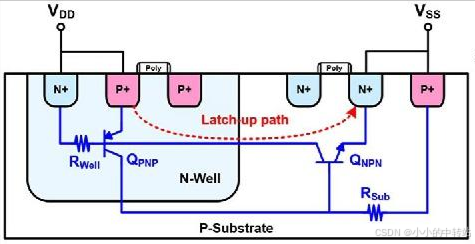

在集成电路中,晶体管之间存在PN结。当一个PNP晶体管的集电极连接到NPN晶体管的基极时,如果结反向偏置电压超过一定阈值,就会发生Latch-up现象,Fig1 所示。

正常工作情况下,三极管是截止的,不会发生Latch up。当受到外界来自电源,I/O,ESD静电泄放的干扰时,当一个PNP晶体管被激活时,它通过连接的NPN晶体管的基极转导电流,导致NPN晶体管也被激活,形成一个正反馈回,电流在这个结构里面不断放大,最终超过芯片承受范围,使得芯片被烧坏。

Fig1. CMOS latch up 原理图

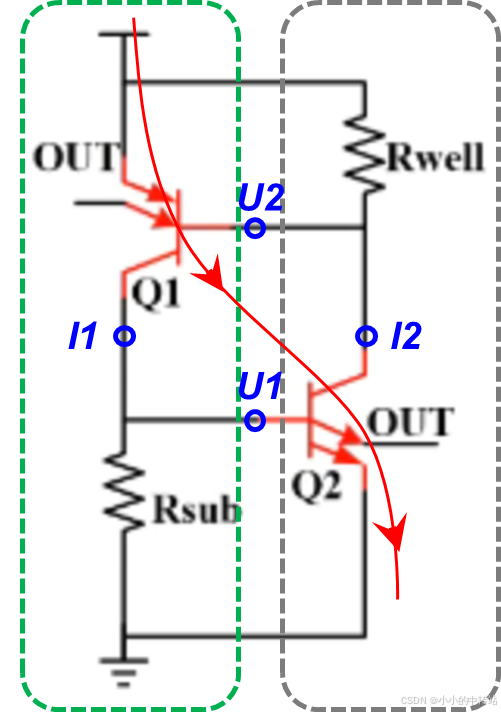

Fig2. 等效电路图(SCR-可控硅结构)

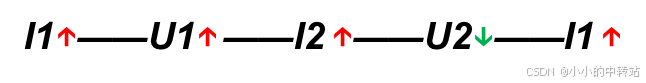

Fig2中电路结构左半部分(绿色框)相当于一个P管放大电路,右半部分(灰色框)相当于一个N管放大电路,且它们的输入输出首尾相连,形成一个正反馈环路。当受到干扰时,PNP管打开,PNP管输出端产生电流I1,I1流经NPN管放大成I2又输入到PNP管的基极,从而导致PNP管的输出端电流I1继续增加,I1增加又导致经NPN管放大后的I2增加,从而形成正反馈环路,电流不断增加。具体电流电压变化趋势如下:

Latch-up的结果是,电路中出现一个低电阻的路径(Fig2 红色线条所示),导致异常电流流过,这会导致电路失去控制,可能导致器件的损坏或电路功能的失效。

Latch up发生的条件

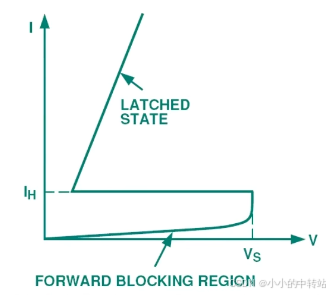

- 环路增益大于1(βnpn*βpnp)

- 两个BJT均导通.

- 电源提供的最大电流大于PNPN导通所需的维持电流IH.

Latch up触发原因

- VDD变化导致Nwell和Psub间寄生电容产生足够电流,进而触发Latch up.

- 当I/O信号变换超过VDD/GND范围,会有较大电流产生,也会触发Latch up.

- ESD静电泄放时,会从保护电路中引入载流子到阱和衬底中,也会触发Latch up.

- 负载过大,VDD或GND突变时也可能会触发Latch up.

- 阱侧面漏电流过大,也会触发.

Latch up预防

- 工艺制造时:采用重掺杂的衬底,降低Rsub,减小放大环路增益.

- 采用轻掺杂的外延层,阻止侧向漏电流从纵向PNP到低阻衬底的通路.

- STI隔离,将NMOS/PMOS分开.

- 使用绝缘隔离槽,SOI绝缘体上硅工艺可消除闩锁效应.

Layout设计

- 接触孔数量增加,接触孔尽量靠近active有源区,主要是为了降低Rwell,Rsub.

- 使用Guard ring,一方面降低Rwell,Rsub,一方面阻止载流子到达BJT基极.

- NMOS靠近GND,PMOS靠近VDD并保持足够距离,降低SCR触发的可能.

1028

1028

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?