目前主流的FPGA芯片仍是基于查找表。FPGA芯片主要由以下6部分组成:

(1)可编程输入输出单元(IOB)

(2)基本可编程逻辑单元(CLB)

(3)完整的时钟管理模块

(4)丰富的布线资源

(5)嵌入式块RAM

(6)内嵌的底层功能单元和嵌入式专用硬核

通过配置以上6个不同的部分,基本可以让FPGA实现任何你想要实现的功能。

一、FPGA的结构解析

对于一款芯片,我们肉眼看到的如图1.1所示,看不出它有任何特点。

当我们对其内部放大时,看到如图1.2所示结构,密密麻麻小方格,仍然完全看不出有什么特点:

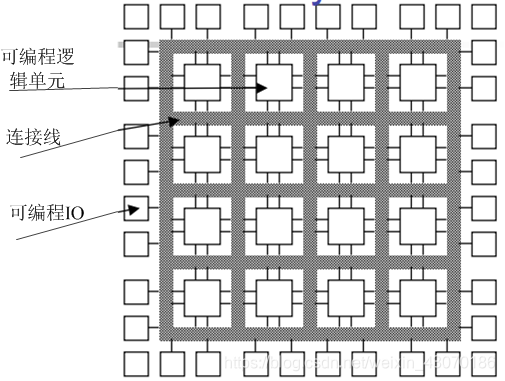

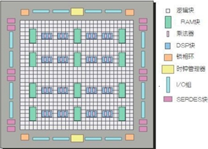

当我们再对其内部进行放大时,看到如图1.3所示结构,这时可以看到芯片内部的最基本组成单元:可编程逻辑单元、布线资源、可编程IO。对于复杂的芯片,内部还应包括时钟管理模块、嵌入式块RAM、内嵌的底层功能单元和嵌入式专用硬核,各基本单元在芯片内部的分布如图1.4所示。

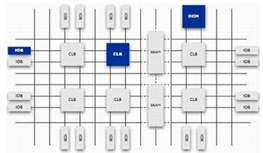

考虑到芯片内部的连接情况,对于图1.4所示的芯片内部结构,可以简化为图1.5所示内部结构相互连接的情况,不同部分通过丰富的布线资源相连接,最终实现我们想要的功能。接下来我们来讨论每个基本组成部分。

二、基本组成部分内部结构及功能

2.1、可编程输入输出单元(IOB)

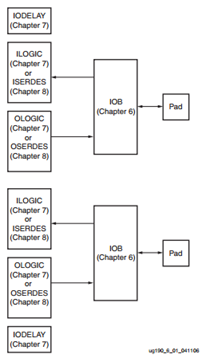

I/O模块包含两个IOB、两个ILOGIC、两个OLOGIC和两个IODELAY。图2.1所示为Virtex-5 I/O模块。

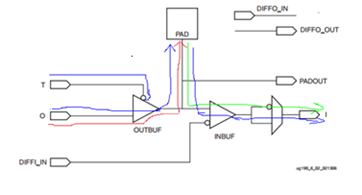

基本IOB图如图2.2所示,每个IOB包含输入、输出和三态SelectIO驱动器。差分I/O使用在一个模块中的两个IOB。图2.2中,红色线代表设置IO为output型时走线,绿色线代表设置IO为input型时走线,蓝色线代表设置IO为inout型时走线,T用来控制三态门,当其为0时,三态门导通,表示IO为输出类型,当为1时,三态门关闭,表示IO为输入类型。如inout data_o;

assign data_o = !T?data_o_2:'bZ;当T为0时,data_o被定义为输出类型;T为1时,data_o被定义为输入类型。

由图2.1可知,各IOB直接连接ILOGIC/OLOGIC对,该逻辑对包含输入和输出逻辑资源,可用于数据和IOB的三态控制。下面我们分别讨论ILOGIC和OLOGIC资源。

2.1.1 ILOGIC/OLOGIC资源

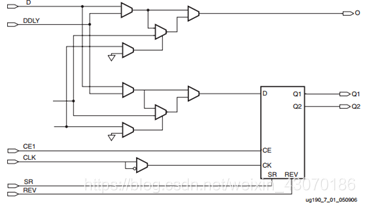

ILOGIC逻辑资源的模块图如图2.3所示:

ILOGIC资源可支

本文详细介绍了FPGA的基本组成结构,包括可编程输入输出单元(IOB)、基本可编程逻辑单元(CLB)、时钟管理模块、布线资源、嵌入式块RAM以及内嵌功能单元。通过对每个部分的深入剖析,阐述了FPGA如何通过配置这些部分实现各种功能。特别强调了IOB的内部结构和功能,如ILOGIC/OLOGIC资源,以及IDDR/ODDR和ISERDES/OSERDES在高速数据传输中的应用。

本文详细介绍了FPGA的基本组成结构,包括可编程输入输出单元(IOB)、基本可编程逻辑单元(CLB)、时钟管理模块、布线资源、嵌入式块RAM以及内嵌功能单元。通过对每个部分的深入剖析,阐述了FPGA如何通过配置这些部分实现各种功能。特别强调了IOB的内部结构和功能,如ILOGIC/OLOGIC资源,以及IDDR/ODDR和ISERDES/OSERDES在高速数据传输中的应用。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1063

1063

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?