`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2020/02/24 10:04:49

// Design Name:

// Module Name: funct

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module funct(

input rst,

input clk,

input [3:0]n,

output reg [31:0]result

);

function [31:0] factorial;

input [3:0]opa;

reg[3:0]i;

begin

factorial=opa?1:0;

for(i=2;i<=opa;i=i+1)

factorial=i*factorial;

end

endfunction

always@(posedge clk or negedge rst)begin

if(!rst)

result<=0;

else begin

result<=factorial(n);

end

end

endmodule

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2020/02/24 10:47:45

// Design Name:

// Module Name: funct_tp

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

`define clk_cycle 50

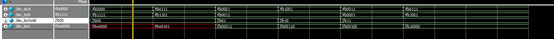

module funct_tp;

reg[3:0] n;

reg rst,clk;

wire[31:0] result;

initial

begin

n=0; rst=0; clk=0;

#50 rst=1;

for(n=0;n<=15;n=n+1)

#100 n=n;

end

always # `clk_cycle clk=~clk; //产生时钟信号

funct funct_try(.clk(clk),.n(n),.result(result),.rst(rst));

endmodule

1052

1052

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?