PDN全拼是Power Delivery Network / 电源分配网络

**一个项目在PCB走线过程中,需要对电源部分进行PDN仿真,软件会模拟将电源功率从电源输送给负载的实体路径,电流通过PDN从电源端流向负载端,再通过PDN,从负载端流回电源端,如果电源走太细或GND不够,PDN仿真将会显示出来结果。如果PDN仿真不通过,就匆匆发板,就会造成不开机、死机或电源烧毁的一些重大问题。**

PDN是什么?

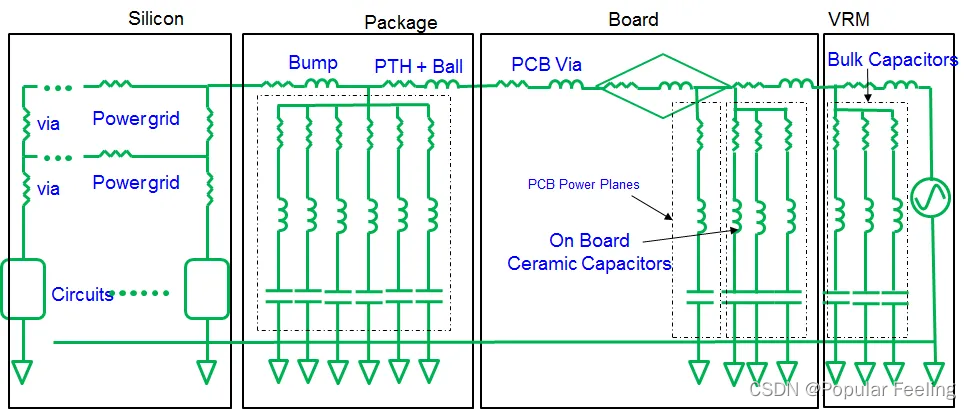

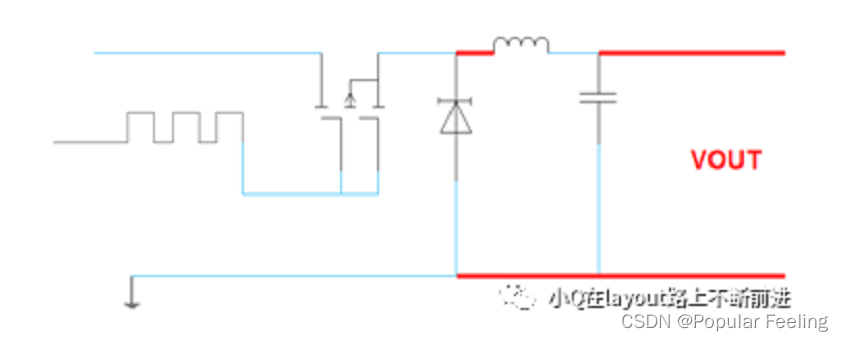

PDN实际是电源分配网络的简写,电源分配网络(PDN)就是将电源功率从电源输送给负载的实体路径。电流通过PDN从电源端流向负载端,再通过PDN,从负载端流回电源端。包含了电源调整模块(DCDC或LDO),靠近源端的大电容,去耦电容,最后到达主IC。而PDN的作用实际就是为负载提供稳定的电压,快速响应负载电流变化,减小开关噪声。

1、电源为什么不稳定?-电源噪声余量及其产生

一般的芯片要求的电源电压波动范围小于5%,但不同的芯片也会有不同的要求,具体可参考规格书,这里应指出的是这个电压应满足芯片在不同工作温度的要求。

电源噪声产生的原因:

(1).电源本身的噪声纹波。

(2).负载调整率。

(3).电源变化在电源路径上产生的压降。

2、PDN等效网络-理解PDN的等效电路及板级PDN涉及的频率范围

下面我们来看PDN的一个等效模型,如下,包含了VRM,PDN,以及SOC。

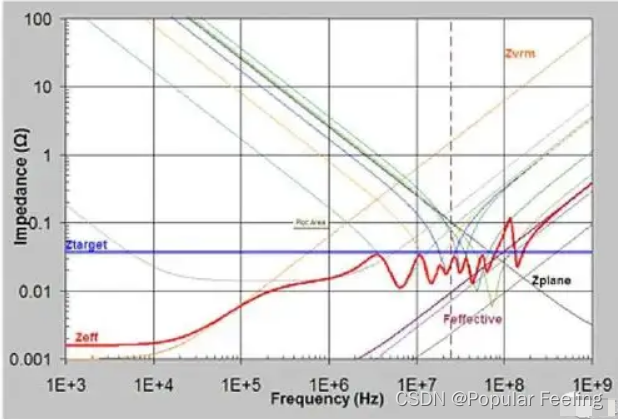

在我们进入对PDN关键路径的分析前,我们先来看一张PDN仿真报告的结果,如下:

纵坐标为阻抗,横坐标为频率。

通过PDN的物理意义,我们可以看出:

1. 该图要求频率从1KHz到1GHz之间,PDN阻抗要低于30mΩ以下。

2. 实际PDN曲线在100MHz附近,大约300MHz以上时,PDN阻抗超标。其他频率范围,PDN满足要求。

为什么要进行PDN阻抗分析?

高速和高频PCB设计人员通过阅读本文即可知道答案。但是,随着技术要求的不断提高,无论是否情愿,我们所有人都将成为高速和高频PCB设计人员,因此了解PDN阻抗如何影响PCB中信号的行为就变得非常重要。

简而言之,您的PDN阻抗会影响电路的以下几个方面:

·电源总线噪声。 由于PCB中的瞬态电流而产生的电压纹波。请注意,由于PDN阻抗是频率的函数,因此开关引起的电压纹波也将是频率的函数。请注意,无论调压器输出中的噪声水平如何,都会产生这些电压瞬变。

·电源总线噪声中的阻尼。 在某些情况下,电源总线上的任何纹波都可能显示为振铃(即,阻尼不足的瞬态振荡)。如果去耦电容器的尺寸不正确,或者在去耦网络中没有考虑到去耦电容器的自谐振频率,就会出现这个问题。

·所需的去耦水平。 过去,由于电容器自谐振频率(~100 MHz)相对较低,因此使用TTL和更快的逻辑系列并不足以确保PCB中实现去耦。因此,设计人员使用层间电容来提供足够的电容,以确保实现去耦。市场上已推出更新款的具有GHz自谐振频率的电容器,它们足以在高速/高频PCB中实现去耦。

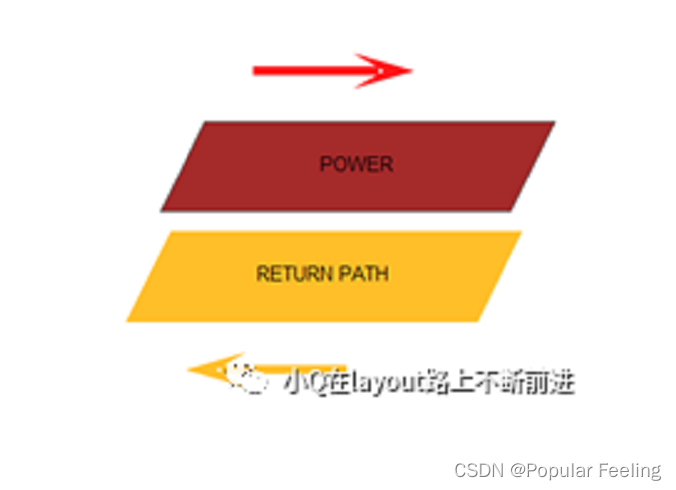

·回流路径。 您的回流电流将遵循最小电阻路径(针对直流电流)或最小电抗路径(针对交流电流)。接地网络中的阻抗会在空间中变化,并且部分取决于信号轨迹与PDN之间的寄生耦合。

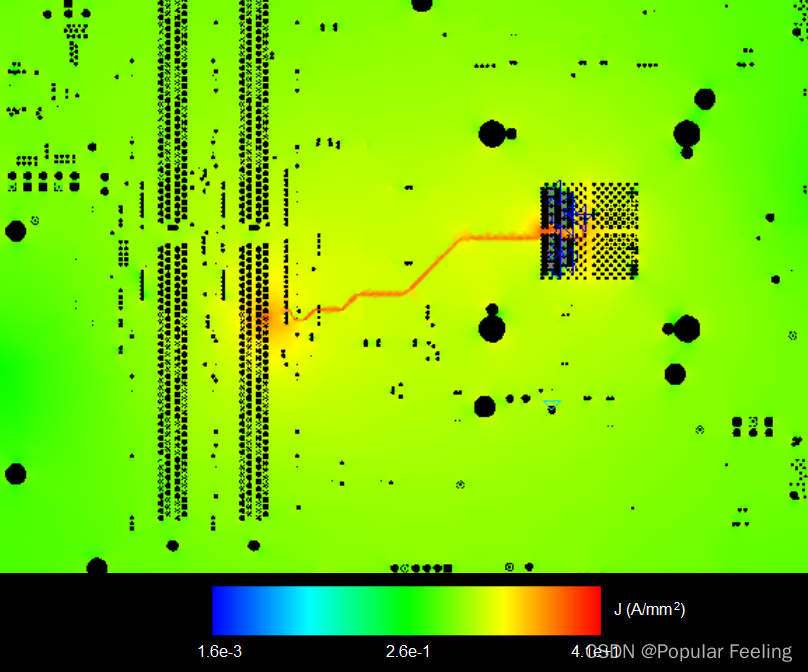

·电阻压降。 由于构成PDN的导体的固有电阻,供电和回流电流的直流电部分将会遭受一定的损耗。下图显示了PDN分析结果示例,说明了特定信号轨迹以下的回流电流和同一接地层中的直流电流。

·定时抖动。 由于信号的传播时间有限,因此从去耦电容器和调压器产生的电流将需要一些时间才能到达开关元件。当这些信号到达元件时,它们会干扰输出信号,从而有效地在信号的上升时间中产生一些抖动。通常,由于电源轨噪声引起的定时抖动会随着噪声强度以及调压器与元件之间的长度而增加。在长电源轨上,这可能会导致定时抖动达到几百纳秒,从而使数据去同步并提高误码率。

**注意此PDN分析仪输出中的信号轨迹**

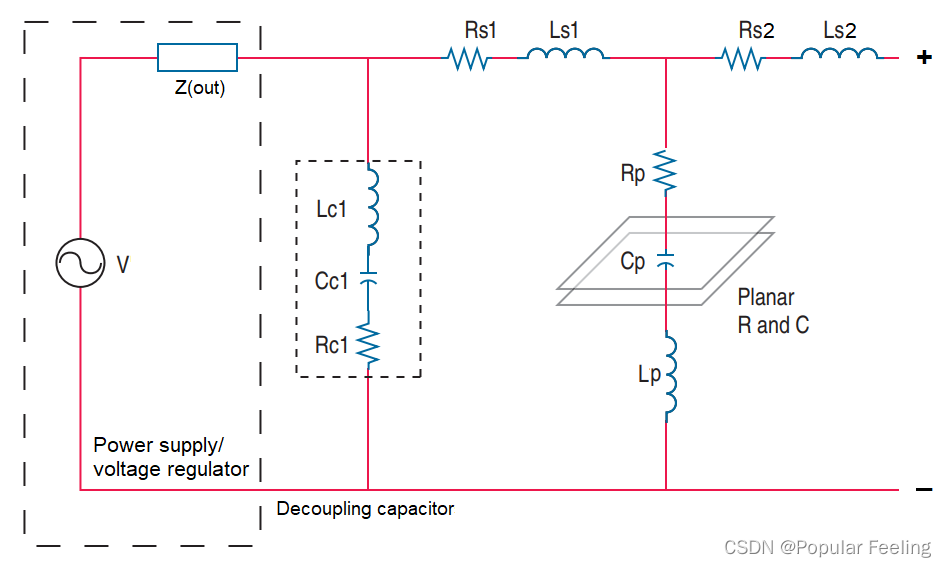

PDN阻抗分析的简化模型

可以直接从原理图为PDN的阻抗谱及其瞬态响应建模,但前提是必须考虑到PDN中的寄生效应。在下面的模型中,您会注意到若干电路元素,但是此模型仅包含两个实际元件。第一个是您的电源/调压器,它具有一定的指定输出阻抗Z(输出),并且通常属于RL串联。第二个是去耦电容器,其理想电容为Cc1。其余的电路元素属于寄生元素。Rs和Ls值分别用于固有导体电阻和寄生电源层电感的建模。Rp、Lp和Cp元件代表了电源和接地层之间的寄生耦合(即,层间电容)。

在分析此模型之前,需要确定或估计模型中各个元素的值。去耦电容器的值很容易处理;只需从数据表单中获取所需电容器的值即可。层间电容也很容易粗略估算;只需使用载板的介电常数、重叠的接地/电源层面积以及它们在叠层中的距离,即可得到层间电容Cp。剩余的R值可以使用预期的导线尺寸计算。L值需要根据电路各部分的近似回路电感来估算;这些值通常在pH到几个nH之间。

分析此模型的目标有两个:

1.根据频率确定右侧正负极端子之间的阻抗。这可以通过简单的频率扫描来完成。

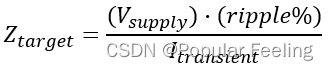

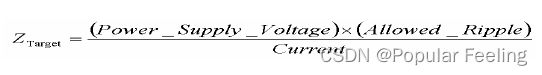

2.检查PDN阻抗是否小于目标阻抗。请注意,目标阻抗是使用开关IC将引入PDN的电流和允许的电压纹波来计算的:

3.通过添加一个与电源输出并联的电流源来检查瞬态行为(将正极端子置于Z(输出)之前)。设置电流源以提供具有下列公式所示总电荷Q的狄拉克δ函数脉冲,或提供阶跃电流。这将模拟传输到位于PDN右端的开关IC的瞬态电流。

4.检查最低频率PDN谐振(即阻抗谱中的峰值)是否大于开关IC的拐点频率。这是为了在尽可能宽的频带上尽量减小纹波。

(请注意,第3点旨在模拟由于下游开关IC引起的瞬态响应。如果您有10个将同时开关的IC,并且它们都向PDN引入相同的瞬态电流,那么您的脉冲幅度将要大10倍,并且您的目标阻抗将需要小10倍。检查完这三点后,您可以接着分析结果并确定可以采取哪些设计步骤来抑制PDN中的电源波动。)

电源完整性仿真

在目前的设计中,PDN仿真:主要看的是PMU→SOC的电源.

这里原厂给的仿真结果基本都是只看小系统的电源,并不是看整版的电源,所以,不要只看仿真结果PI,PASS就认为我这块板子上的电源都OK.

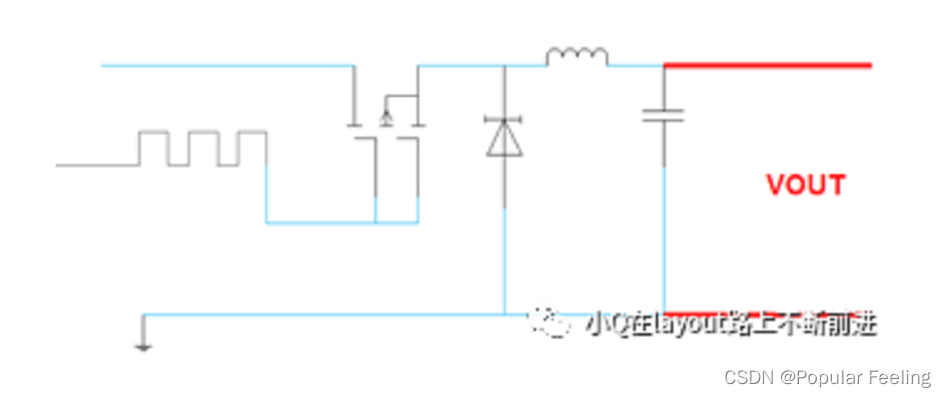

PMU通常包含有BUCK,LDO,BOB模块等.

PDN仿真的时候通常看的是BUCK回路,你看到的反馈结果最常见的应该都是只给一些out输出部分的一些仿真参数的结果而已,而有的平台设计还会给出关于IN输入部分的仿真参数的结果,以及反馈参数的要求是否满足等等.

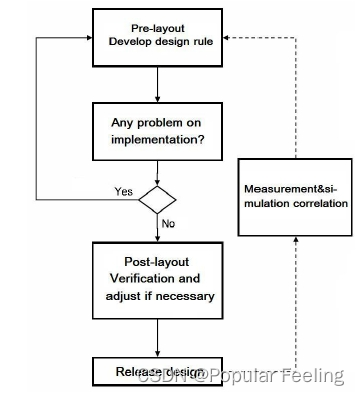

PDN 设计流程

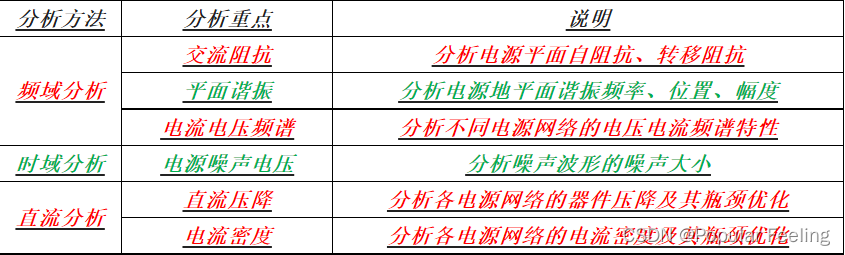

与信号完整性仿真设计流程类似,PI 设计流程也可以分为前仿真,后仿真,测量验证三个阶段。如下图所示:

前仿真的主要任务是:

1. 叠层设计;

2. 电源/地层铜厚选择;

3. 去耦电容数量、容值以及位置选择;

4. 过孔尺寸及出线方式选择;

5. VRM 感应线位置优化。

后仿真的主要任务是:

6. 去耦电容优化;

7. 定位过细的“颈线”;

8. 定位电流分布的热点。

(是通过实际的上板测量验证仿真的准确性。贯穿于PI 设计流程的PI 仿真分析的主要方法包括:直流压降分析、交流分析以及瞬态分析。)

1.直流压降分析

当电流通过有一定阻抗的导体时,会在导体两端产生一定的压差。由于这个压降完全是由导体直流电阻引起的,我们称这个压降为直流压降(IRDrop)。根据欧姆定律,直流压降由导体阻值和在导体上流动的电流所决定。随着芯片工艺的进步以及集成度的提高,芯片对电流的需求在不断增加,同时,芯片供电电压在不断降低,相同的直流压降在整个PDN 裕量中所占的比例越来越大,使得PDN 设计人员不得不考虑直流压降对PDN 性能造成的影响。直流压降分析的主要目标是:

1. 优化关键器件位置

2. 定位电流分布热点

3. 确定电源模块感应线位置

4.定位高阻抗区域及高温升区域

2.交流分析

大多数芯片对电源的要求以允许的最大波动为指标,PDN 看起来是一个时域问题,但是在时域中测量容易引入干扰,并且很难激励有源芯片的最大电流。除电源模块和最终负载,PDN 组成元件都是无源器件,相比于有源器件,在频域下有更好的稳定性。综合以上原因,使得在频域下进行PDN 的设计,在时域下进行PDN 的测量验证更加简单有效。

2.1目标阻抗及最大有效频率

我们可以通过如下公式确定PDN 的目标阻抗,各个参数都可以从芯片手册中得到,需要注意的是这里的电流指的是描述芯片工作所需最大电流与最小电流之间差值的动态电流。可以从芯片功耗计算出最大电流,通常,可以假定动态电流为最大电流的一半进行计算。

如果芯片厂商提供了芯片所需电流变化曲线,可以通过傅立叶变换将时域下电流转化为频域下电流变化曲线,代入上式,可以得到更准确的随频率变化的目标阻抗,这将使PDN 设计有更多裕量。

由于芯片封装和板上分布电感的存在,限制了板级PDN 的有效频率。在某个频率点之上,芯片片内电容将有效的降低PDN 阻抗。在极低目标阻抗PDN 设计中,板级PDN 的有效频率很难达到百兆赫兹,这时需要知道芯片片内电容开始起作用的准确频率。

2.2板上电容选择方法

板上电容种类,数量及位置的选择是PDN 设计的重要步骤。当前,主要有三种电容选择方法:频域目标阻抗法、大“V”法以及十倍法。频域目标阻抗法通过选择一系列不同容值电容得到多个谐振点,多个谐振点之间保持较近的距离从而得到一条相对平滑的阻抗曲线。大“V”法在整个频带上只选择一种电容,通过增加此电容的数量降低谐振点位置以及阻抗曲线的感性部分,增加容性部分以达到目标阻抗的要求。十倍法是指选择容值相差10 倍的一组电容均匀的分布于整个频带上,在没有精确仿真工具的帮助时,这种方法可以有效而快速的完成电容的选择。

2.3抑制反谐振

PDN 中的任意两个不同部件都会产生反谐振,发生反谐振时所产生的谐振峰值极大的拉高了PDN 的阻抗,影响PDN 的性能。如上节所述三种电容选择方法,如果不考虑电容与电源模块及芯片封装间谐振,三种方法都可以满足设计要求,但是考虑电容与PDN 中其它组成部分间的谐振,不一定每种方法都可以满足要求。抑制反谐振是PDN 设计中的重要内容,通常,减少电源/地平面间介质厚度可以有效的抑制PCB 模态谐振。

方法二. 借助于仿真工具进行分析

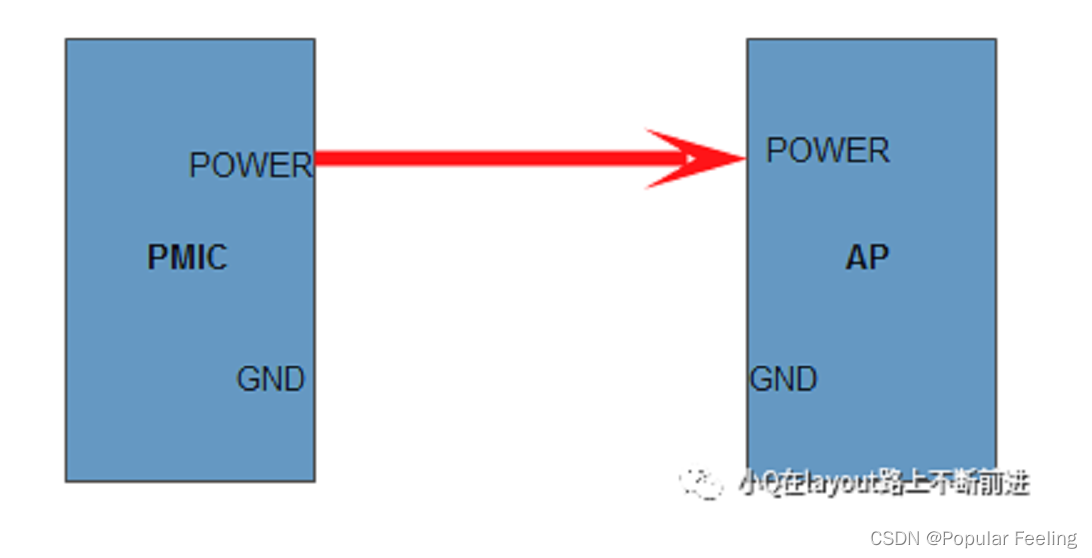

(1)返回路径的考虑

要借助于仿真工具的分析,我们不仅需要知道仿真工具有哪些可以实现我们的目的,以及如何实现,更重要的是,我们需要知道该怎么去分析这个参数的原理,这部分内容针对于仿真工具的部分先放到后面再说,主要还是以分析RDC的原理为重点.

由前面提到的内容,我们知道,分析RDC,无非就是分析直流电阻,方法一的分析方式说了只是估算,是的,它分析的并不全面,只考虑了一种比较理想状态的数据,完全几何形状的,再回过头来看看我们的PCB的大电源的走线,规矩点的还用走线来,可那些铺铜箔的呢,难道还一块块分割来进行分析吗,明显不可能.

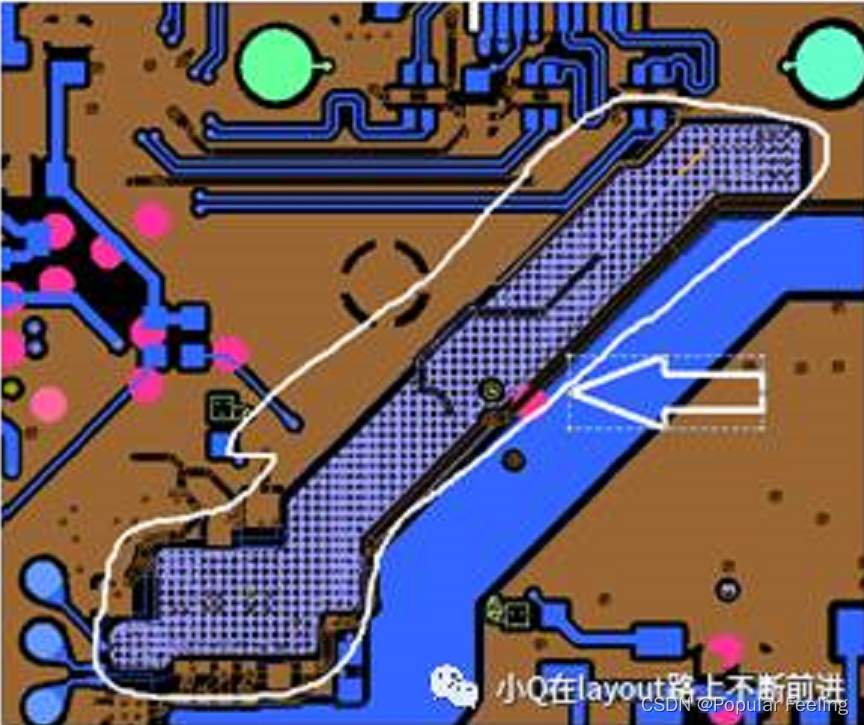

那么提到了直流电阻,如果没有实际去分析,相信很多人在设计的时候只关心了如下图部分,只关心了电源宽度是否满足设计要求,但这样的考虑是不完全的.

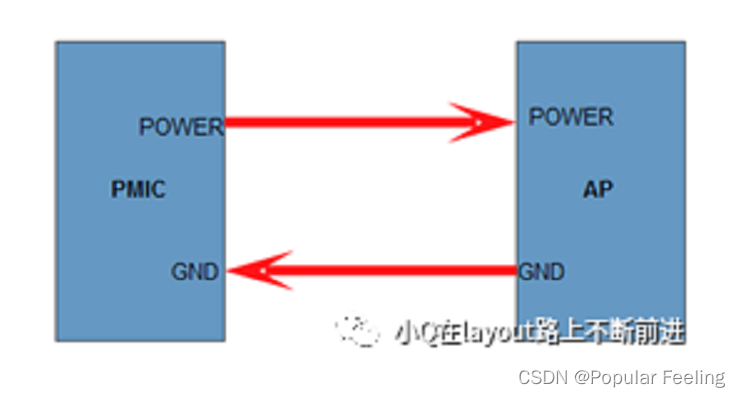

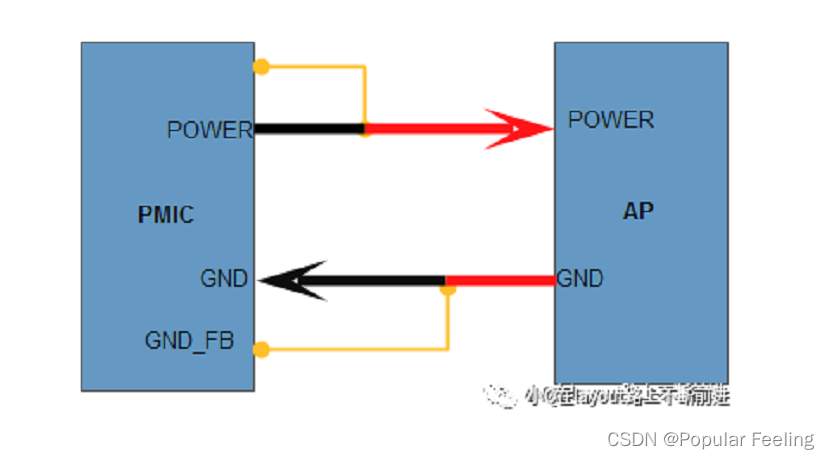

考虑比较完全的应该如下图所示:

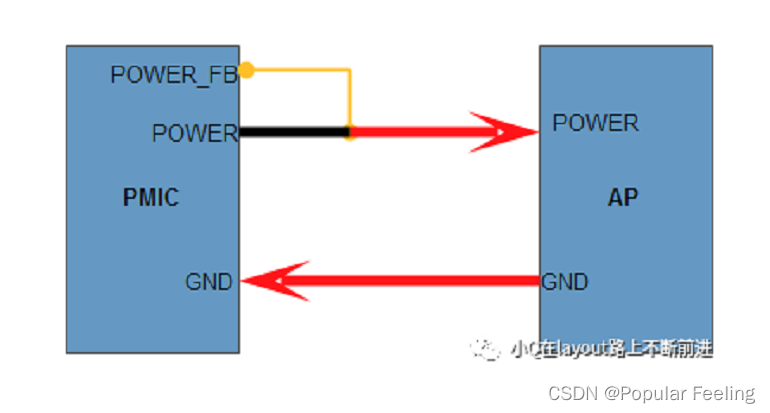

同理,在分析PMU输出的时候,还有个FB的问题,这里会涉及到远端反馈跟近端反馈的问题.

个人见解:

至于远端反馈近端反馈的问题,当然能够更好的反应用电端的电压变化是最好的,可是如果近端反馈已经足够的话,也没必要一定要绕远道去取远端的用电端的数据

(2)三种不同设计下的RDC分析

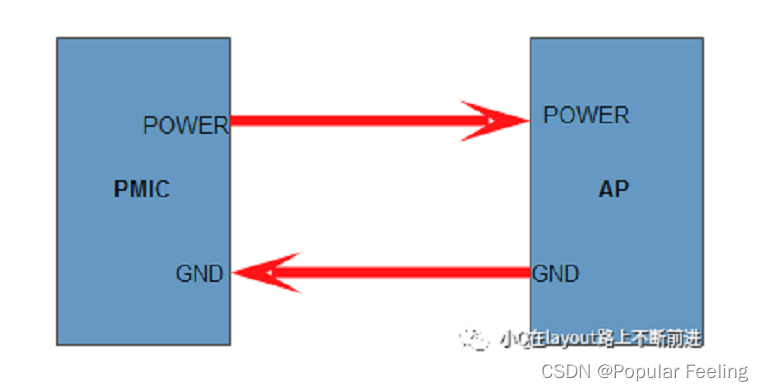

情况1.无反馈型(LDO输出型)

情况2.电源反馈型

情况3.差分反馈型

对应的RDC=RPOWER_RED+RGND_RED

备注:

公式表示将红色路径的阻抗都考虑入内,叠加,换句话说,RDC的值等于电源路径的阻抗+地路径的阻抗,这里_RED的意思是只考虑红色标注的路径部分.

(3) 不同平台设计的差异性

看了(2)的设计,也许你会说”原来如此啊!”.

可是,如果,你就这么直接的应用到每个平台设计上的时候(假设你已经会使用某个仿真工具了),你会发现时而与原厂提供的数据挺接近的,时而又好像有所差异,问题在哪里呢?

RE. 这是因为每家分析的角度都有所差异,初期可以先将上述的分析套入,从而进一步分析他们的分析路径,当然,如果你已经明白了这些原理,可以直接写邮件向原厂咨询(人家愿不愿意搭理你是另外一回事了)以进一步确认分析是否可行.

在实际项目分析的时候,遇到的问题可能会更多.

(4) 推荐分析方式

推荐采用情况1的分析方式,考虑比较完整.也比较通用.一般来说,如果只考虑BUCK输出的时候,正常分析下面红色路径即可

但是实际中,推荐如下考虑,从PMU的引脚输出到电感引脚端的一小段的走线也列入其中.

(5) Layout中的注意事项

根据上面唠叨的一大堆内容,想要RDC阻抗尽可能的低,那么电源路径很重要,其相邻的参考平面也是很关键的,在layout设计中,尽可能不要跨分割电源平面.

Q. Z阻抗是什么,怎么分析?

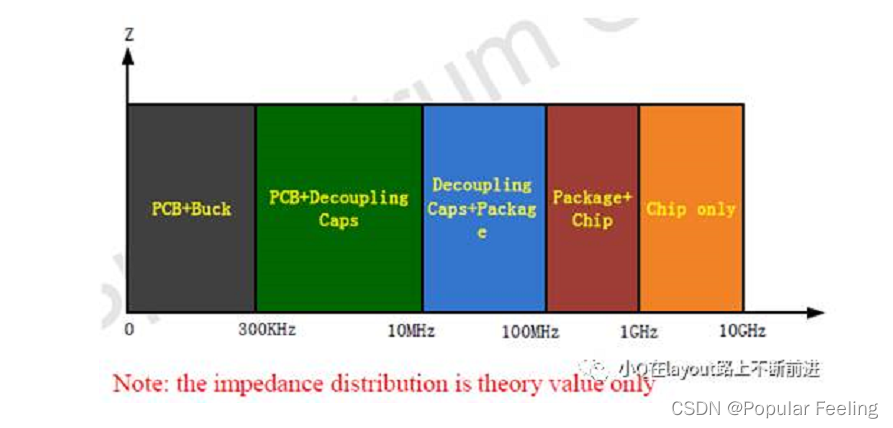

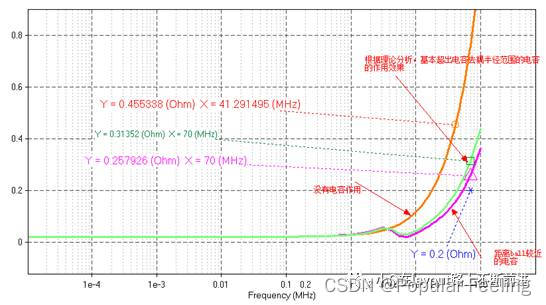

要讲Z阻抗之前,先来回顾一下最开始给出的一个频段的图,如下

可能我们比较经常听到的看到的是S参数,相对于Z参数而言,可能就较为陌生了。这里需要明白的是S参数主要针对于信号线而言,而Z参数则主要针对于电源/GND而言。

通常直流电源,并不是真正的直流,而是参杂着很多高次谐波,即电源纹波,不同频率的电源纹波对电源平面本身有哪些影响呢?我们通过Z参数模型曲线来理解。

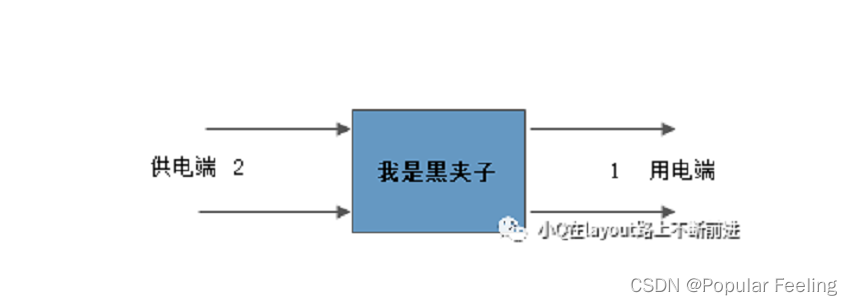

把电源供电网络(PDN)看成一个二端口网络,Z11和Z22就是自阻抗,如果端口2是VRM输出管脚,端口1为器件的电源管脚,则Z11表征了该器件工作时的输入阻抗特性,即从器件向PDN系统内部看进去的阻抗。通常要分析该指标是否满足目标阻抗的要求,如果波形中有谐振,则必须抑制它. Z12和Z21通常被称为转移阻抗或者是传输阻抗。转移阻抗反映了不同电源管脚或者芯片之间的噪声干扰。通常用于研究电源网络之间的干扰及去耦电容的放置。

在PDN设计中,我们最关心的是Z11的设计是否满足了低于目标阻抗值的问题。

Z11的在PCB的设计上主要体现在PCB走线以及去耦电容的设计问题上。

关于去耦电容的设计,可以根据理论分析其去耦半径,从而可以进一步大致评估电容的摆放位置是否起到了作用,关于去耦电容位置的摆放也可以进一步通过软件进行分析,得到比较直观的结果。

在高频的时候还需要特别注意电容已经不再是单纯的电容的问题,有着ESR以及ESL参数,以及安装电感,等都会对电源系统的设计带来叠加效应。

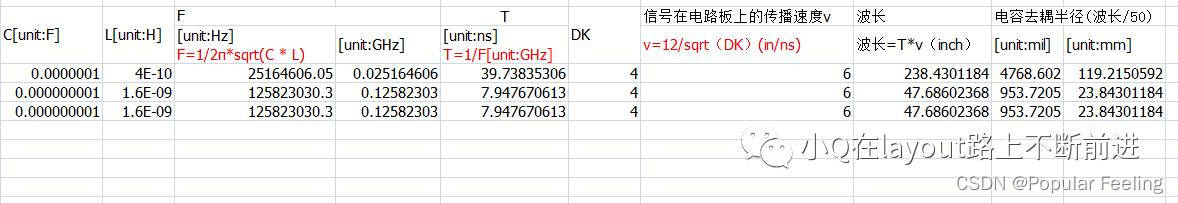

Q. 一个电容的作用范围可否预估?

我研究了一下,觉得这是挺有意思的发现,可以把相关的公式输入到Excel,对应着相应的的容值以及ESL进行换算可得到一个去耦半径的参数,也就一个电容对应的理论应有的作用范围.

以1uf作用范围为例,假如PCB板厚为7mm,则可得1uf电容放置在bottom面的作用范围约只剩下2mm,也即78mil左右,以电容焊盘为中心画圆(球形考虑),可以大致评估电容可作用到的范围。

案例分析:对比电容放置在去耦半径之外对结果的影响(电容1uf)

一个单纯的电容有着他自身的谐振频率;

一个电容安装到PCB上,存在着安装电感,从而导致自谐振频率的偏移。

在后面的文章中也将进一步谈如何逆推去耦电容的回路电感,也可以通过仿真计算去耦电容的回路电感。

Q. Rremote是什么?

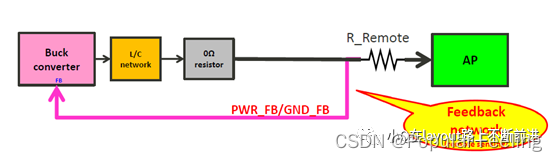

听过Rdc参数,听过Z参数,但可能就不是所有人都听过Rremote参数了.但你一定注意过PCB设计中的电源的反馈线,也是我们之前谈到过的可能是单根的反馈线,也可能是差分反馈线.那么关于这反馈线的设计要满足怎样的要求呢?答案是要满足Rremote的参数设计要求.

先来看看下面一张图:

我想从上图来看,我们能够比较清晰的理解这个R_remote的概念,在我们设计中通常会通过一个短接点接到芯片ball,为了尽可能减小R_remote参数值,直接的方式则是尽可能将短接点尽可能的靠近CPU的ball,这里要注意层叠的影响,放在L5与放在L8的短接点对结果的影响是很大的,关于层叠方面的知识可以进一步深入说明。

再来看看Rremote的计算方式:

PDN仿真经验总结:

1.Bypass电容尽量放电源Pin的背面,这样距离短,不容易被旁路,回路也短;

2.孔径越大越容易过PDN仿真。

3.

971

971

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?