前言

本文为我自己的学习笔记,属于Cadence Virtuoso系列的进阶部分,采用的软件版本是Cadence Virtuoso IC617。其他文章请点击上方,看我制作的Cadence Virtuoso专栏内容。

本文主要记录了如何用Cadence Virtuoso IC617和工艺参数设计有源负载差动对(俗称五管OTA)。这将帮助学习者理解工艺参数在运放设计中的作用,以及为后续引入 gm/Id 设计方法做好铺垫。

原理

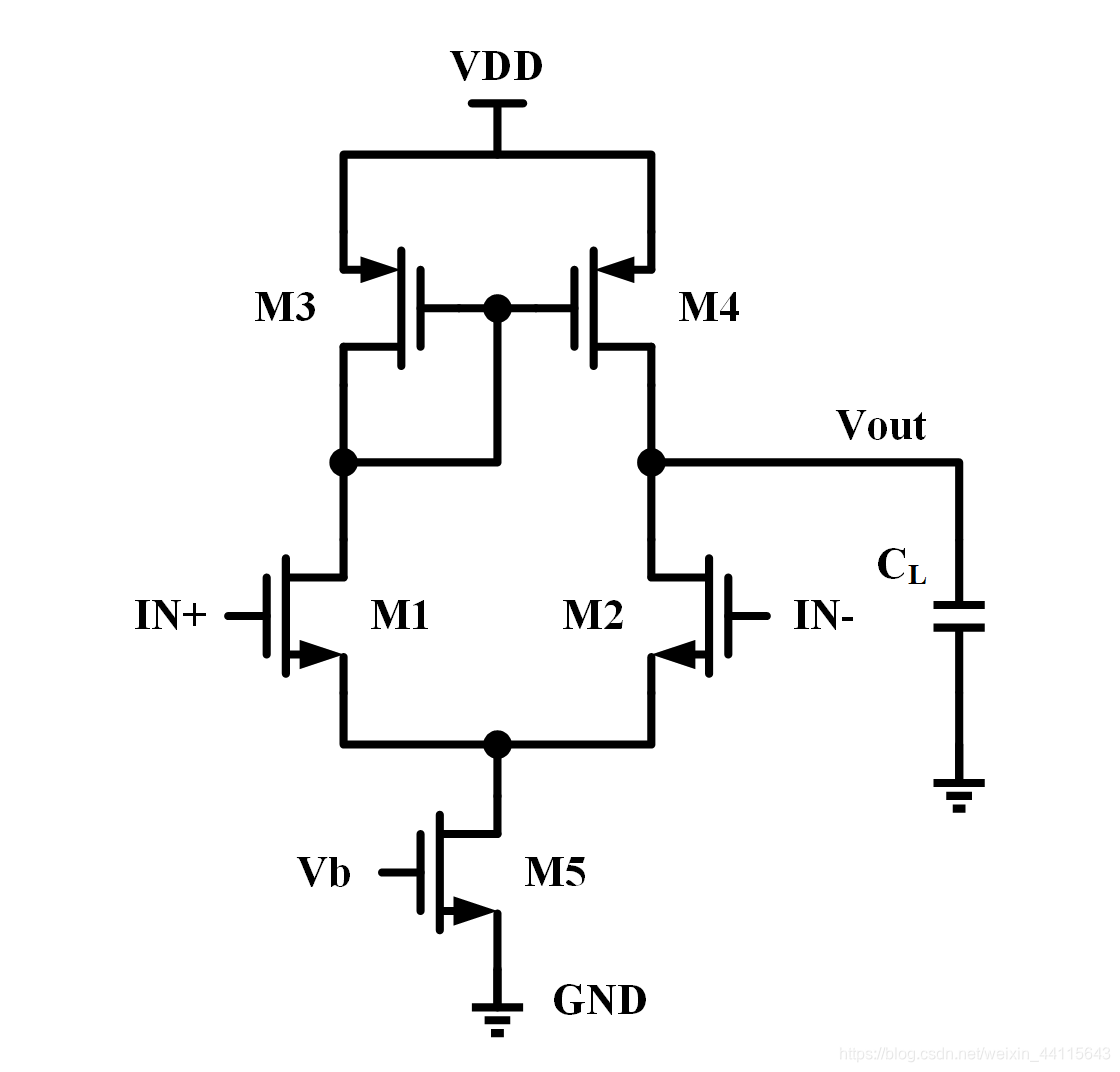

电路拓扑

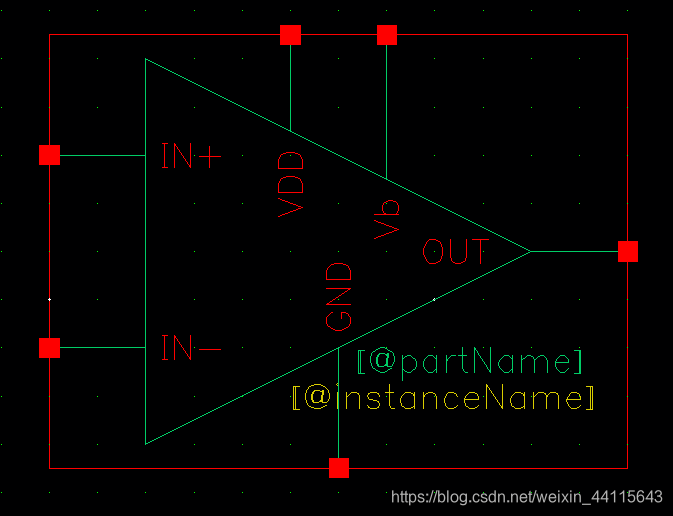

五管OTA的主拓扑由五只晶体管组成。注意,这里不考虑深n阱工艺等特殊工艺,所以,所有的N-MOS的B端接到GND,所有的P-MOS的B端接到VDD。

两只输入管 M1 和 M2 为N-MOS,互相对称,构成差分输入结构,其跨导gm和增益相关。

M3 和 M4 两只P-MOS构成有源电流镜,互相对称,其中 M4 的 D 端接输出,而 M3 的 D 端和 G 端相连,这就构成了单端输出结构。

最后的 M5 决定了尾电流,其需要另外接一个电流基准。

在输出端还需要接上 pF 级别的负载电容。

参数指标

以一个例题举例,题目要求如下:

计算公式

转换速率SR

S R = I 5 C L ( I 5 = I S S ) SR={I_5 \over C_L}\quad (I_5=I_{SS}) SR=CLI5(I5=ISS)

功耗P

P = V D D ∗ I 5 P=V_{DD}*I_5 P=VDD∗I5

输出电阻Rout

R o u t = 2 ( λ n + λ p ) I 5 R_{out}={2 \over (\lambda _n +\lambda _p)I_5 } Rout=(λn+λp)I52

截至频率f-3dB

f − 3 d B = 1 2 π R o u t C L f_{-3dB}={1 \over 2\pi R_{out} C_L} f−3dB=2πRoutCL1

增益Av

A v = g m 1 , 2 R o u t Av=g_{m1,2}R_{out} Av=gm1,2Rout

共模输入上限V-ICMR-MAX

V I C M R − M A X = V D D − V S G 3 , 4 + V T N V_{ICMR-MAX}=V_{DD}-V_{SG3,4}+V_{TN} \\\quad\\ VICMR−MAX=VDD−VSG3,4+VTN

共模输入下限V-ICMR-MIN

V I C M R − M I N = V D 5 , s a t + V G S 1 , 2 V_{ICMR-MIN}=V_{D5,sat}+V_{GS1,2} VICMR−MIN=VD5,sat+VGS1,2

计算步骤

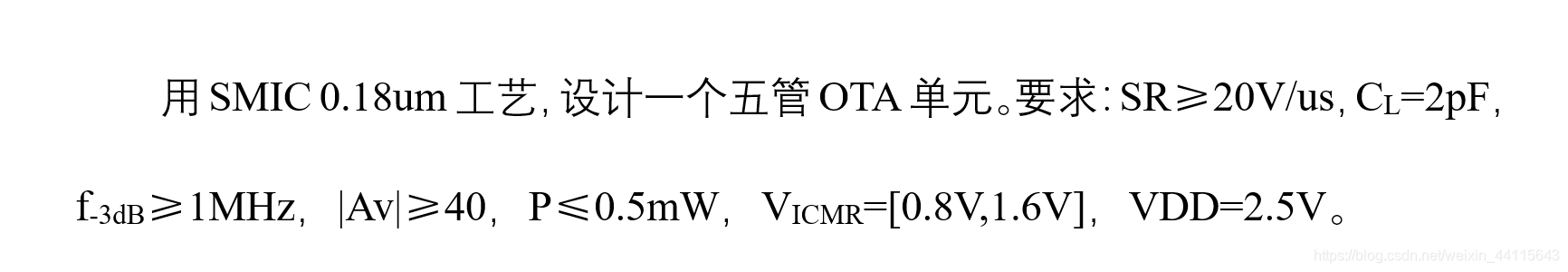

工艺参数

在之前的文章中,已经把工艺参数仿真出来了,可以点击以下链接查看仿真方法。

用Cadence Virtuoso IC617仿真工艺库参数

仿真出来的参数如下。

其中Kx代表衬底的参数。

K x = μ x C o x \quad\quad K_x=\mu_xC_{ox} Kx=μxCox

确定Iss取值

首先确定尾电流 ISS 的取值,即 I5 ,才能确定各个晶体管的尺寸。

转换速率的约束

S R = I 5 C L ⩾ 20 V / μ s ⇓ I 5 ⩾ 40 μ A SR={I_5 \over C_L} \geqslant 20V/\mu s \\\dArr\\ I_5\geqslant 40\mu A SR=CLI5⩾20V/μs⇓I5⩾40μA

截止频率的约束

f − 3 d B = 1 2 π R o u t C L = ( λ n + λ p ) I 5 4 π C L ⩾ 1 0 6 ⇓ I 5 ⩾ 113 μ A f_{-3dB}={1 \over 2\pi R_{out} C_L} ={(\lambda _n +\lambda _p)I_5 \over 4\pi C_L} \geqslant 10^6 \\\dArr\\ I_5\geqslant 113\mu A f−3dB=2πRoutCL1=4πCL(λn+λp)I5⩾106⇓I5⩾113μA

功耗的约束

P = V D D ∗ I 5 ⩽ 0.5 m W ⇓ I 5 ⩽ 200 μ A P=V_{DD}*I_5 \leqslant 0.5mW \\\dArr\\ I_5 \leqslant 200\mu A P=VDD∗I5⩽0.5mW⇓I5⩽200μA

最终取值

综合以上计算,得出 I5 的取值范围如下。

113

μ

A

⩽

I

5

⩽

200

μ

A

113\mu A \leqslant I_5 \leqslant 200\mu A

113μA⩽I5⩽200μA

由于左边范围由转换速率和截止频率约束,右边范围由功耗约束,为了更好接近指标,取值可以稍微靠右,选取以下数值。

I 5 = 180 μ A I_5 = 180\enspace \mu A I5=180μA

确定M1和M2尺寸

以下关系式成立,可以代入Av的计算公式中。

g

m

1

,

2

=

2

K

n

(

W

L

)

n

1

,

2

I

1

,

2

I

1

,

2

=

1

2

I

5

g_{m1,2}=\sqrt{ 2K_n \Big ({W \over L} \Big)_{n1,2} I_{1,2}} \quad\quad I_{1,2}={1 \over 2}I_5

gm1,2=2Kn(LW)n1,2I1,2I1,2=21I5

可以得到以下结果。

( W L ) n 1 , 2 = A v 2 ( λ n + λ p ) 2 I 5 4 K n ≈ 25.25 \Big ({W \over L} \Big)_{n1,2}= {A_v^2 {(\lambda _n +\lambda _p)}^2 I_5 \over 4 K_n }\approx25.25 (LW)n1,2=4KnAv2(λn+λp)2I5≈25.25

确定M3和M4尺寸

以下关系式成立。

V

S

G

3

,

4

=

2

I

3

,

4

K

p

(

W

L

)

p

3

,

4

+

∣

V

T

P

∣

I

3

,

4

=

1

2

I

5

V_{SG3,4}=\sqrt{ {2I_{3,4} \over K_p( {W\over L} )_{p3,4}} }+\lvert V_{TP} \rvert \quad\quad I_{3,4}={1 \over 2}I_5

VSG3,4=Kp(LW)p3,42I3,4+∣VTP∣I3,4=21I5

同时对公式移项。

V

I

C

M

R

−

M

A

X

=

V

D

D

−

V

S

G

3

,

4

+

V

T

N

⇓

V

S

G

3

,

4

=

V

D

D

+

V

T

N

−

V

I

C

M

R

−

M

A

X

=

1.16

V

V_{ICMR-MAX}=V_{DD}-V_{SG3,4}+V_{TN} \\\dArr\\ V_{SG3,4}=V_{DD}+V_{TN}-V_{ICMR-MAX}=1.16\enspace V

VICMR−MAX=VDD−VSG3,4+VTN⇓VSG3,4=VDD+VTN−VICMR−MAX=1.16V

最后得出。

( W L ) p 3 , 4 ≈ 3.5 \Big ({W \over L} \Big)_{p3,4} \approx3.5 (LW)p3,4≈3.5

确定M5尺寸

以下关系式成立。

V

G

S

1

,

2

=

2

I

1

,

2

K

n

(

W

L

)

n

1

,

2

+

V

T

N

I

3

,

4

=

1

2

I

5

V

O

V

5

=

V

G

S

5

−

V

T

N

=

2

I

5

K

n

(

W

L

)

n

5

V_{GS1,2}=\sqrt{ {2I_{1,2} \over K_n( {W\over L} )_{n1,2}} }+V_{TN} \quad\quad I_{3,4}={1 \over 2}I_5 \\\quad\\ V_{OV5}=V_{GS5}-V_{TN}= \sqrt{ {2I_5 \over K_n( {W\over L} )_{n5}} }

VGS1,2=Kn(LW)n1,22I1,2+VTNI3,4=21I5VOV5=VGS5−VTN=Kn(LW)n52I5

代入进以下公式。

V

I

C

M

R

−

M

I

N

=

V

O

V

5

+

V

G

S

1

,

2

=

0.8

V

V_{ICMR-MIN}=V_{OV5}+V_{GS1,2}=0.8\enspace V

VICMR−MIN=VOV5+VGS1,2=0.8V

最后得出。

(

W

L

)

n

5

≈

25.7

\Big ({W \over L} \Big)_{n5} \approx25.7

(LW)n5≈25.7

同时得出 VGS5 ,也就是尾电流晶体管的直流偏置电压。

V G S 5 = V b = 0.575 V V_{GS5}=V_b=0.575\enspace V VGS5=Vb=0.575V

结果仿真

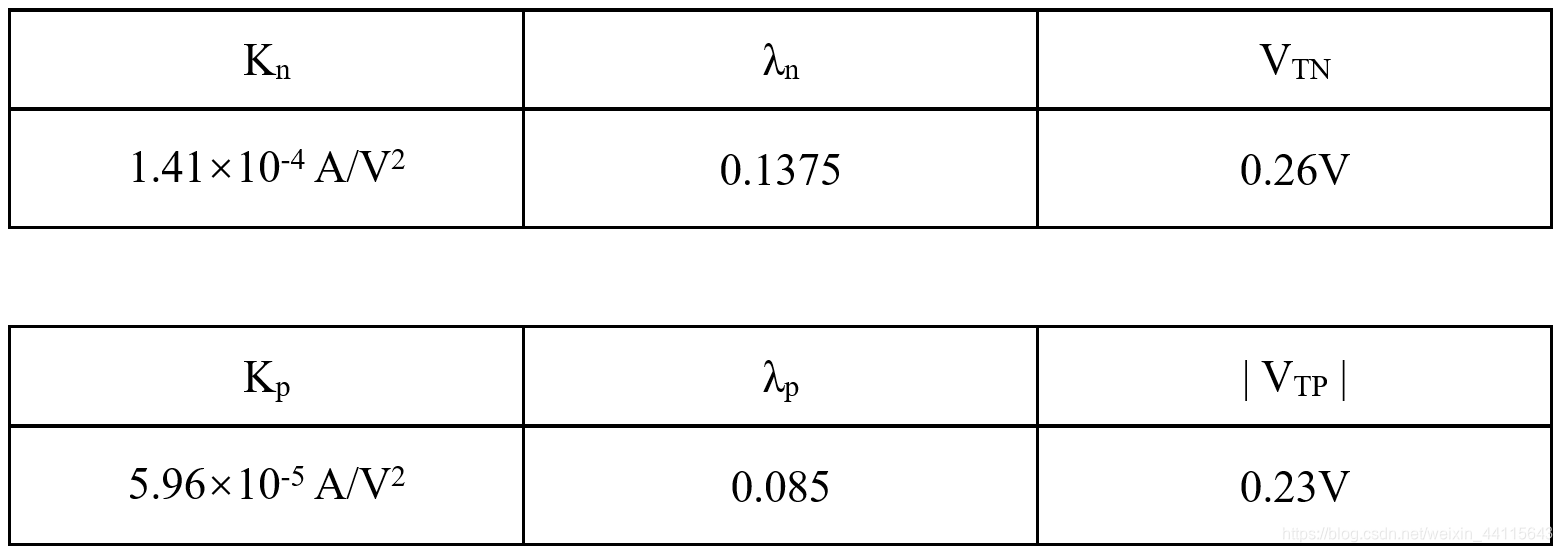

参数汇总

根据以上结果,汇总成下表。

| 1,2 | 3,4 | 5 | |

|---|---|---|---|

| W/L | 25.25 | 3.5 | 25.7 |

选取最小栅长180nm的两倍作为晶体管栅长,定以下尺寸。晶体管栅长的最小步进是10nm,也就是说,只能是180nm,190nm这样取值,而不能取185nm,会导致W/L的实际取值和计算稍微有点偏差。

| 1,2 | 3,4 | 5 | |

|---|---|---|---|

| W | 9.1u | 1.26u | 9.3u |

| L | 360n | 360n | 360n |

| W/L | 25.28 | 3.5 | 25.8 |

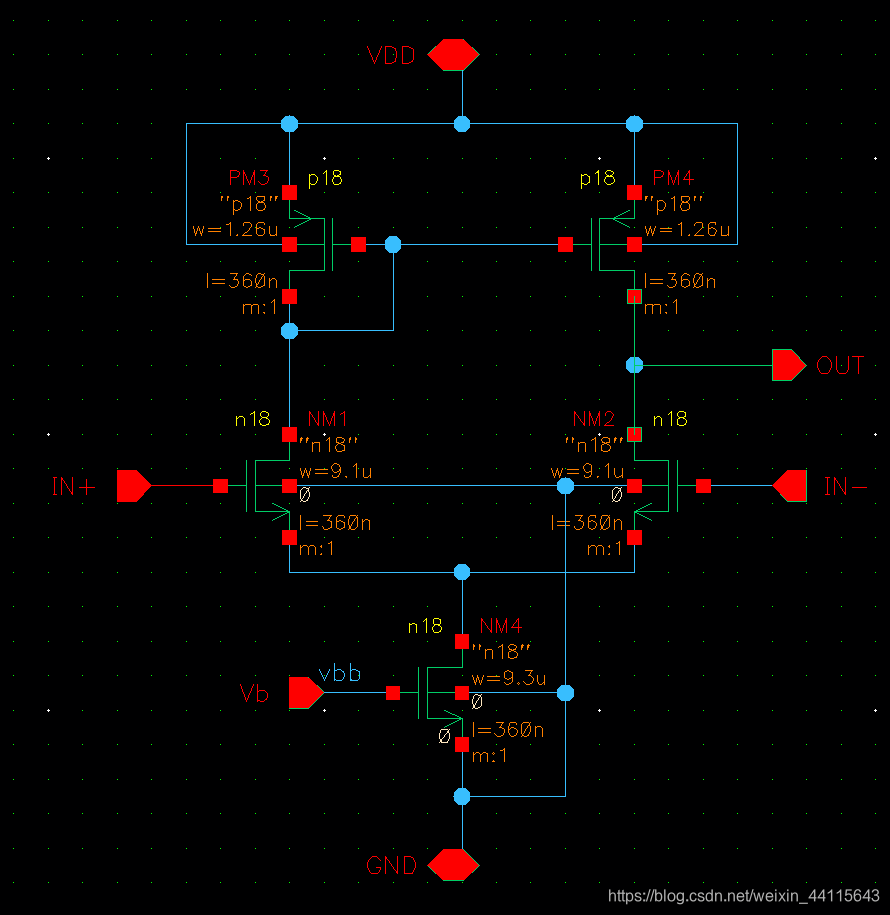

绘制器件

在Cadence Virtuoso IC617里绘制器件内部的原理图。同时,设置Pin脚,即将其作为一个完整的模块进行仿真。电源接口设置为“inputOutput”双向接口,其他的就设置为“input”或“output”。注意,pin的名字不要和其他的网络标号同名,在部分工艺库中是不区分大小写的,所以字母一样但大小写不一样也不行,保存的时候会报Error。

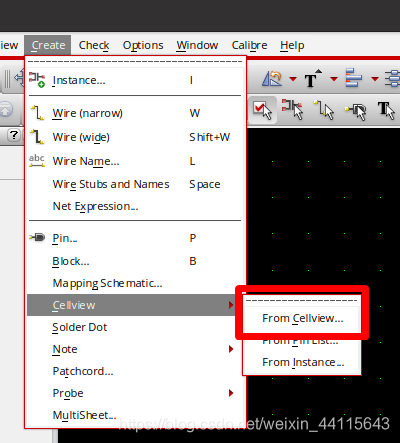

生成器件

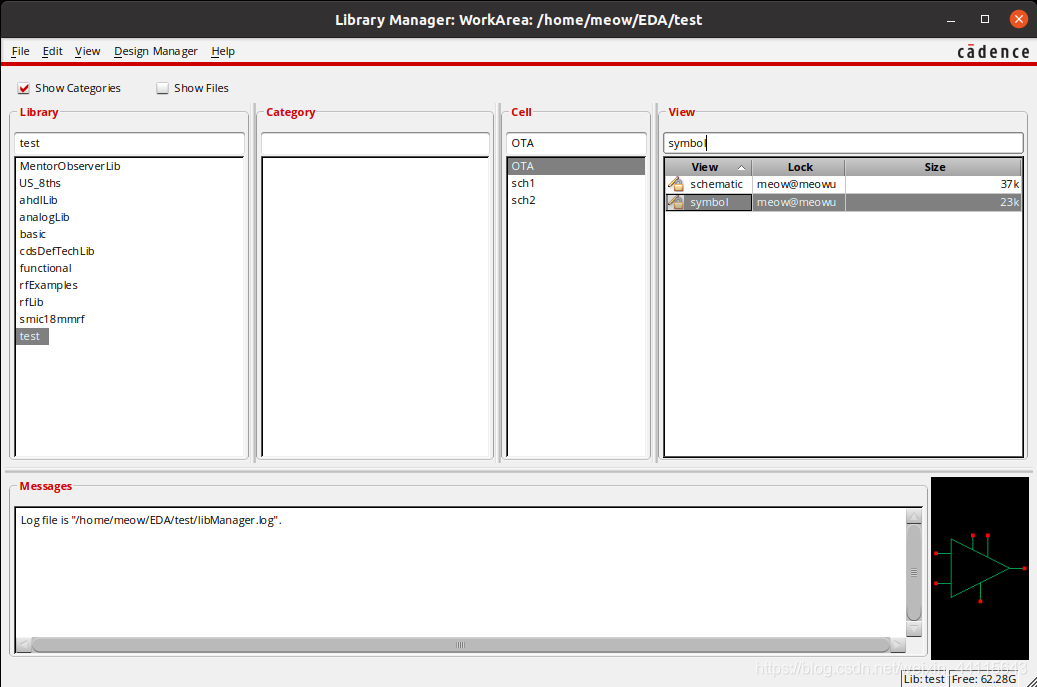

设计好子模块后,生成单独的器件。

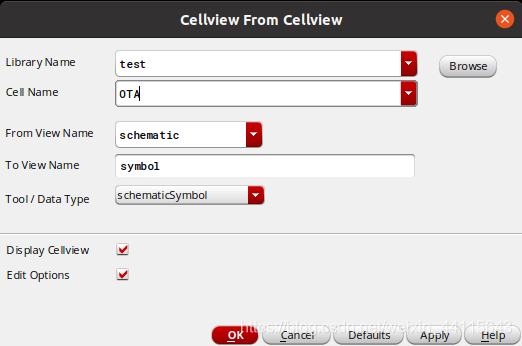

名字选择默认的即可,默认的为当前原理图的名字。

这里设置的是Pin脚的朝向,按照一般的习惯设置即可。

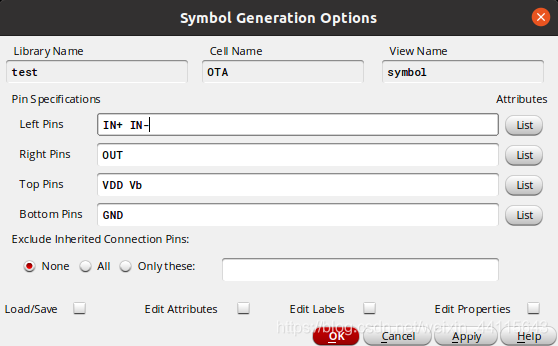

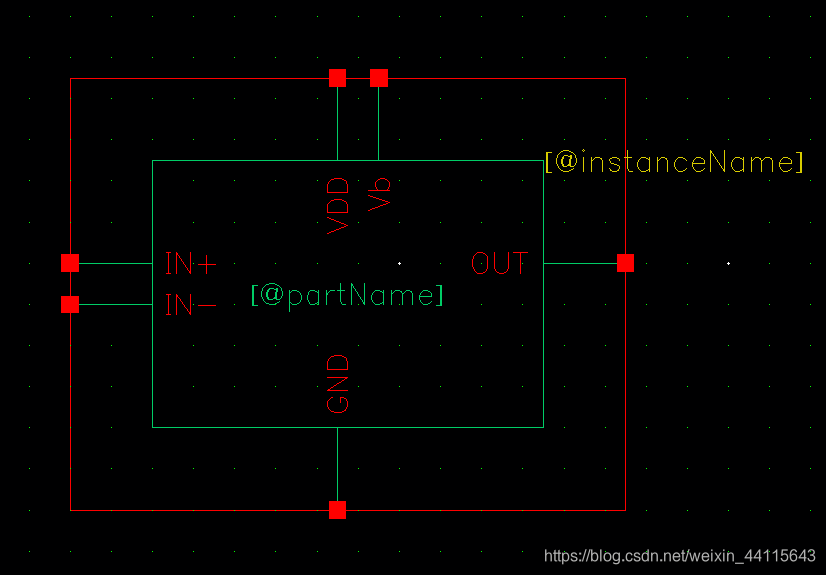

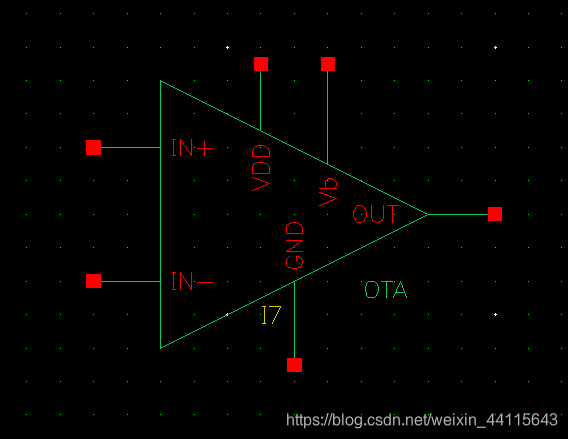

默认出来的器件有点丑,但是引脚的位置都是我们上一步设置过的。

可以自己改一下器件的线条,能好看点(可选)。

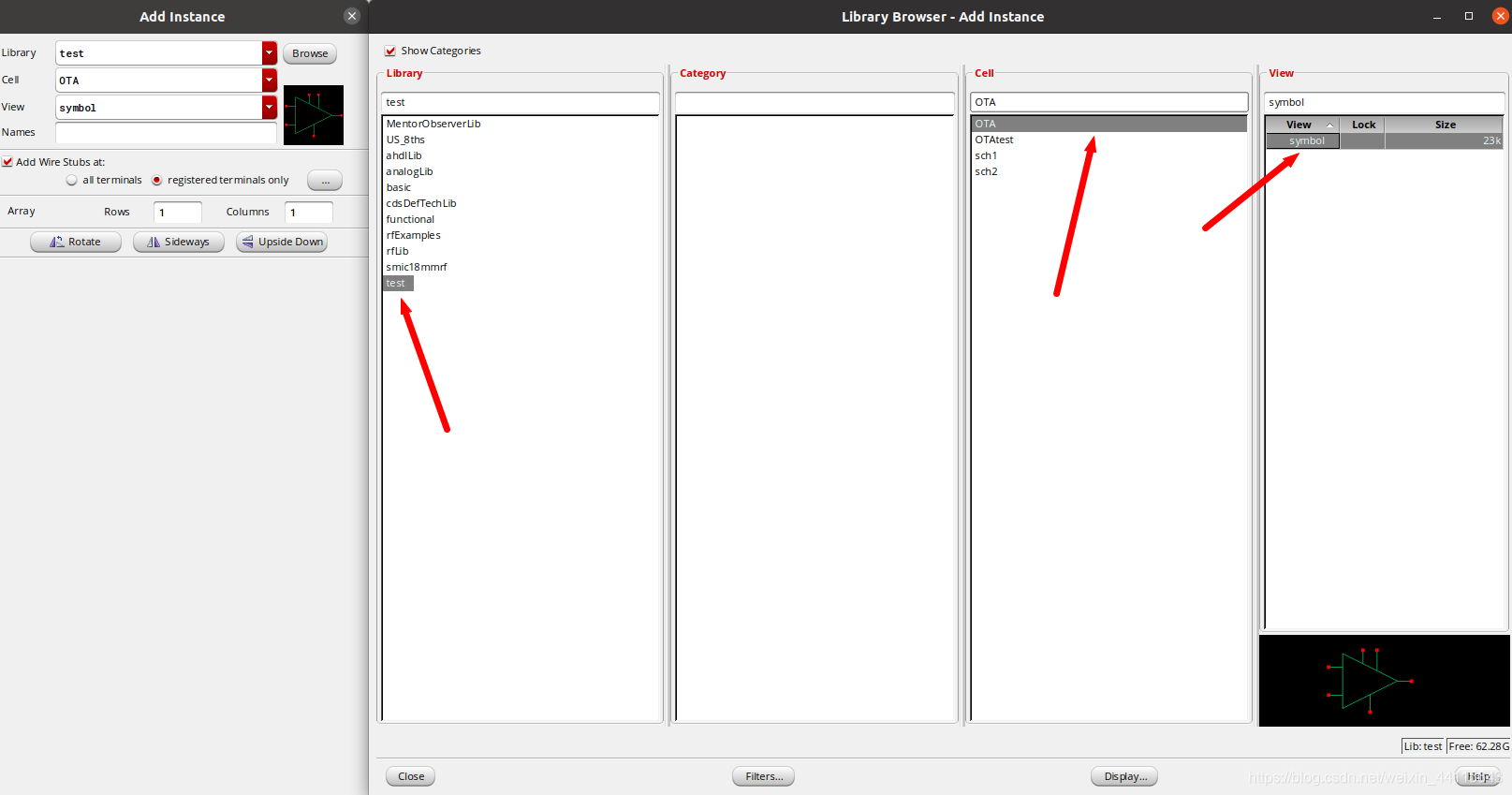

把原理图和器件图都保存后,可以在库管理菜单中看到,这个OTA器件,不仅有常见的原理图,还多了个器件选项。

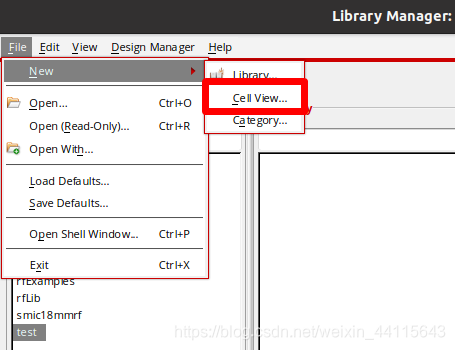

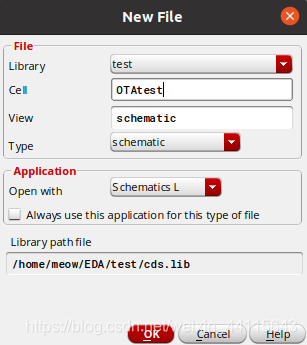

绘制测试用原理图

新建一个原理图,用于测试。

命名为OTAtest。

按照正常的插入器件的方式,选择库,选取器件。

插入到原理图中的器件。

按照原理,将电路连接好。

仿真设置

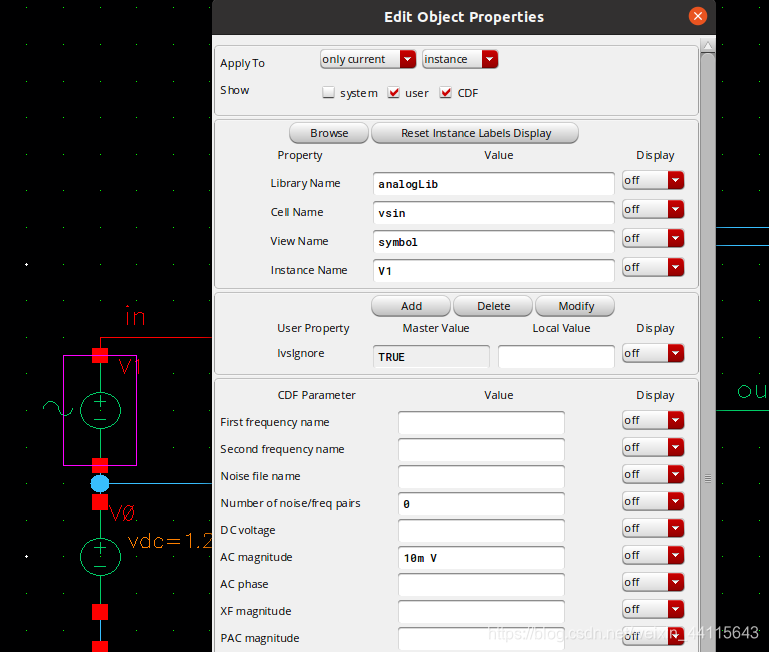

注意,vsin这个电压源,只设置AC magnitude幅值参数,不设置频率。

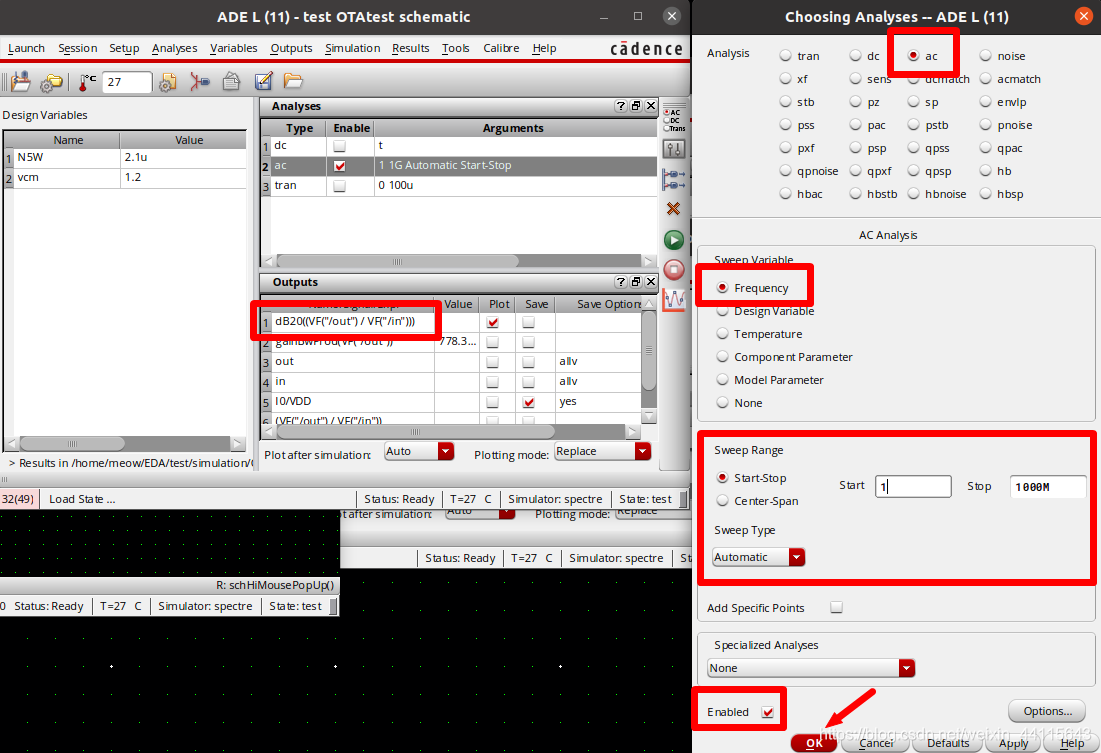

依次设置仿真类型,选择ac仿真,频率从1000到10M(这样出来的X轴为非线性,比较直观),输出点具体设置比较简单,略过。输出dB20参数的那个代码如下记录。

dB20((VF("/out") / VF("/in")))

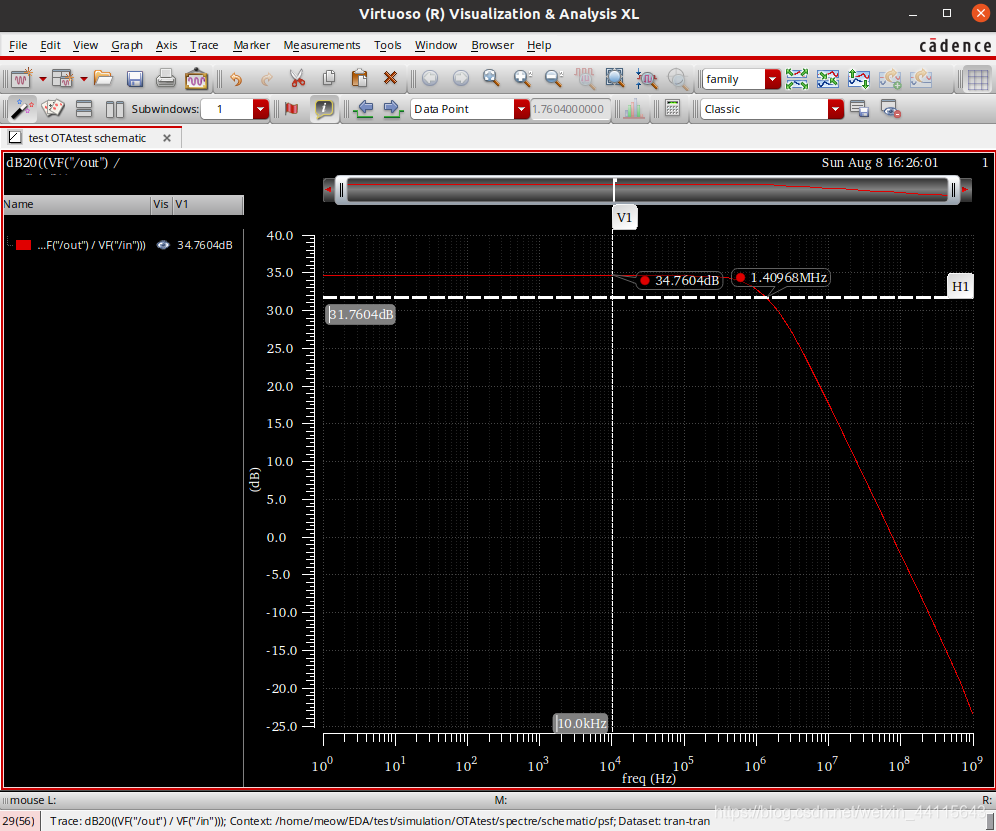

测试结果

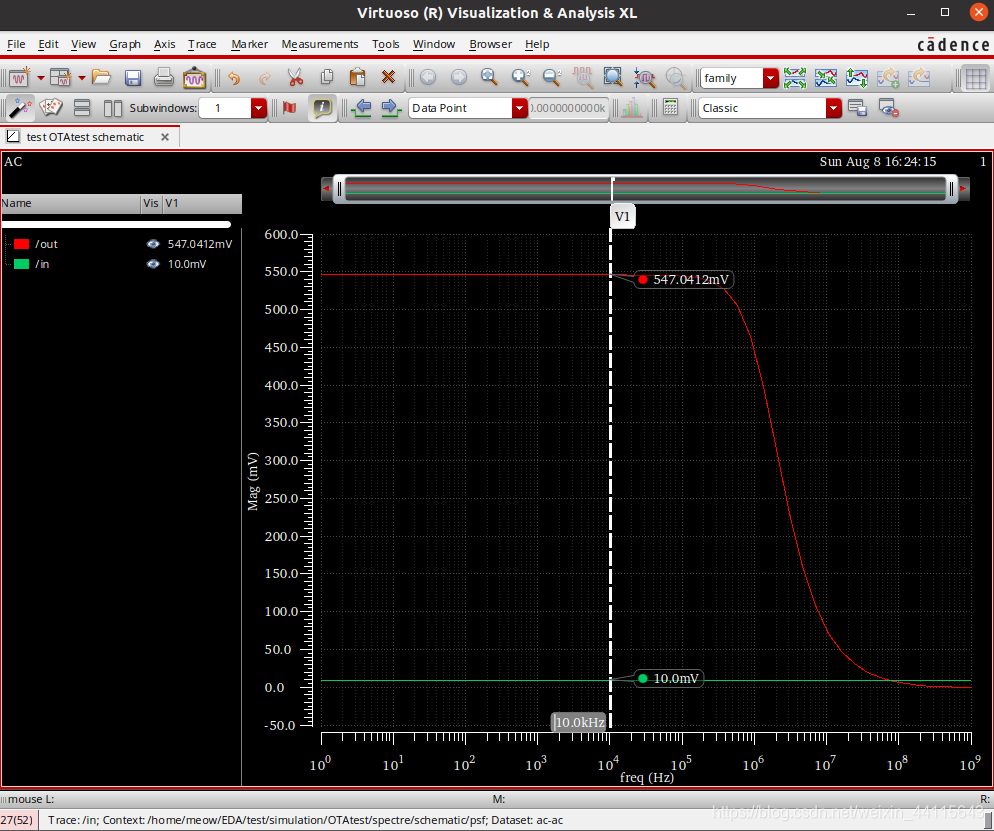

点绿色图标开始仿真,出来仿真结果。添加一个vout=10mv的marker标记。从中得到输出大致为800mV,而输入为10mV,增益Av=87。

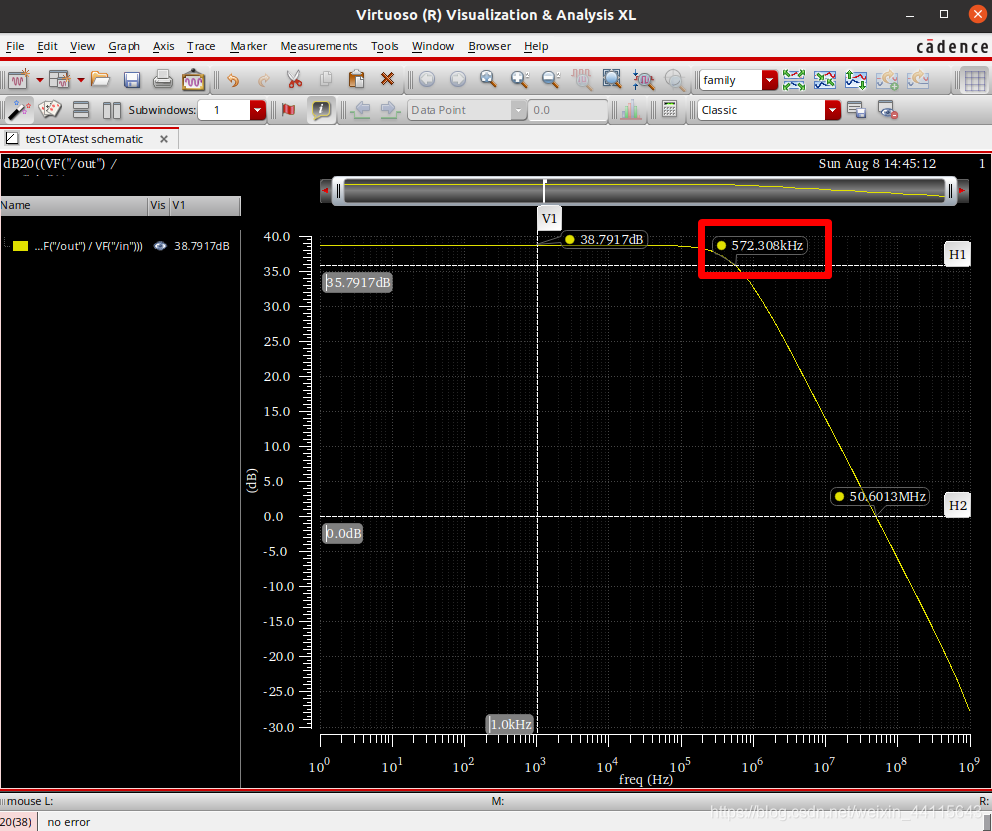

使用ac扫描,输出为以下式子,测得-3dB带宽为572KHz,未达到设计要求。

dB20((VF("/out") / VF("/in")))

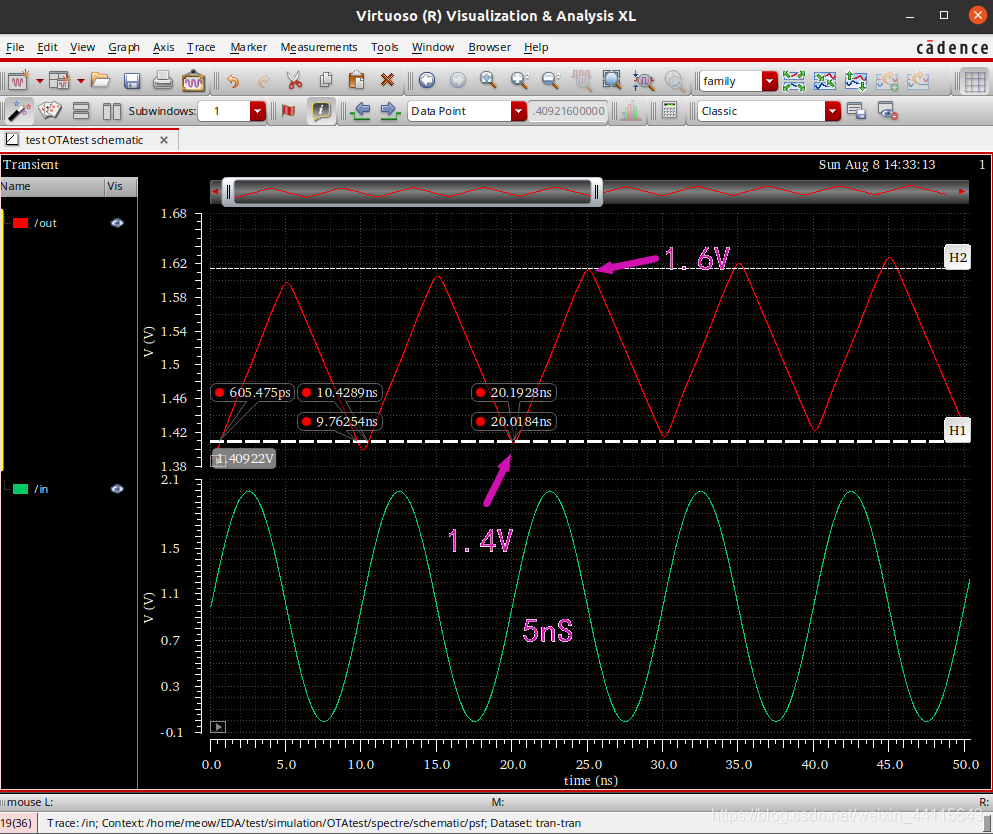

压摆率为40V/us,达到要求。此处的测试方法为,输入一个频率足够高同时幅值较大的正弦信号,然后观察输出信号即可。

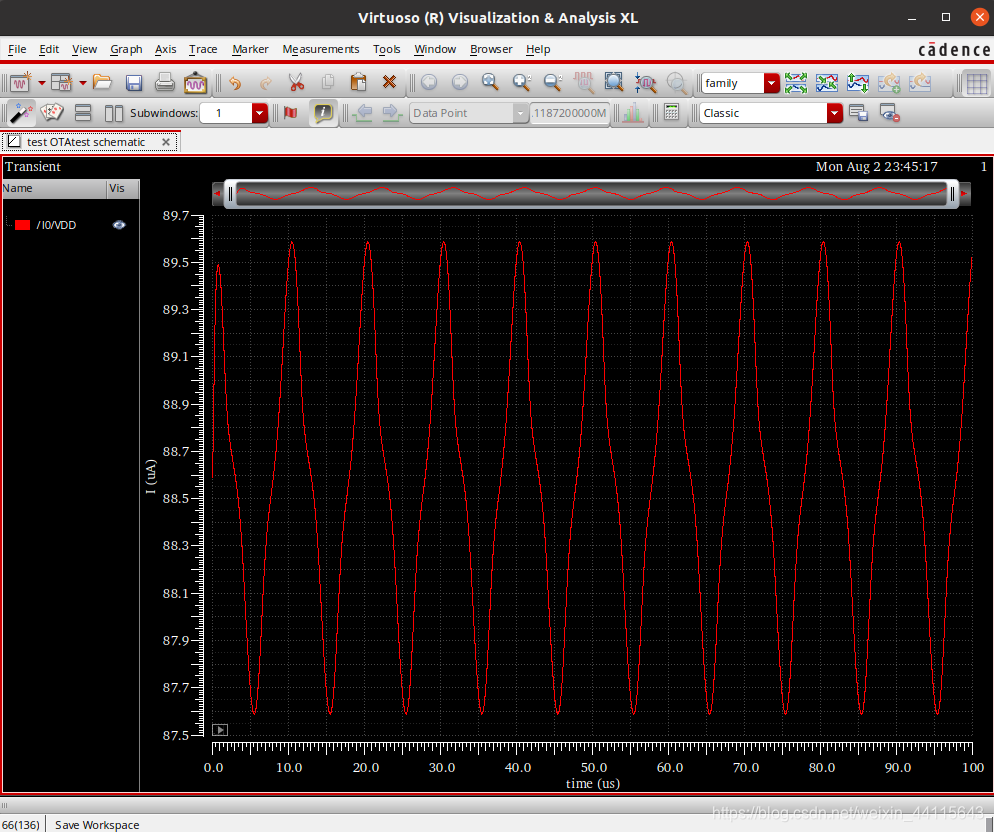

频率特性未达到要求的原因为尾电流不够,测试得尾电流大致为88.5uA。

修改后测试结果

从前面的测试中可以看出,带宽并没有达到要求。这里只对尾电流进行修改,在Vb不变的情况下,应该提高M5的W/L,但也要满足功耗需求,不能超过200uA。因为在实际设计中,这是一个有源电流镜,其W/L直接与电流在一定范围内成线性关系。

修改尾部晶体管的尺寸,将W增加至21um,再次进行仿真验证。

此时的尾电流为188.5uA,达到了前面计算的数值,增益Av=54.7。

而带宽为1.4MHz,已经达到目标值了。

总结

从上面的测试结果可以看出,能达到基本的指标,但整个设计还存在一定的问题,许多参数的偏差较大。例如,计算出M5的尺寸和对应的尾电流为180uA时,带宽仅为572KHz,而增加M5的尺寸使得尾电流达到188uA后,带宽提高至1.4MHz。总之整个设计值与实际存在较大偏差。

以上的设计也告诉了我们,通过工艺参数去设计电路是不太靠谱的,同时大部分的工艺库都不会给出衬底的参数,即un和Cox,就是计算中用到的Kn。当遇到大型工程时这些问题会变得更加复杂。所以我们需要用gm/Id来设计运放,这将在以后的文章中记录。

1465

1465

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?