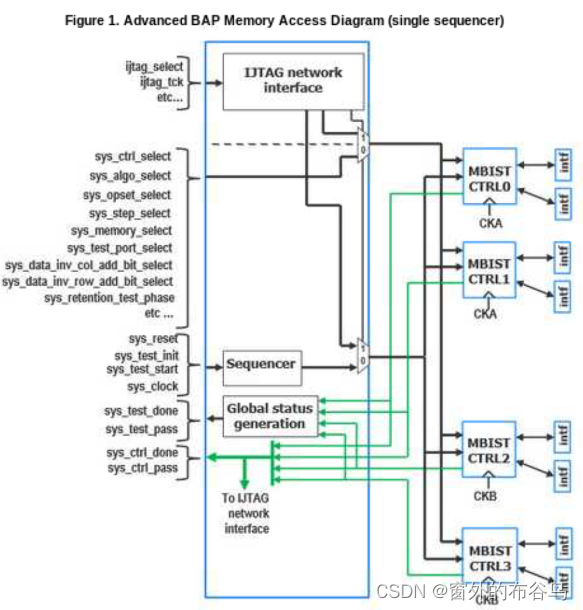

高级BAP memory访问特征由两部分组成,如图1所示。BAP直接访问接口ports的连接是用户可配置的,连到到功能逻辑上。BAP到MeroryBISTde controllers的连接是完全自动的,用户不可配置。对于MemoryBIST controllers的信号是可通过添加到BAP的IJTAG TDRs来编辑的,或者,通过BAP直接访问接口来配置。MemoryBIST 控制器的端口可以独立于BAP直接访问接口来执行,高级BAP在不串行配置控制器的情况下,为所有memory支持某些特性重写,例如算法。通常在hw_default模式下操作memoryBIST控制器,可以通过消除shift cycles来减少测试时间,从而在IJTAG协议中设置memory测试。

直接访问接口通过连接到BAP的系统信号提供调用memory tests的能力。BAP中的sequencer(序列产生器?)实施low latency protocol来启动和停止memory 测试。在该实施中,使用单个sequencer来最小化BAP的门数量。sequencer的时钟,sys_clock应该具有相对低的频率,与ijtag_tck相当,为了确保生产的控制信号能够以正确的顺序到达所有的MBIST控制器。

直接访问接口提供基本的选项来配置memory测试。可以改变应用到memories上的算法和操作集,可以基于in-system测试要求选择控制器、step和memory来执行,例如,如果分配的测试时间被限制,通过选择具有少数指令的算法或者旨在一个memory上执行memory BIST是有益的。

直接访问接口的输出端口显示所有有效控制器的全局通过/失败和完成状态(是否完成了测试)。每个控制器的执行时间通常是不同的,因为各个控制器的pass/fail和完成状态可以被监视。

每个功能时钟配置一个sequencer能够进一步减少开启和停止控制器所要求的时间,并更准确地约束从sequencer到共享功能时钟地MBIST控制器的关键路径,成本包括专用的输入/输出控制信号,以及每个功能时钟的sequencer(为每一个时钟配置sequencer,会增加sequencer以及sequencer的输入和向控制器的输出信号)。

1601

1601

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?