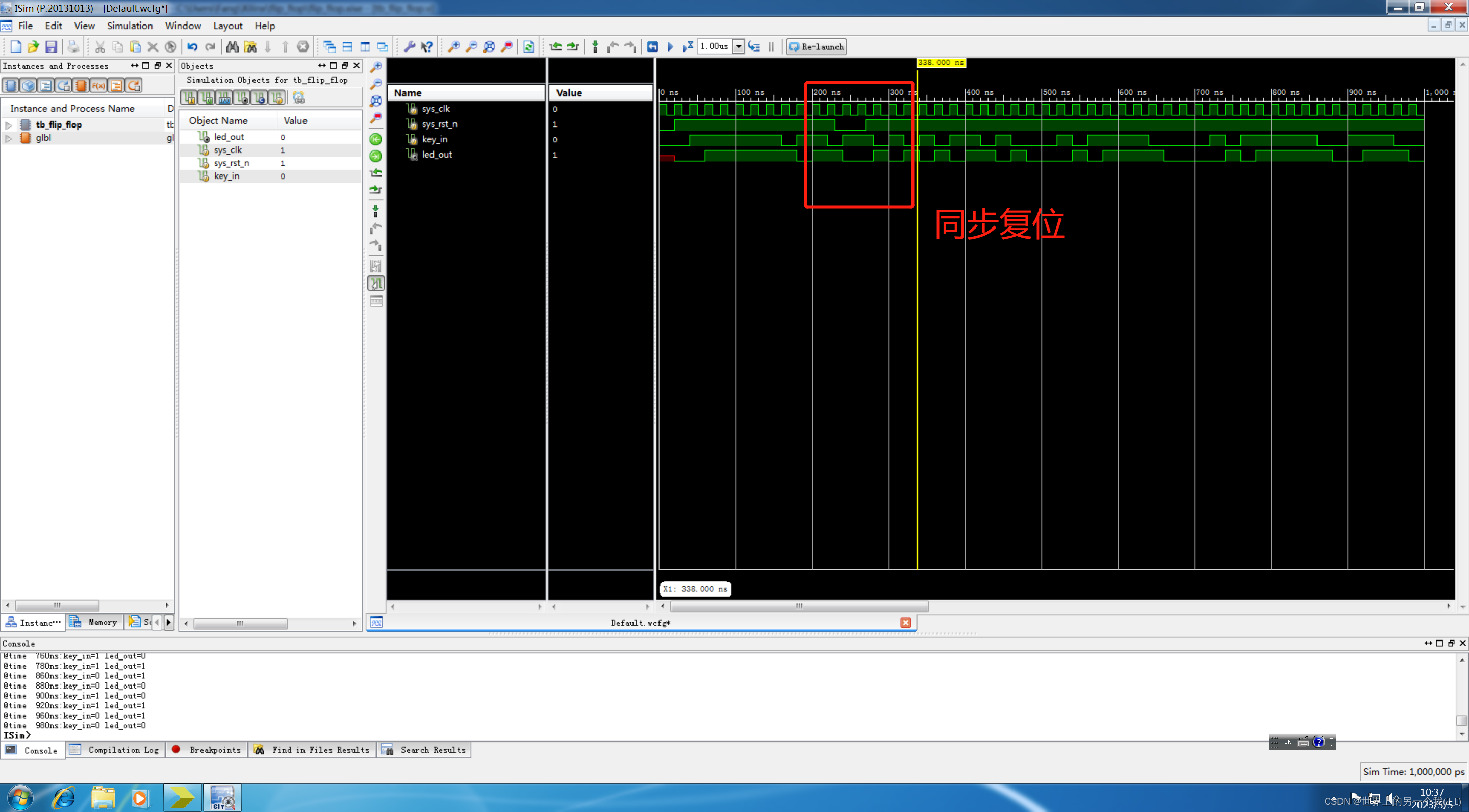

1、同步复位:只有在时钟上升沿到来时有效

同步复位代码:

always@(posedge sys_clk)

if(sys_rst_n == 0)

led_out <= 0;

else

led_out <= key_in;

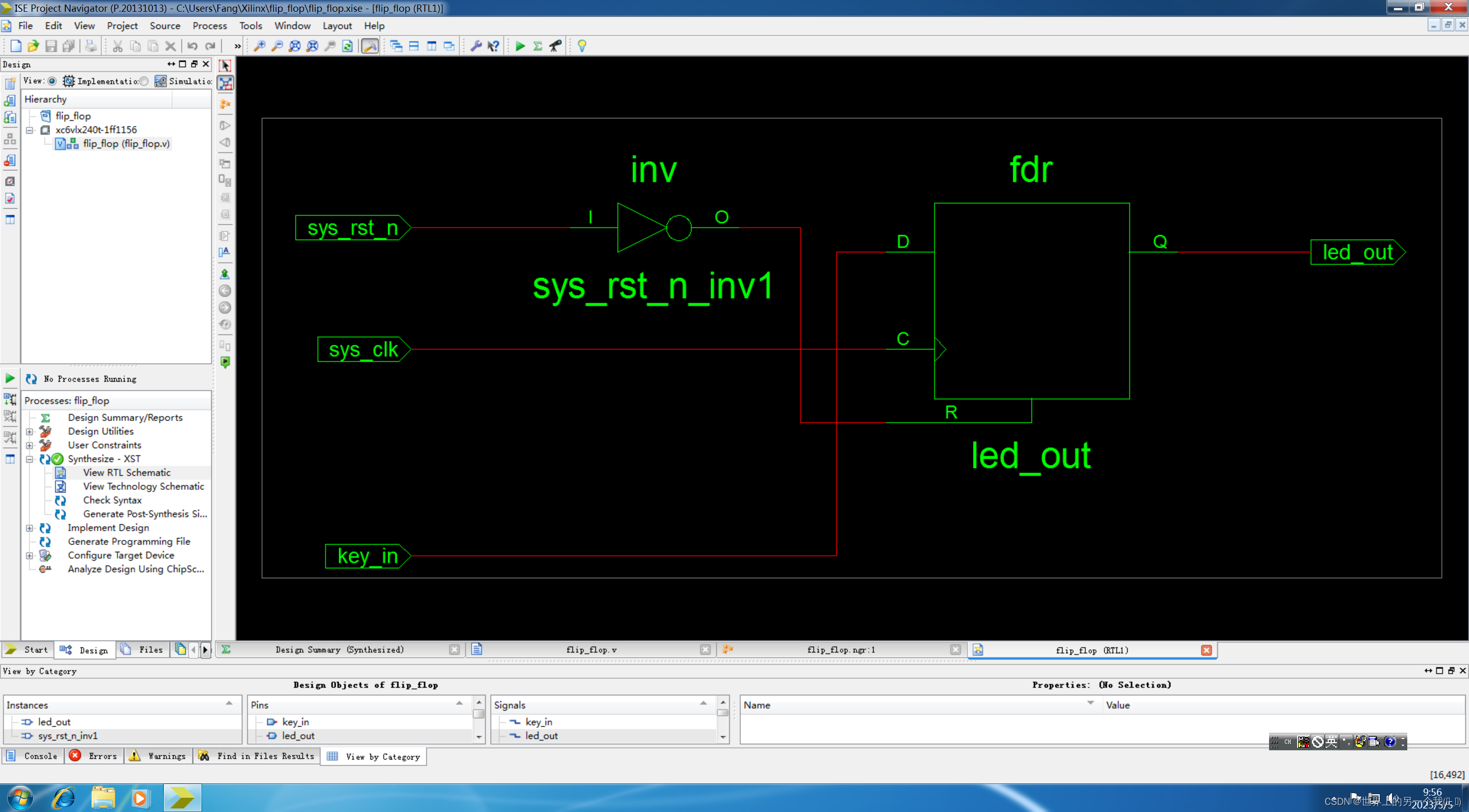

综合电路:FDR : D Flip-Flop with Synchronous Rsest同步清除D触发器。

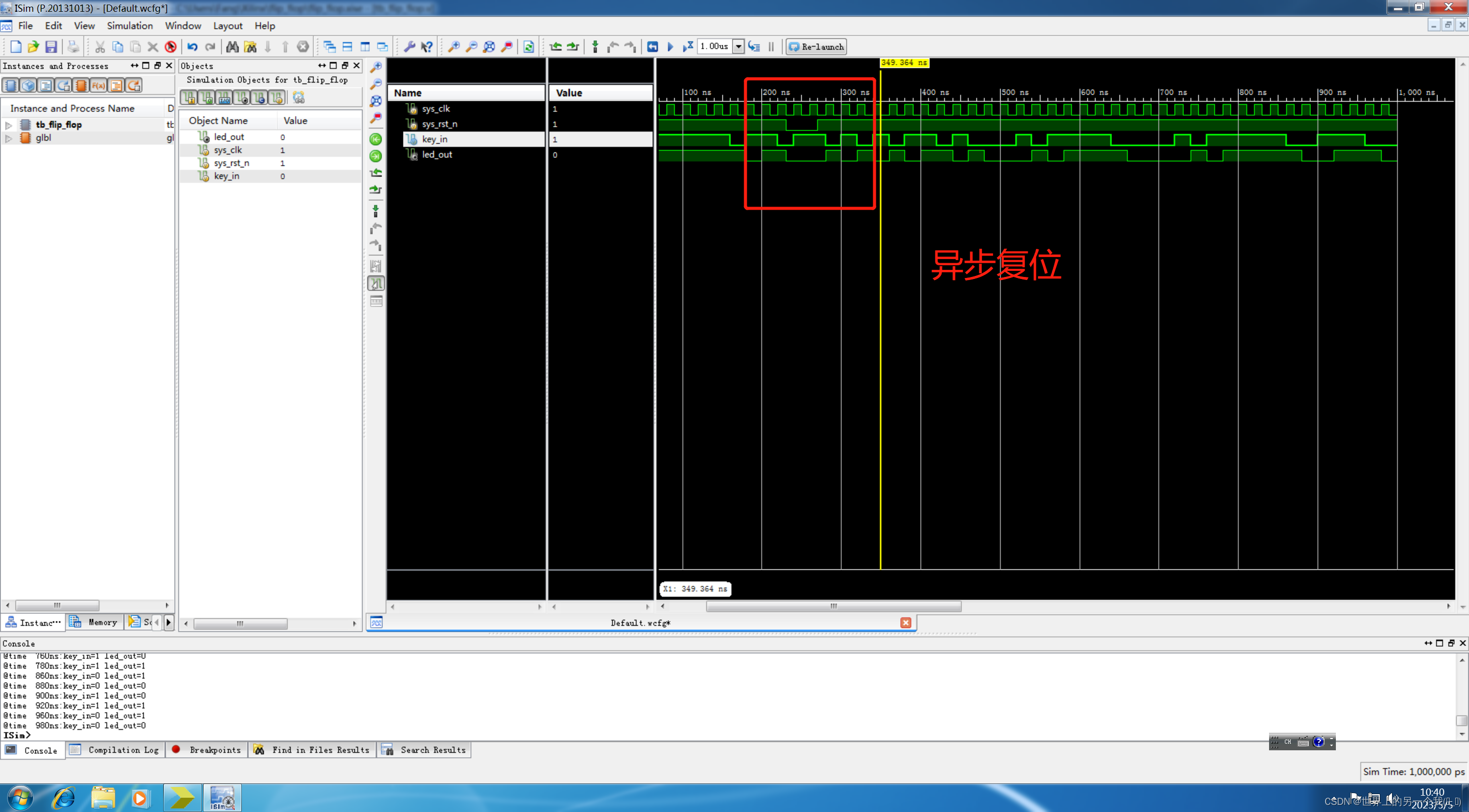

2、异步复位:只要复位信号有效,就对信号进行复位

代码:

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 0)

led_out <= 0;

else

led_out <= key_in;

综合电路:FDC : D Flip-Flop with Asynchronous Clear 带异步清除D触发器 ,与 FDR的区别是。当CLR置为高电平时,不需要等到下一个时钟的上升沿就可以复位寄存器。

3、仿真代码

`timescale 1ns / 1ns

module tb_flip_flop;

// 输入输出列表

reg sys_clk;

reg sys_rst_n;

reg key_in;

wire led_out;

//初始化

initial begin

sys_clk = 1'b1;

sys_rst_n <= 1'b0;

key_in <= 1'b0;

#20;

sys_rst_n = 1'b1;

#210;

sys_rst_n = 1'b0;

#40;

sys_rst_n = 1'b1;

end

//模拟时钟和按键输入

always #10 sys_clk = ~sys_clk; //时钟每隔10ns翻转一次,周期为20ns,频率为50Mhz

always #20 key_in <= {$random} % 2;

//实例化

flip_flop uut (

.sys_clk(sys_clk),

.sys_rst_n(sys_rst_n),

.key_in(key_in),

.led_out(led_out)

);

endmodule4、仿真波形

异步复位同步释放

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?