Synthesis

1. Synthesis工具

综合工具是将高级硬件描述语言(HDL)代码(如Verilog或VHDL)转化为等效的门级网络的工具。它们的主要作用是将抽象的设计描述转化为具体的逻辑电路,为后续的优化和布局布线提供基础。主要是Synopsys和Cadence的综合工具。

- Synopsys Design Compiler:Synopsys的Design Compiler(DC)是业界最常用的综合工具之一。它能够智能地优化设计结构、时序和功耗,并生成最小面积且高效的门级网表。

- Cadence Genus:Genus是Cadence公司开发的综合工具。它具有高度自动化和优化能力,可在最短的时间内生成最佳的门级网表。

2. DC/genus常用命令

- 查询功能

- 搜索指令:help “指令”

- 查指令用法:“指令” -help

- 看详细解释和实例: man “指令”

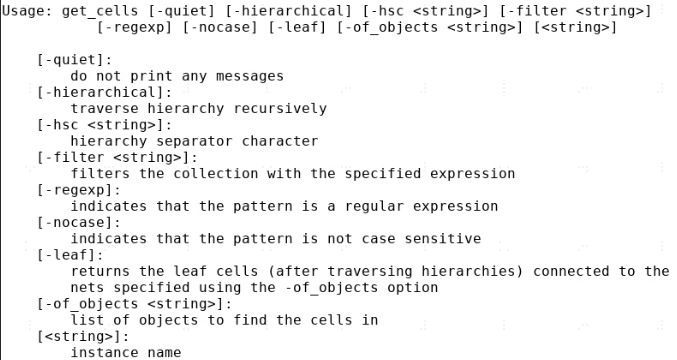

- get_cells相关

get_cells它可以报出cell信息,genus中的可选参数如下。

- 打印

- 打印全部top层的cell:

get_cells - 打印出某个层次的全部cell:

get_cells "xxxx/\*。 直接在双引号里写东西实际上是在写-filter "full_name = cordic_phase_V_U/\*" - 打出全部最底层次的cell:

get_cells -hierarchical。hierarchical的意思只是带着路径打印对象,也可以是直接打出所有最底层cell,相当于shell命中中的-r遍历。

- 打印全部top层的cell:

- -quiet:不打印任何信息

- -nocase:关闭patterns的大小写敏感

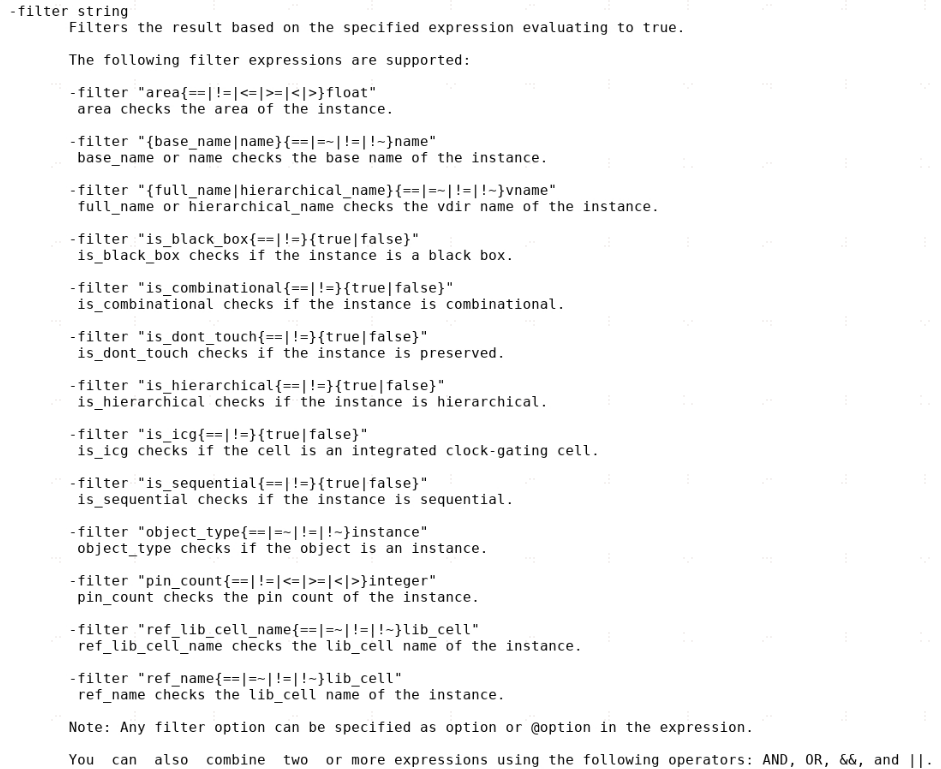

- -filter:使用属性进一步过滤。具体可以使用什么样的过滤方式方法水,是基于这个命令所属于的类(class)的,这个命令组的命名方式一般是get_$class,譬如说get_cell所对应的类(class)就是cell,所有filter可以操作的范围就是这个class里边的数据/属性,genus中的可选参数如下。

- 指的模块层级:

full_name =~ xxx/\*。条件运算符“=~”表示模糊匹配,用于匹配“xxx/”层级下的所有对象。例如,筛选名字中包含module1的对象,可以使用full_name =~ *module1\*。

- 指的模块层级:

- 使用示例:统计指的层级下所有时序单元的数量:

sizeof_collection [get_cells -hierarchical -filter "full_name =~ xxx/* && is_sequential == true"]

- 打印

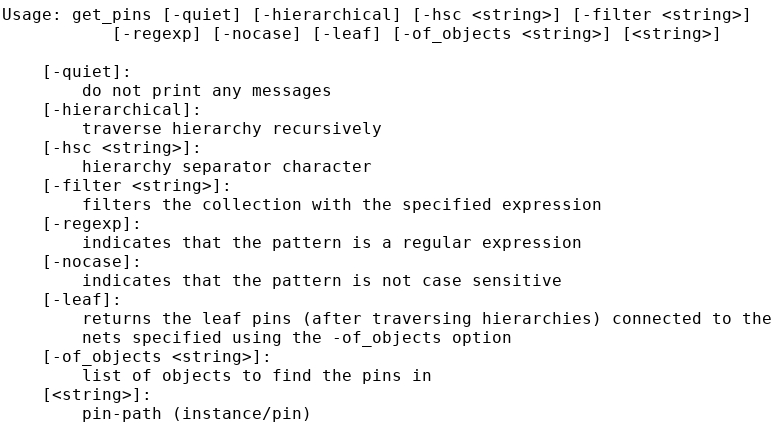

- get_pins相关

get_pins它可以报出cell信息,genus中的可选参数如下。

- 使用示例:报出指定cells的所有pin脚

get_pins -of_objects xxx/cell_name

- 使用示例:报出指定cells的所有pin脚

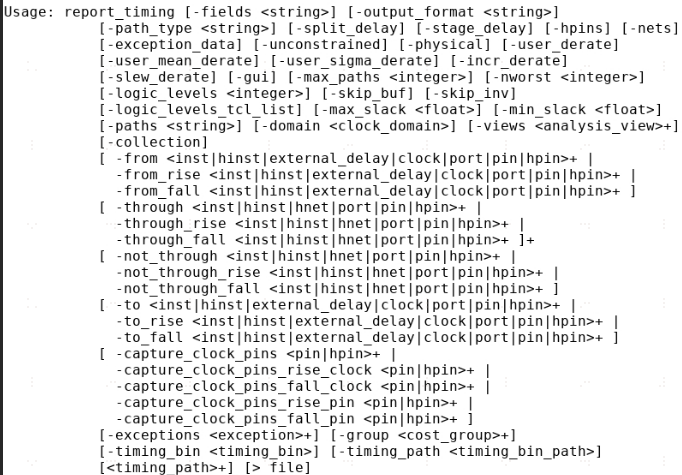

- report_timing相关

report_timing是平时分析timing时用得最多的一个命令,它可以报出一条完整path的详细timing信息,genus中的可选参数如下。

- -from:path起点

- -to:path终点

- -through:path经过的中间点

- -max_paths:报告的条目的最大条数

- -max_slack:报告的条目的最大slack

- -net:报告path中的net,提供更详细的timing path

4706

4706

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?