LTSSM L0s

L0s状态是一个低功耗活动电源管理状态,从L0s状态转换到L0状态只需要很短的时间(因为LTSSM不经过Recovery)。

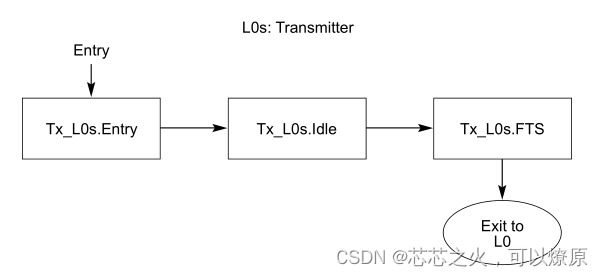

L0s Tx状态机

L0s Tx状态转换图如下所示:

Tx_L0s.Entry子状态

从L0进入

更高层控制PCIe设备进入L0s,可以通过链路上一段时间不活跃(不发送TLP、DLLP、PLP)所触发的超时机制来实现。

处于Tx_L0s.Entry

1 Tx发送EIOS,并且链路进入空闲状态。

2 Tx驱动0~3.6V的DC共模电压。

退出到Tx_L0s.Idle

50个UI(20ns)后退出到Tx_L0s.Idle,同时Tx驱动一个稳定的DC共模电压。

Tx_L0s.Idle子状态

从Tx_L0s.Entry进入

50个UI(20ns)后从Tx_L0s.Entry进入到Tx_L0s.Idle,同时Tx驱动一个稳定的DC共模电压。

处于Tx_L0s.Idle

1 链路处于电气空闲状态。

2 Tx的输出阻抗可能为低或者高。

退出到Tx_L0s.FTS

单向从Tx_L0s.Idle进入到Tx_L0s.FTS根据上层的指示(例如需要重新发包)

Tx_L0s.FTS子状态

从Tx_L0s.Idle进入

单向从Tx_L0s.Idle进入到Tx_L0s.FTS根据上层的指示(例如需要重新发包)

处于Tx_L0s.FTS

Tx开始发送FTS去重新训练对端的Rx,FTS的数量是由进入L0的时候对端发送过来的最后的TS里面的N_FTS数值决定的。(SPEC中规定如果在这个过程当中,Rx出现了timeout,可能可以选择在Recovery的时候增加N_FTS的数值来解决)如果Extended Synch bit设置,这个时候Tx必须发送4096个FTS而不是N_FTS个。

注:对于所有的速率,Tx在发送FTS之前,不能发送任何的SOS。对于5.0GT/s的速率,Tx在发送FTS之前,必须发送4~8个EIE symbols;对于128b/130b,Tx在发送FTS之前,必须发送一个EIEOS。

退出到L0

Tx一旦发送完了所有的FTSs,就会退出到L0。对于8b/10b编码方式,在所有配置的lanes上,Tx会在发完所有的FTS之后,发送一个SOS。对于128b/130b的编码方式,Tx会在发完所有的FTS之后,发送一个EIEOS,同时这个EIEOS后面会跟着SDS和数据流。

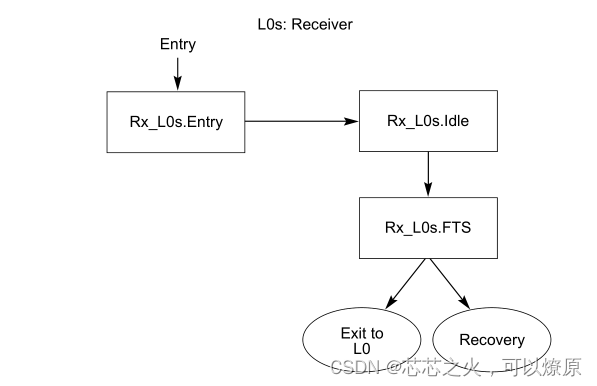

L0s Rx状态机

L0s Rx状态转换图如下所示:

Rx_L0s.Entry子状态

从L0进入

当Rx收到一个EIOS的时候(此时是支持L0s并且没有进入L1或者L2的指示),则进入Rx_L0s.Entry。

退出到 Rx_L0s.Idle

在TX_IDLE_MIN超时(20ns)的时候,从Rx_L0s.Entry退出到Rx_L0s.Idle。

Rx_L0s.Idle子状态

从Rx_L0s.Entry进入

在TX_IDLE_MIN超时(20ns)的时候,从Rx_L0s.Entry退出到Rx_L0s.Idle。

处于Rx_L0s.Idle

Rx此时处于电气空闲状态。

退出到Rx_L0s.FTS

Rx在检测到一个EIEOS后,则从Rx_L0s.Idle退出到Rx_L0s.FTS。

Rx_L0s.FTS子状态

从Rx_L0s.Idle进入

Rx在检测到一个EIEOS后,则从Rx_L0s.Idle退出到Rx_L0s.FTS。

处于Rx_L0s.FTS

在此状态下,Rx已经接收到了一个EIEOS,之后重新根据对端Tx发送过来的FTS进行Bit Lock和Symbol或者Block Lock。

退出到L0

如果所有配置的lane的Rx在8b/10b编码方式下收到一个SOS或者在128b/130b编码方式下收到SDS,则进入L0。

注:Rx在收到SOS或者SDS之后,必须能够立刻接收有效数据,并且在离开Rx_L0s.FTS之前必须完成lane-to-lane-de-skew。

退出到Recovery

如果在此状态下,不满足上述退出到L0的条件,则在N_FTS超时之后,Tx和Rx都会进入Recovery(对于Tx而言,此时可以允许其完成正在发送的TLP或者DLLP的发送)。

注:对于N_FTS超时问题,SPEC中建议增加N_FTS的数量减少再次发生的可能性。至于具体的数量,请查阅SPEC。

参考书籍

1 PCI Express® Base Specification Revision 5.0 Version 1.0

2 PCI Express Technology Comprehensive Guide to Generations 1.x, 2.x, 3.0

151

151

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?