ATE设备是连接工程师和芯片的桥梁,现代芯片测试都是通过ATE设备来进行的。设备是ATE测试的重中之重,是衡量一个芯片测试企业的最关键指标,它决定了芯片测试能力的上限。ATE工程师需要进行设备的开发和维护,还需要对ATE进行迭代更新以适应更加丰富和深入的芯片测试需求。

目录

一、圆晶阶段 -- CP(Chip Probing)测试

二、封装阶段 -- FT(Final Test)测试

三、系统级测试 -- SLT(System Level Test)测试

四、为何需要两个阶段的测试

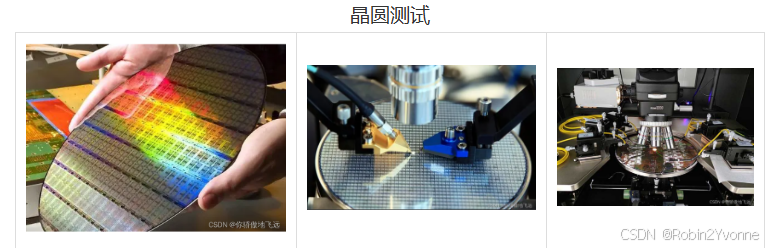

一、晶圆阶段

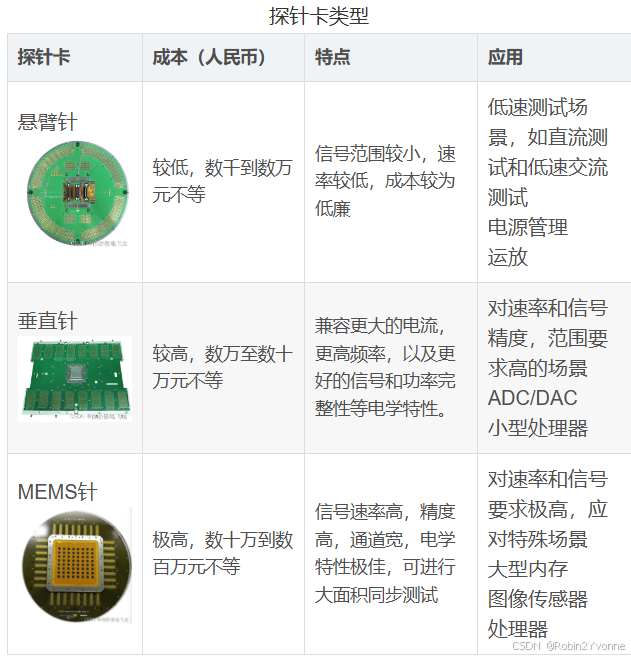

在晶圆阶段,进行的测试即为CP(Chip Probing)测试,需要用到的最重要的设备是探针卡(Probe card),它是一个多层圆形印刷电路板,上面布满了各种检测通道,用于连接晶片与测试机。探针卡需要在晶圆敲定晶片的尺寸时一同确定制作数据,如接触引脚数,引脚分布和接触面积等。按照探针的不同可以分为悬臂针(也叫环氧针,以环氧树脂固定),垂直针和MEMS针等。其中悬臂针最为通用,因其成本低廉,且参考资料丰富,有一定的标准因此相对易于定制,足以覆盖对信号要求不高的场景。

进行晶圆测试时,需要将探针卡上的触点对应到晶片上的测试引脚上。在这个过程中,针卡需要与晶圆保持绝对的平行,以确保每个触点都被接触到。因此针卡的平整性和相对晶圆的垂直调整很重要,否则在下压阶段探针可能会在晶圆上戳出一个个凹陷,通常称为弹坑,不及时调整甚至可能戳穿晶圆,导致不同的信号层被下压力叠在一起,引发开短路等故障。探针与晶圆建立良好的电气接触后测试机会读出特定的信号,此时就可以开始运行测试项了。

二、封装阶段

来到封装阶段,进行的测试是FT(Final Test)测试,通常这也是出厂前的最后一个测试。因此FT测试需要进行的测试通常会比晶圆阶段更深入,测试项覆盖更全面。该阶段需要用到的设备是分选机,分选机中负责测试的系统由一个负载板(Load Board),芯片插座(Socket),机械手(Handler)组成,工程师将芯片批量送进测试机后按顺序运行测试项。每一个测试项都会设置一个容器,在硬件上是一个盘子,机械手会将不通过该测试项的芯片放进对应的盘子里,这个盘子就称为Hard Bin;软件上是一个用于归类的标签,标示芯片的该项功能测试不通过,这个标签称为Soft Bin。可以形象地理解为一个个带有标签的盘子,装着不同测试环节出现问题的芯片,这样设置可以方便按功能项来寻找问题的根源,反馈到设计或制造端进行针对性的改进。

分选机工作的大致流程如下:

通常分选机的出货形式是卷带(装器件的带子本身叫载带),也就是我们购买元器件时最常见的形态。因为这样既方便分选机高效输出通过测试的器件,也方便自动贴片机的进料。

三、系统级测试

部分特殊的芯片需要额外进行一项测试,就是将其应用在某个完整系统里,模拟其工作环境进行测试,称为SLT(System Level Test)测试。SLT一种是在其他测试覆盖率无法满足时使用。还有一种就是为了控制成本,因为ATE的测试成本比较高。SLT的测试是把芯片放在测试板上,测试板可以用于验证芯片的各个功能。同时工程师控制多台测试机,可以实现批量测试。

四、为何需要两个阶段的测试

首先受测试治具的限制,在绝大多数情况下,特别是国内,在CP测试上选用的探针基本属于悬臂针(也有叫环氧针的,因为针是用环氧树脂固定的缘故)。

- 这种类型的针比较长,而且是悬空的,因此信号完整性控制非常困难,数据的最高传输率只有100~400Mbps,高速信号的测试几乎不可能完成。

- 而且,探针和晶圆的直接接触在电气性能上也有局限,容易产生漏电和接触电阻,这对于高精度的信号测量也会带来巨大的影响。

- 所以,通常CP测试仅仅用于基本的连接测试和低速的数字电路测试。

虽然理论上在CP阶段也可以进行高速信号和高精度信号的测试,但这往往需要采用专业的高速探针方案,如垂直针/MEMS探针等技术,这会大大增加硬件的成本。多数情况下,这在经济角度上来说是不划算,因此在CP测试阶段只能选择传输率不太高,对良率影响较大的测试项目。 于是,一些测试难度大,成本高但信号速率不高的测试项目放到FT阶段再测试。但是一些芯片的部分模组的管脚在封装之前都不会引出来,在FT阶段很难甚至无法测量,如芯片的封装是SIP之类的特殊形式。在这样的情况下,有些测试就必须在CP阶段进行,这也是在封装前还需要进行CP测试的一个重要原因。

因此,晶圆测试和封装测试的区别如下

1、因为封装本身可能影响芯片的良率和特性,所以芯片所有可测测试项目都是必须在FT阶段测试一遍的,而CP阶段则是可选。

2、CP阶段原则上只测一些基本的DC,低速数字电路的功能,以及其它一些容易测试或者必须测试的项目。凡是在FT阶段可以测试,在CP阶段难于测试的项目,能不测就尽量不测。一些类似ADC的测试,在CP阶段可以只给几个DC电平,确认ADC能够基本工作。在FT阶段再确认具体的SNR/THD等指标。

3、由于CP阶段的测试精度往往不够准确,可以适当放宽测试判断标准,只做初步筛选。精细严格的测试放到FT阶段。

4、如果封装成本不大,且芯片本身良率已经比较高。可以考虑不做CP测试,或者CP阶段只做抽样测试,监督工艺。

5、新的产品导入量产,应该先完成FT测试程序的开发核导入。在产品量产初期,FT远远比CP重要。等产品逐渐上量以后,可以再根据FT的实际情况,制定和开发CP测试。

了解了它们之间的不同,我们还可以根据测试项目的不同和重复内容等因素,在具体测试项目中进行判断和取舍了。毕竟增加一个复杂的高速或高精度模拟测试,不仅仅会增加治具的成本,还会增加测试机台的费率和延长测试时间,影响出产成果。

1756

1756

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?